Branch checkout for reduction of non-control flow commands

A control instruction and non-control technology, applied in the direction of program control design, concurrent instruction execution, address formation of the next instruction, etc., can solve problems such as speed drop and delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

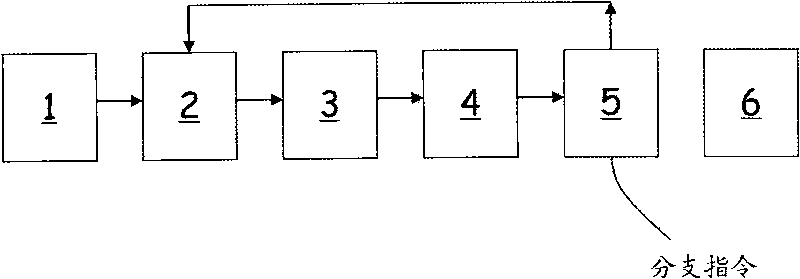

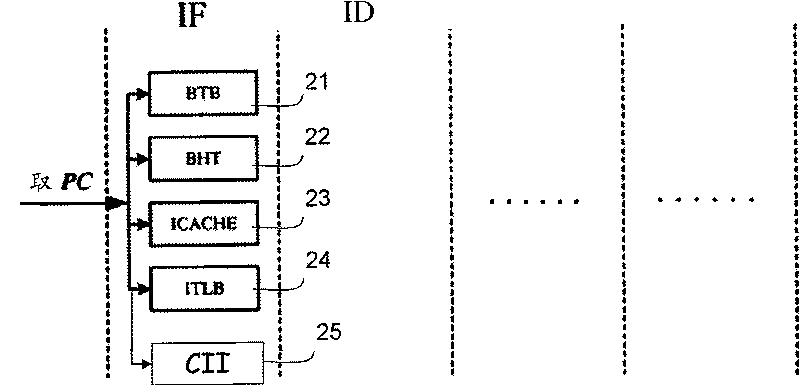

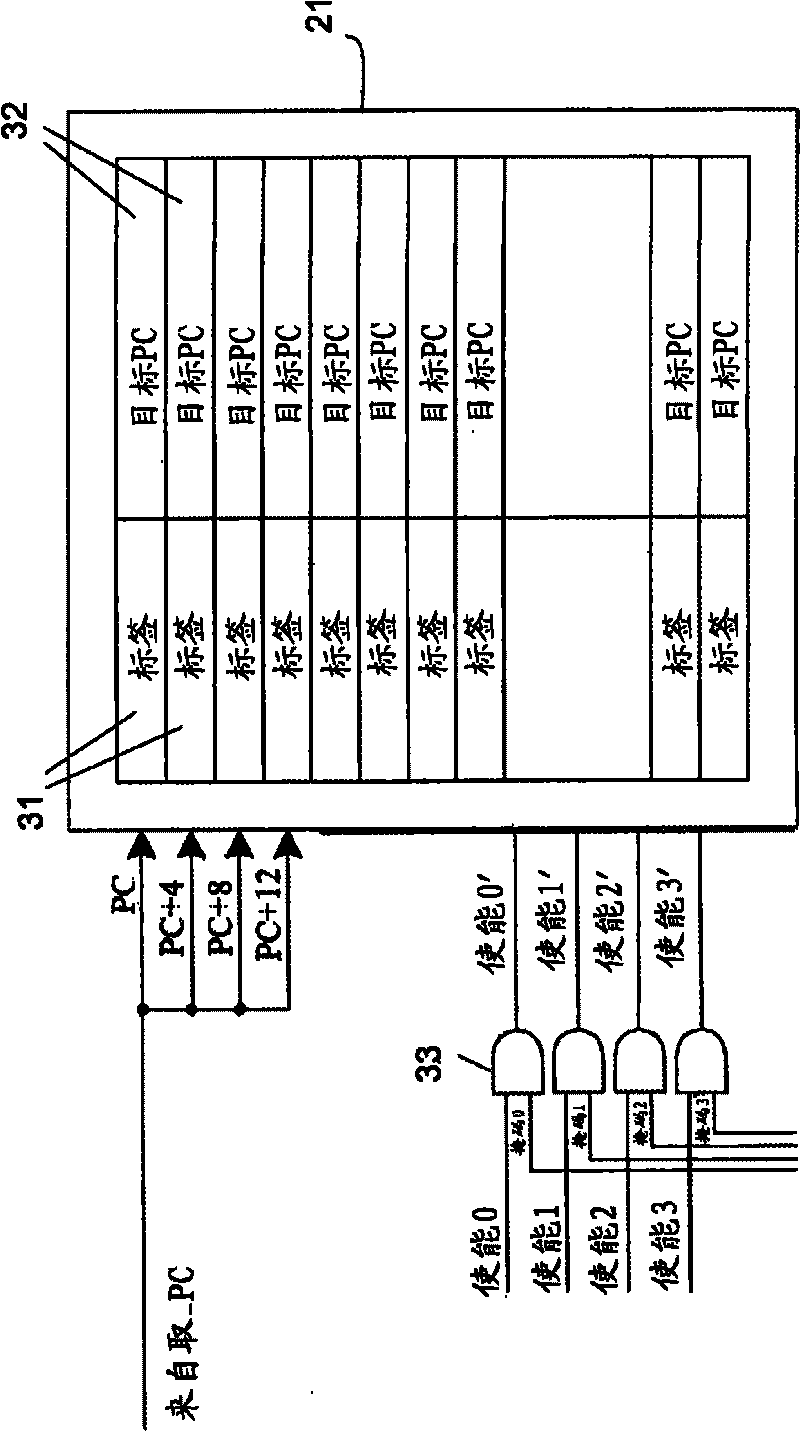

[0018] As mentioned above, branch instructions slow down the microprocessor pipeline. Some microprocessors include hardware component(s) such as branch history table (branch history table, BHT) and / or branch target buffer (branch target buffer, BTB). ), which provides branch prediction information that can be used to increase the speed of the pipeline. Some microprocessors, such as superscalar microprocessors, use branch history tables and branch target buffers to improve performance. A superscalar microprocessor is a processor that utilizes several functional units within the microprocessor core, such as the arithmetic logic unit and / or other functional units, to execute more than one instruction in one cycle. In a superscalar microprocessor, several instructions may be fetched in parallel from the instruction cache. While an instruction fetch is being performed, the BHT and / or BTB's branch prediction information for the fetched instruction may be checked concurrently. For ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More