High-speed and low-delay Berlekamp-Massey iteration decoding circuit for broadcast channel (BCH) decoder

A BCH decoder and iterative decoding technology, applied in the direction of error correction/detection using linear codes, error correction/detection using block codes, cyclic codes, etc., can solve delay increase, slow speed, low Delay and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

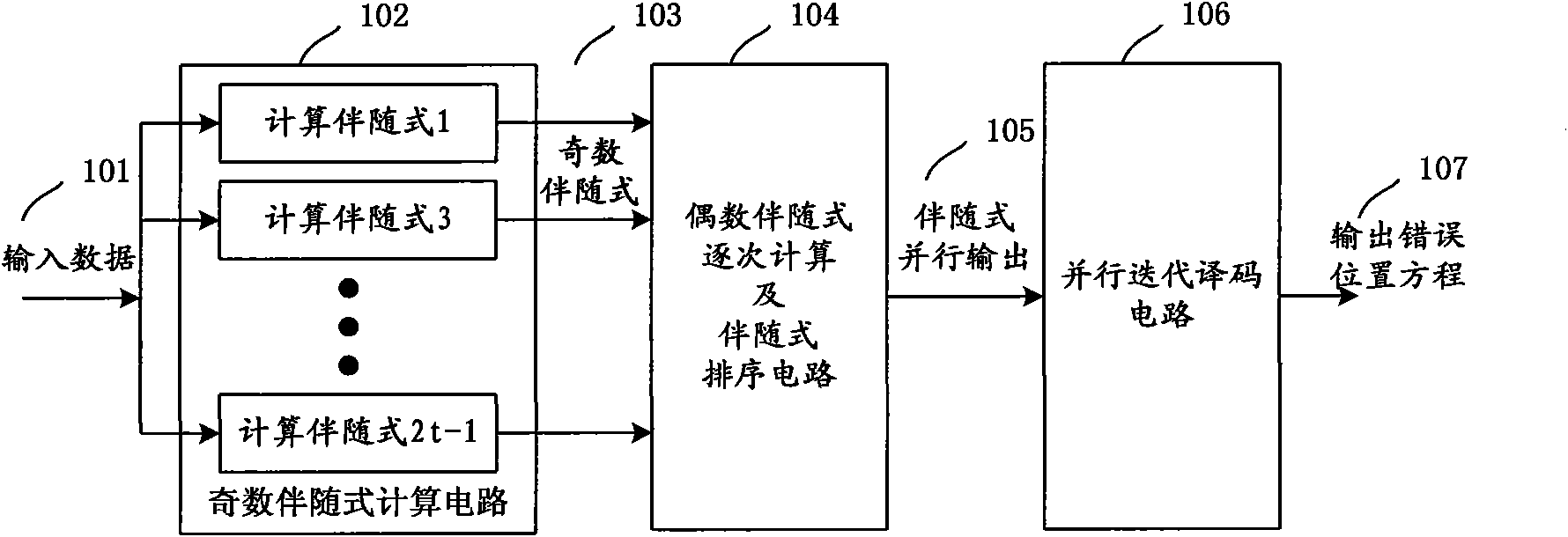

[0060] FIG. 1 is a schematic diagram showing the basic structure of the Berlekamp-Massey iterative decoding circuit of the present invention. The iterative circuit designed in the present invention mainly includes three parts, the calculation circuit 102 of the odd syndrom, the circuit 104 for successive calculation and sorting of the even syndrom, and the parallel iterative decoding circuit 106 .

[0061] When the binary BCH coded data 101 carrying multi-bit parity information is input to the iterative decoding circuit, at first the odd syndrome 103 of the BCH coded data is calculated by the odd syndrome calculation circuit 102, when there is no error bit in the data, All odd syndromes are 0, jumping out of iterative decoding. When there is an error bit in the data, the odd syndrome is not all 0, at this time, the odd syndrome is input to the even syndrome sequential calculation and syndrome sorting circuit 104, the even syndrome is obtained, and the syndrome 105 is output in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More