Multi-core processor

A processor and multi-core technology, applied in a variety of digital computer combinations, etc., can solve the problems of limited expansion capability and limited chip power consumption, and achieve the effect of easy expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

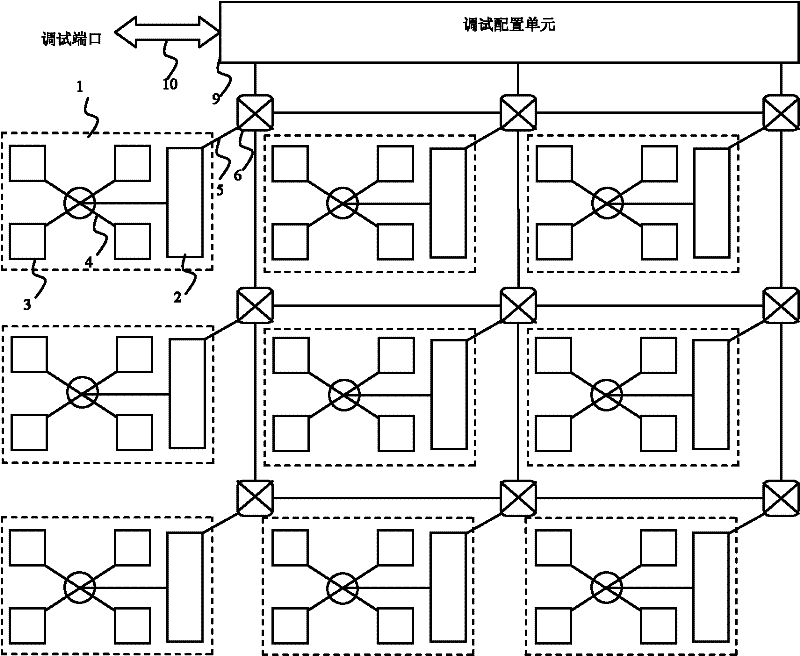

[0034] figure 1 Include a plurality of processor sets 1, and described processor set comprises a master processor 2 and several slave processors 3, master processor and slave processor and slave processor and slave processor are connected by local bus 4, The processor sets and between the processor sets and the debugging configuration unit are connected by the global bus 5 and the switching unit (SWITCH) 6, and some peripherals or hardware acceleration units may be integrated on the multi-core processor. figure 1 Not shown in , these peripherals or hardware acceleration units can also be connected to the debug configuration unit and the processor set through the global bus 5 .

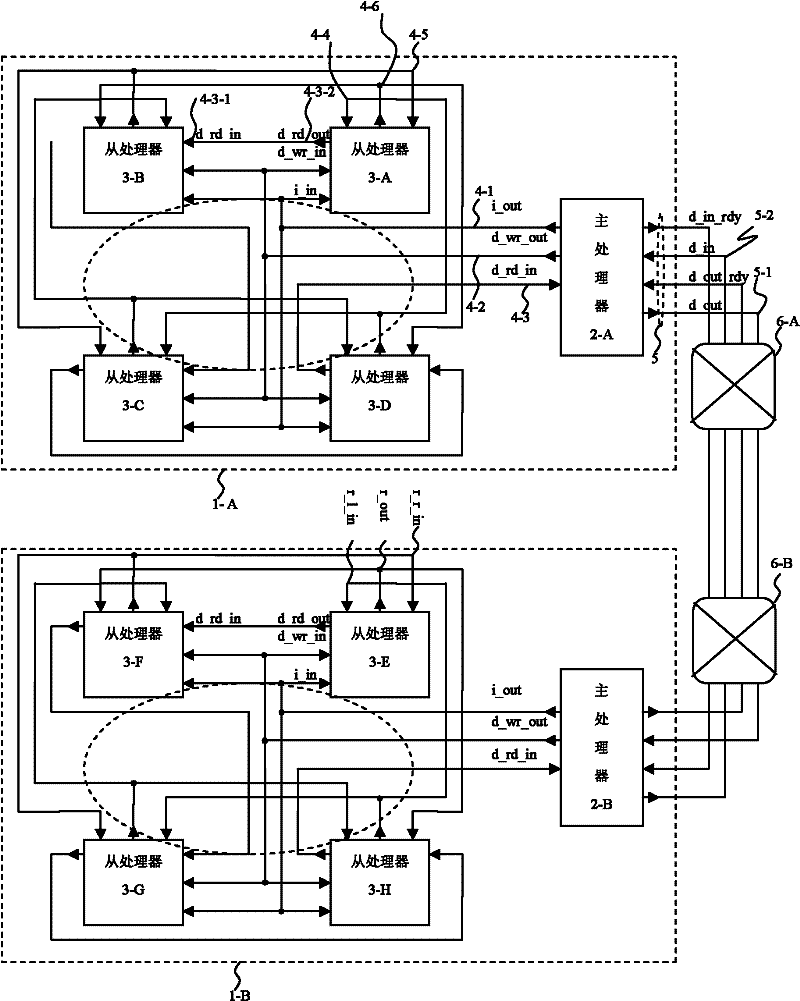

[0035] The master processor 2 controls the instructions and data carried out from the processor 3, and the slave processor may not have a program memory and an instruction fetch unit, and the master processor sends the super long instruction word to the slave processor 3 through the instruction bus in ...

Embodiment 2

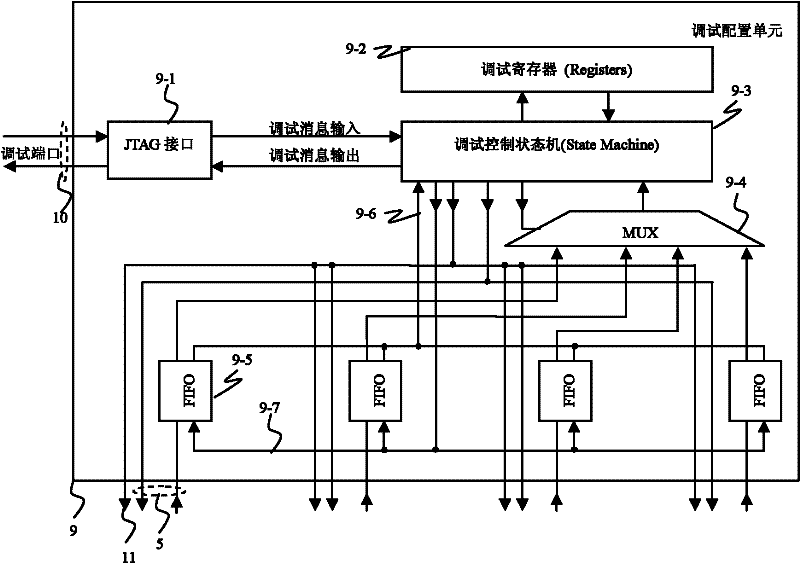

[0056] figure 1 The central global bus 5 can not only transmit multipoint-to-multipoint data communication between processor sets, but also transmit control information such as configuration, debugging, and tracking between the debugging configuration unit and the processor set. The multi-core processor system can work in two modes: debug mode and non-debug mode. Regardless of the debug mode or the non-debug mode, before the multi-core processor starts to run the code, the debug configuration unit 9 is responsible for configuring the program memory of the main processor in all processor sets on the entire multi-core processor, that is, the The code executed in is loaded into the program memory of the host processor. At the same time, debugging the configuration unit may also need to initialize the register files, data memory or other special registers of the master processor and the slave processor in the processor set.

[0057] After a power-on reset, the multi-core process...

Embodiment 3

[0071] according to figure 2 The bus configuration shown in includes global bus 5, global bus switching unit 6 and local bus 4. All slave processors 3-A, ..., 3-D in a processor set 1-A jointly complete SIMD or MIMD tasks under the control and coordination of the master processor 2-A , and different sets of processors can handle different tasks. In order to increase the processing capability of the multi-core processor, or to increase the number of slave processors in each processor set, the number of processor sets may also be increased. The increase in the number of slave processors in the processor set does not change the structure of the bus and the bus input and output ports of the master processor and the slave processor. Increasing the number of processor sets does not change the structure of the global bus and the global bus switching unit, so the processor capability of the multi-core processor of the present invention is easy to expand.

[0072] If you want to fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More