Patents

Literature

30results about How to "Save bus resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

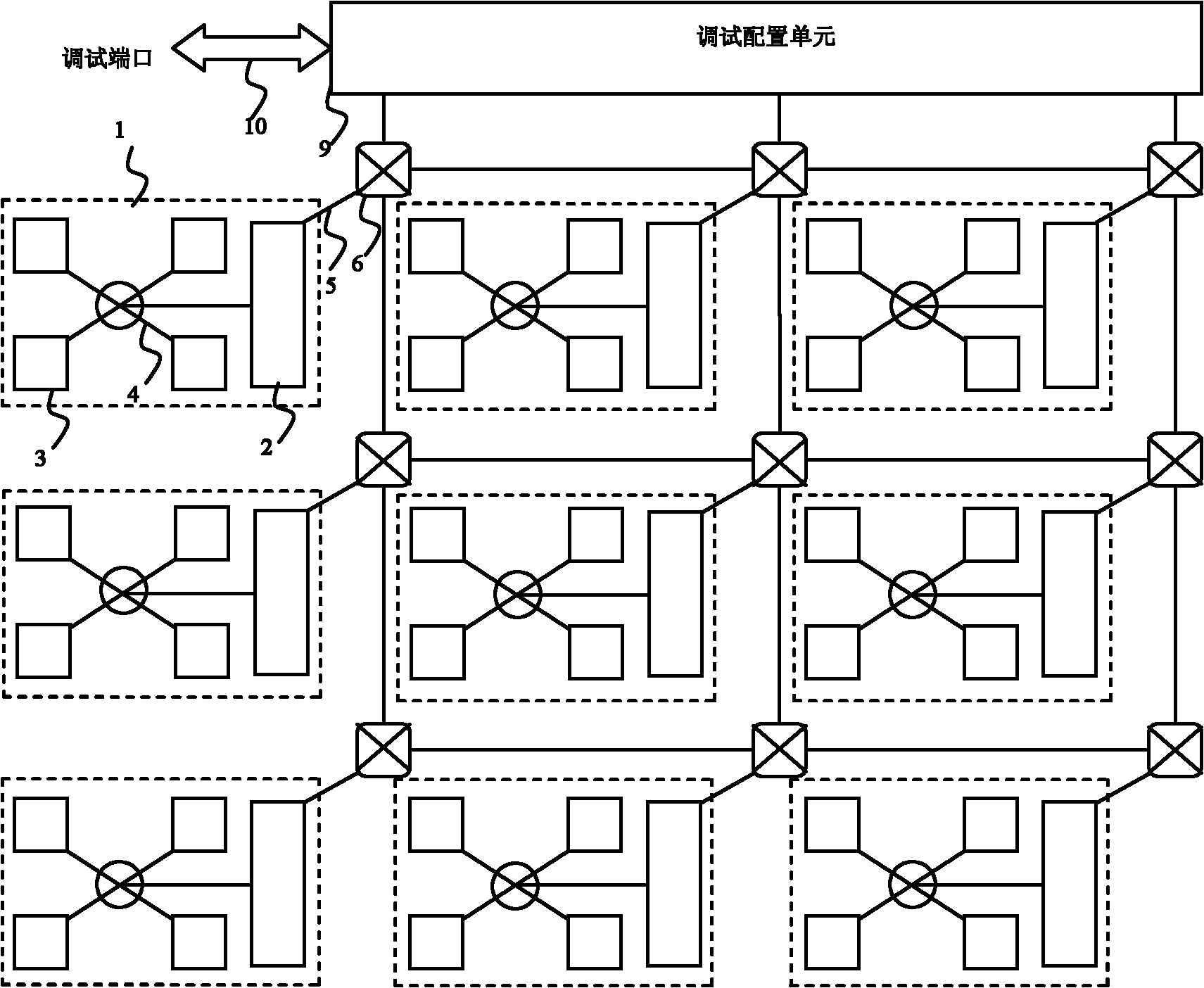

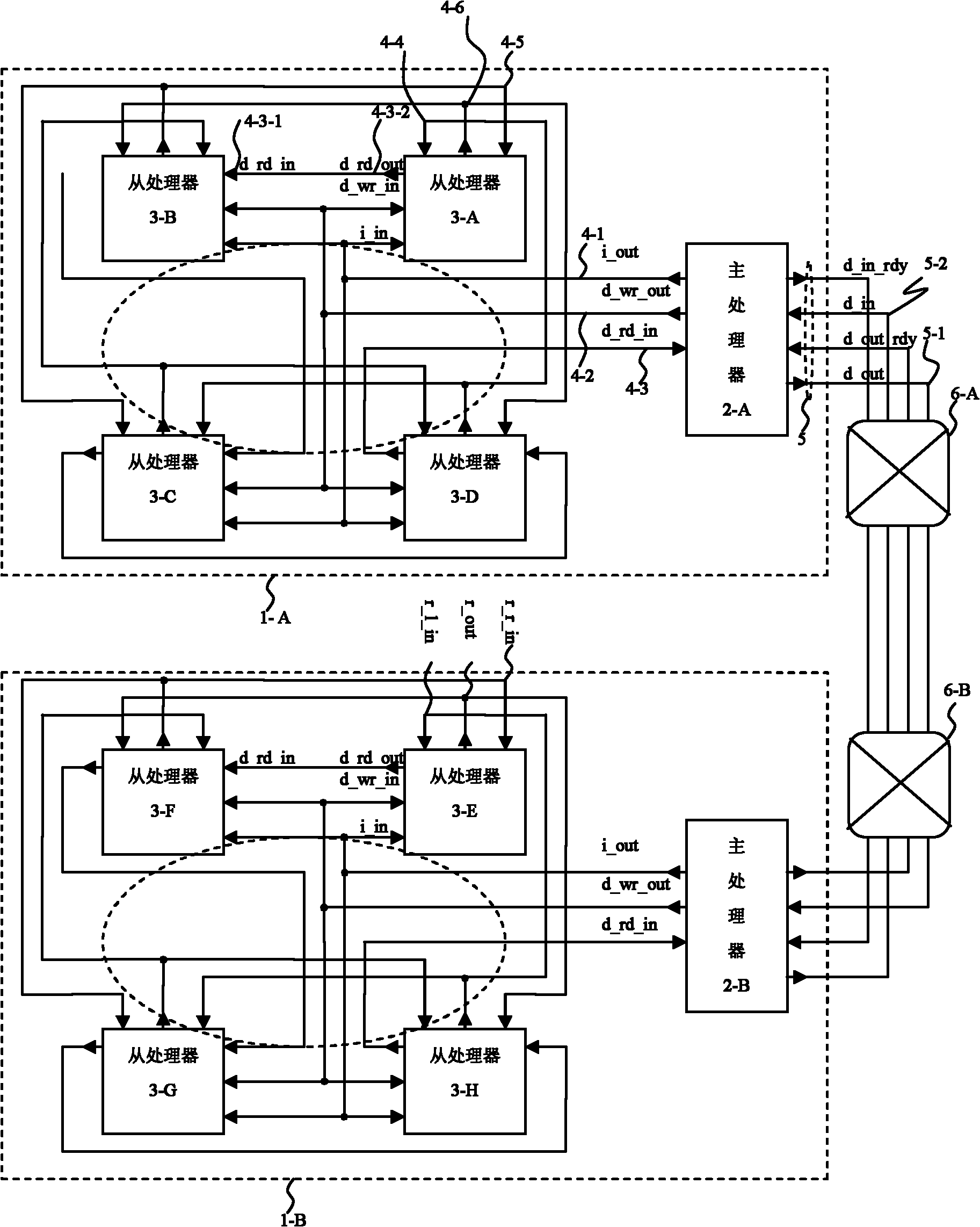

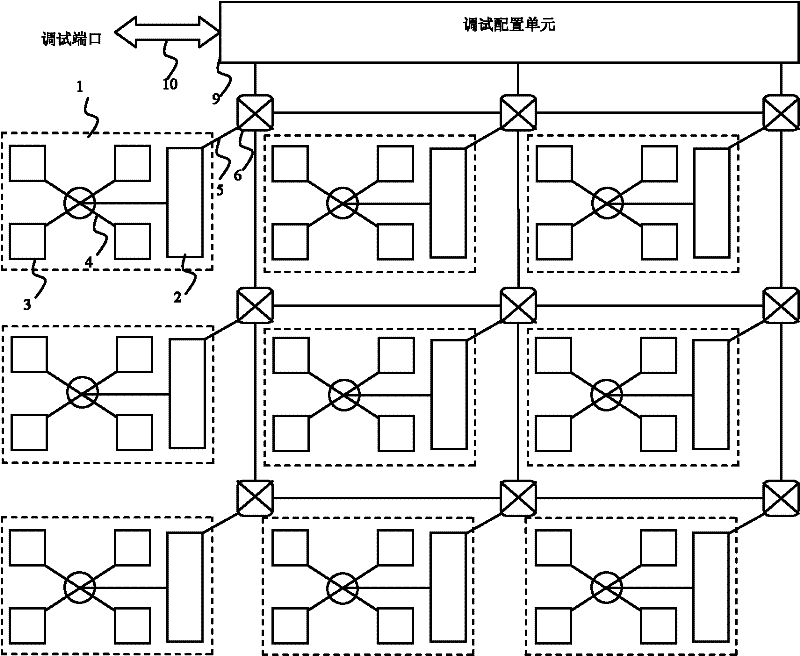

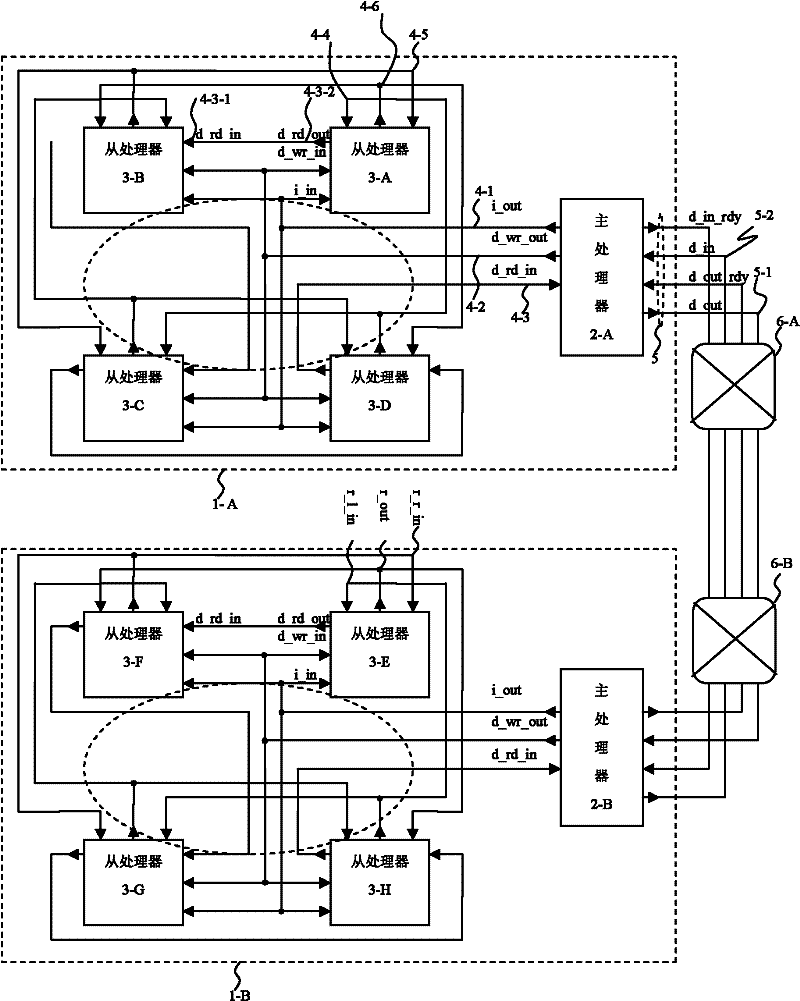

Multi-core processor

InactiveCN101882127AIt is not easy to change the numberImprove scalabilityMultiple digital computer combinationsMaster processorMulti-core processor

Owner:HUNAN UNIV

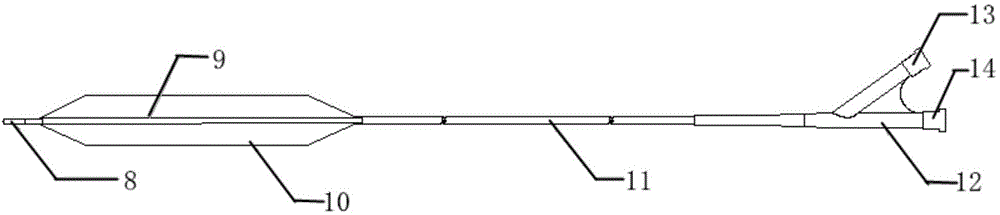

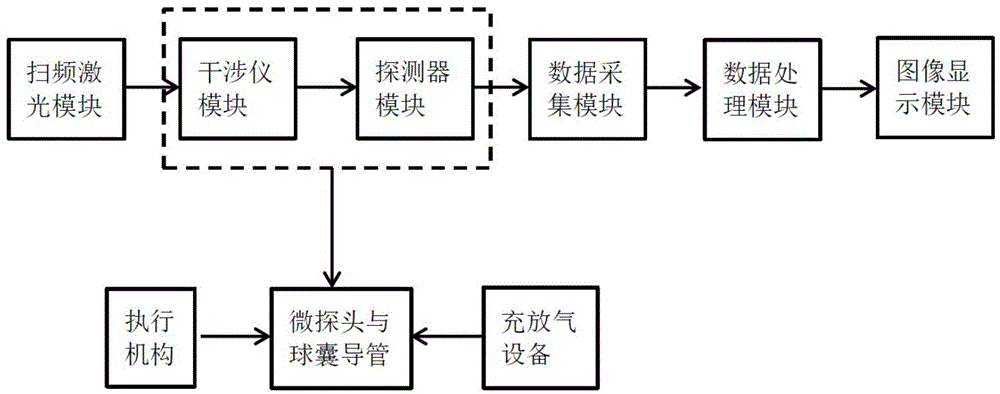

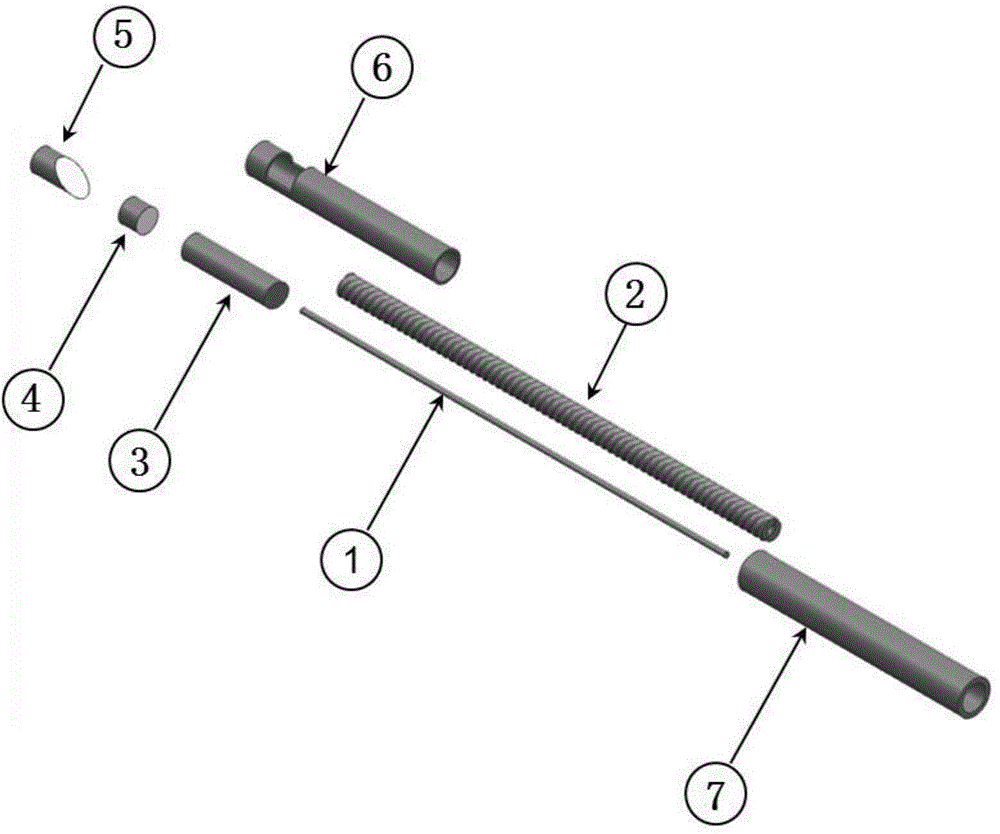

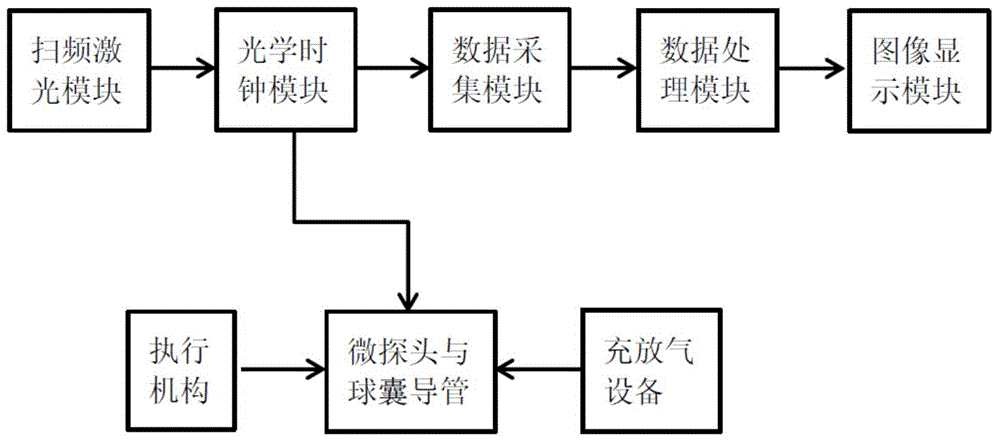

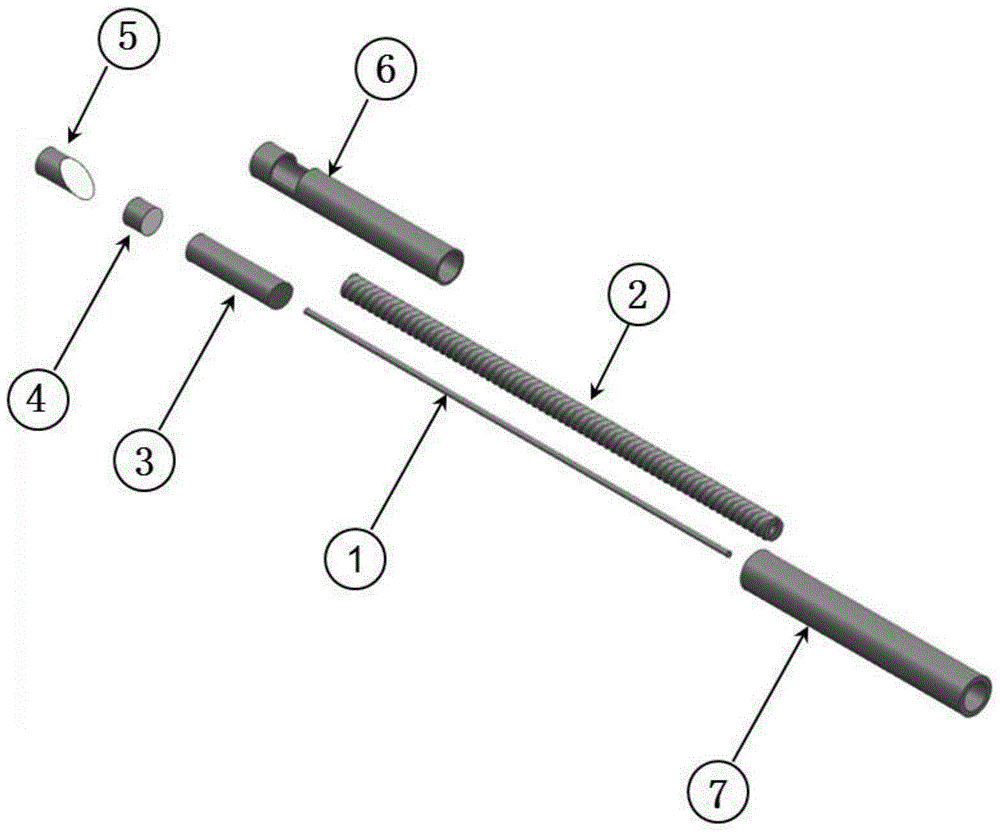

Balloon catheter applied to OCT (optical coherence tomography) endoscopic scanning imaging, use method and OCT imaging system

ActiveCN104825118AWill not affect the scan judgmentAvoid enteringSurgeryEndoscopesAtmospheric pressureBalloon catheter

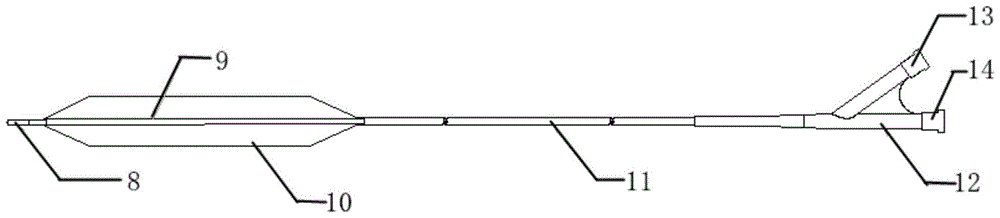

The invention relates to the technical field of medical instruments, and provides a balloon catheter which is matched with an endoscope and an OCT (optical coherence tomography) optical detector for use, an OCT imaging system, and a use method. The balloon catheter comprises a handle, a dual-cavity pipe, a balloon, an inner pipe, a soft head and the like; the use pressure of the balloon catheter is 3 separate atmospheric pressure; damage to a normal gullet is not caused under lower pressure, at the same time concentricity of the inner pipe and the balloon is ensured and optic imaging is facilitated.

Owner:MICRO TECH (NANJING) CO LTD

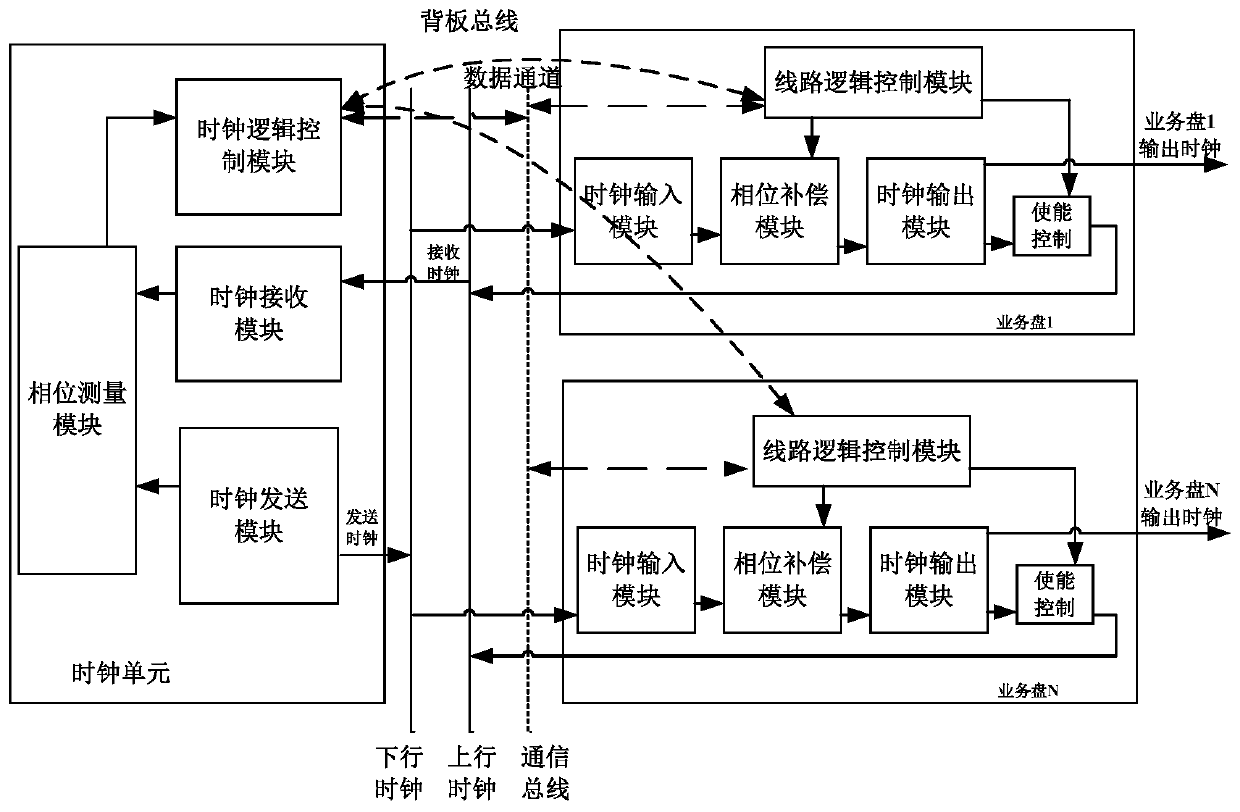

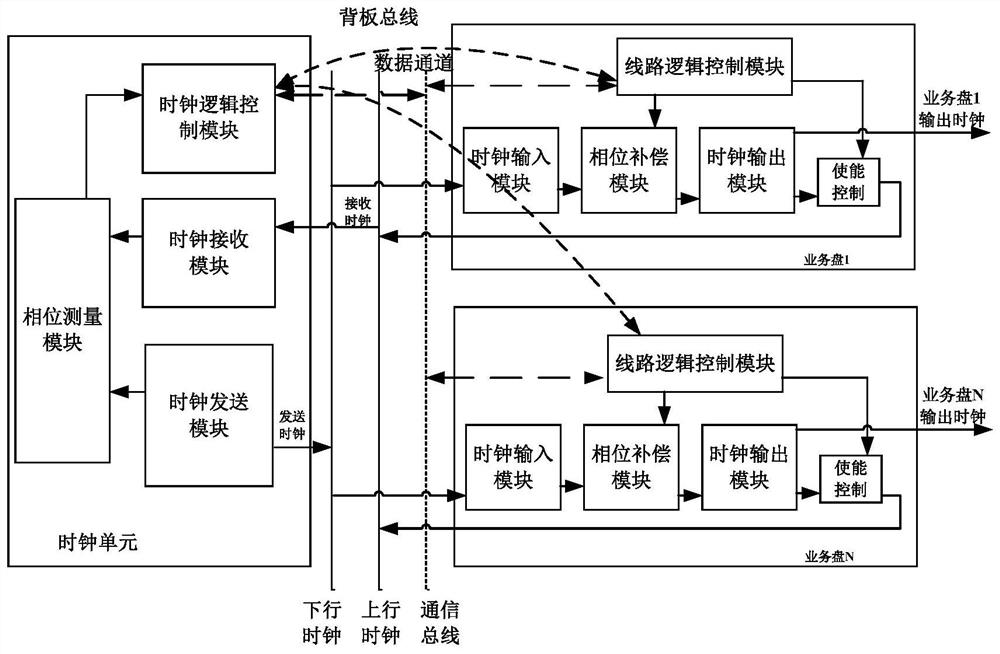

High-precision clock synchronization method and system for communication equipment

ActiveCN109818701AImprove Clock Synchronization AccuracySimple logicSynchronisation arrangementTime-division multiplexPhase compensationVIT signals

The invention discloses a high-precision clock synchronization method and system for communication equipment, and relates to the field of clock synchronization. The method comprises the following steps: a clock unit of communication equipment issues a transmission delay value to a service disk, and the transmission delay value is obtained according to a clock sending signal issued to the service disk by the clock unit and a clock phase difference of a clock signal uploaded to the clock unit by the service disk; And the service disk performs phase compensation on the clock sending signal according to the transmission delay value to form a clock signal which is basically consistent with the clock phase of the clock sending signal. According to the invention, after the clock signal is subjected to phase compensation by receiving the transmission time delay value, the compensated clock signal can be aligned with the output phase of the clock sending signal, so that the influence caused bythe transmission time delay of the clock signal in the prior art is eliminated, and the clock synchronization precision is greatly improved.

Owner:FENGHUO COMM SCI & TECH CO LTD

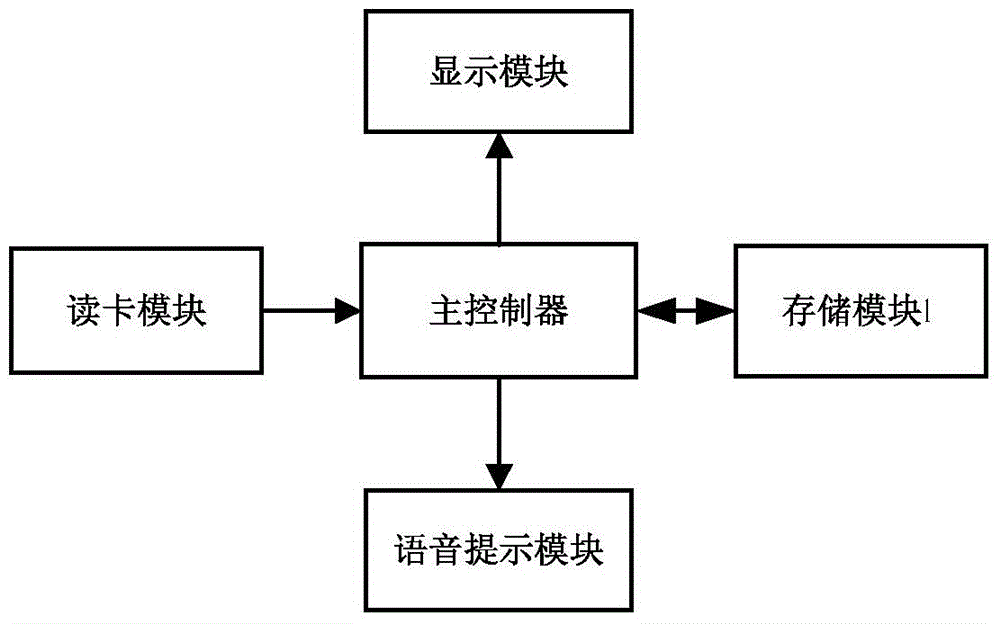

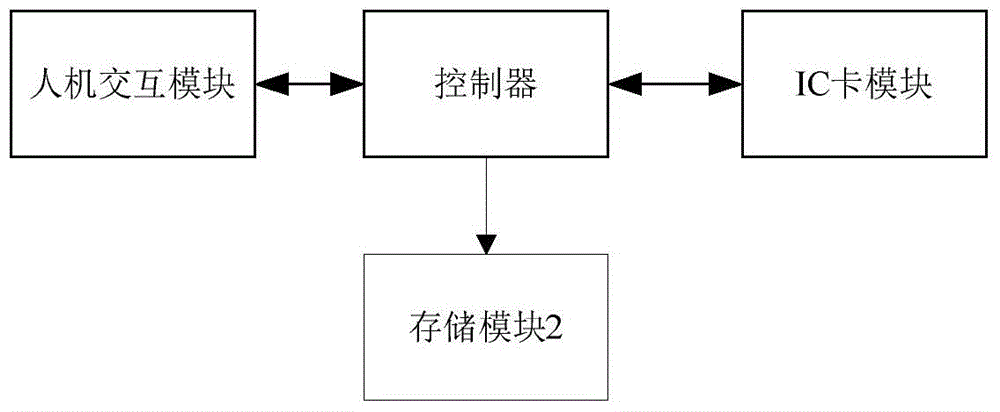

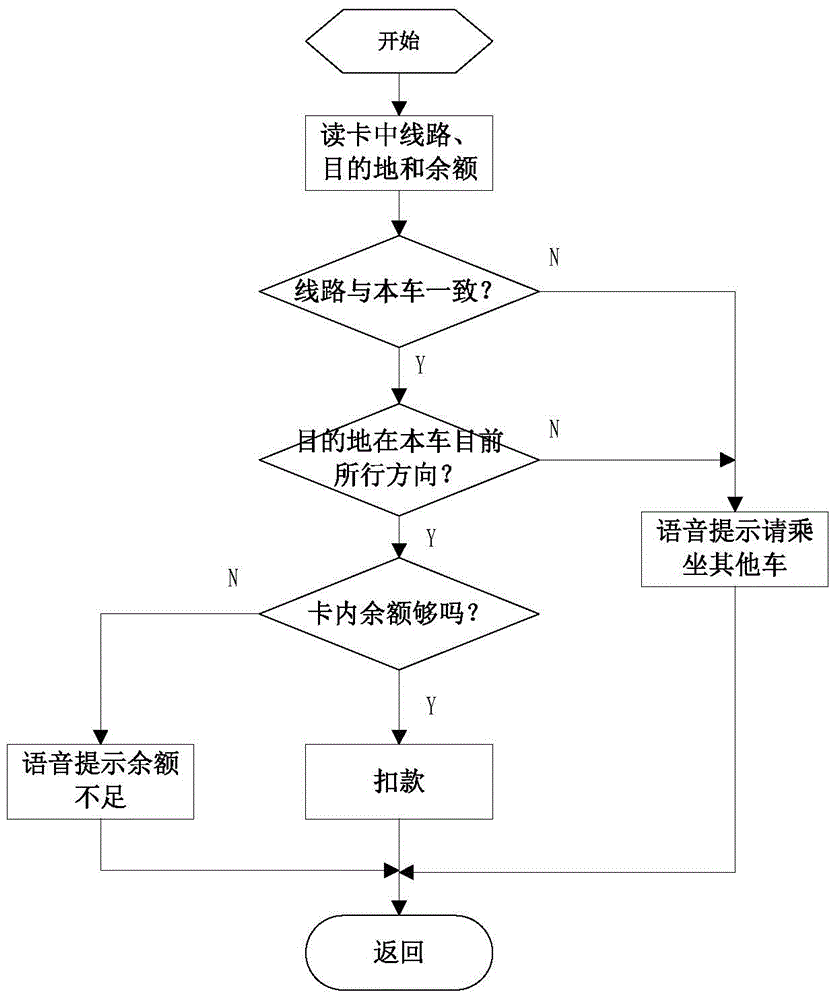

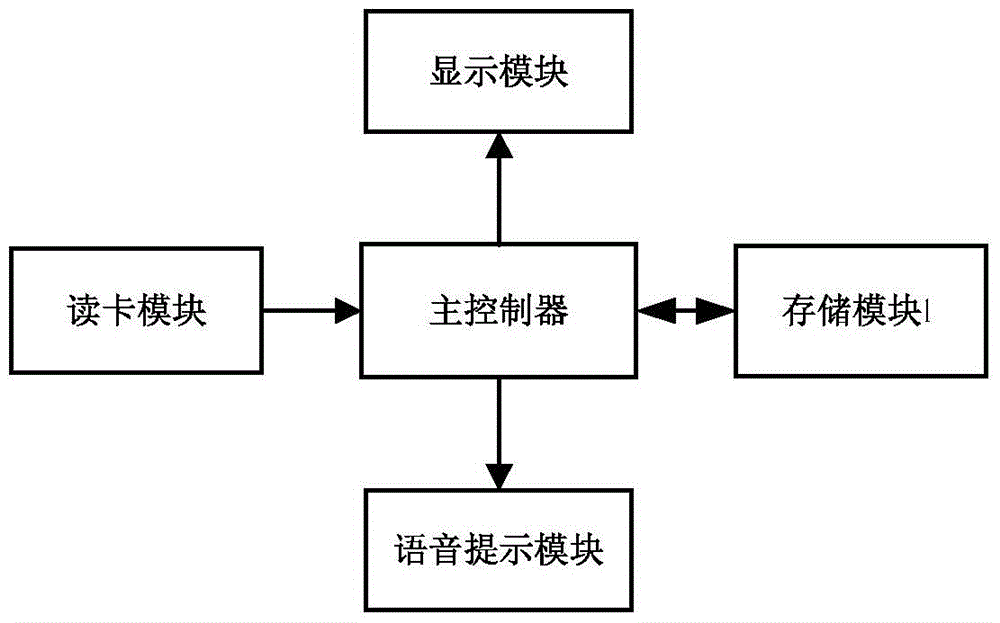

Intelligent bus card swiping management system and method

InactiveCN104574654AShorten the timeSave moneyData processing applicationsCoded identity card or credit card actuationUser inputCard reader

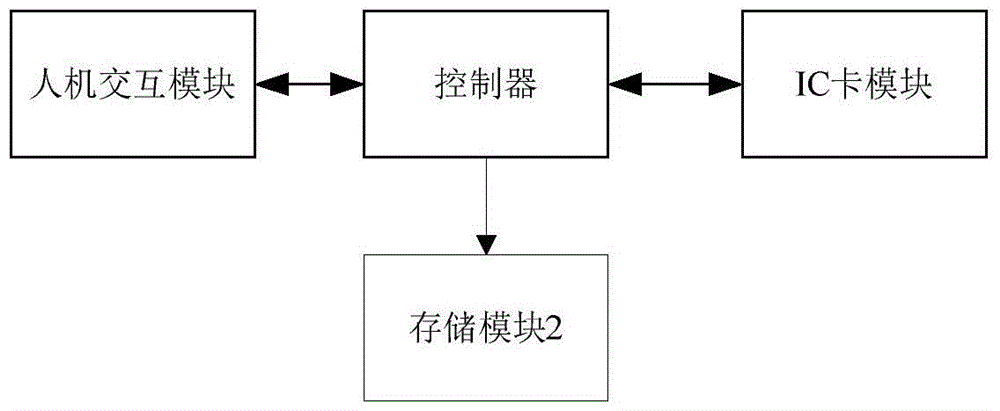

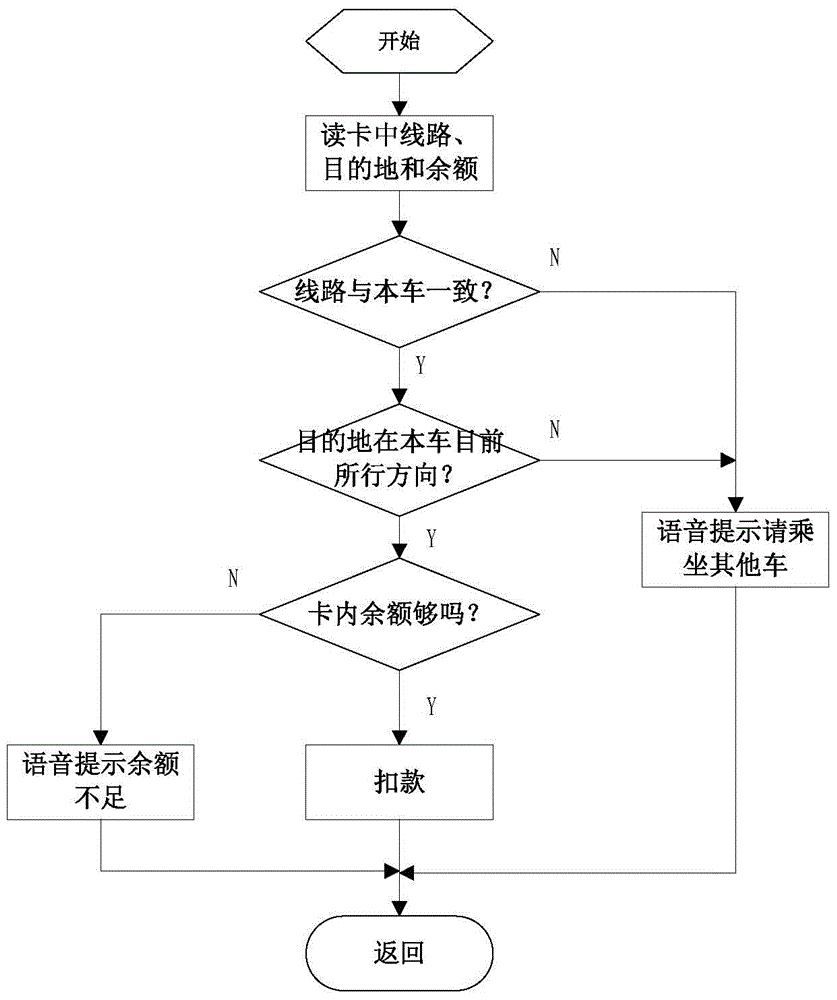

The invention provides an intelligent bus card swiping management system and method. The intelligent bus card swiping management system comprises a card swiping machine module and bus card modules, wherein the card swiping machine module is mounted on a bus, and the bus card modules are used by users during bus taking; the card swiping machine module comprises a main controller, a card reader module, a memory module 1, a display module and a voice prompt module, and each bus card module comprises an IC (Integrated Circuit) card module, a controller, a memory module 2 and a human-machine interaction module. According to the system and the method, before bus taking, a user inputs a bus line or destination and selects to take the most reasonable bus; when the corresponding user gets on the bus and swipes the corresponding card, the card swiping machine module reads information from the corresponding IC card module, judges whether the line needed to be ridden by the corresponding user is consistent with that of the bus or not, prompts the corresponding user of wrong-bus taking with voice if the line needed to be ridden by the corresponding user is inconsistent with that of the bus, further judges whether the balance of the corresponding card of the corresponding user is sufficient or not if the line needed to be ridden by the corresponding user is consistent with that of the bus, prompts the corresponding user of insufficient balance if the balance of the corresponding card of the corresponding user is insufficient, and charges if the balance of the corresponding card of the corresponding user is sufficient; thus, unsuspecting waste caused the wrong-bus taking of the users can be avoided, the time and money of the users are saved, and meanwhile, bus resources are saved.

Owner:CHANGZHOU UNIV

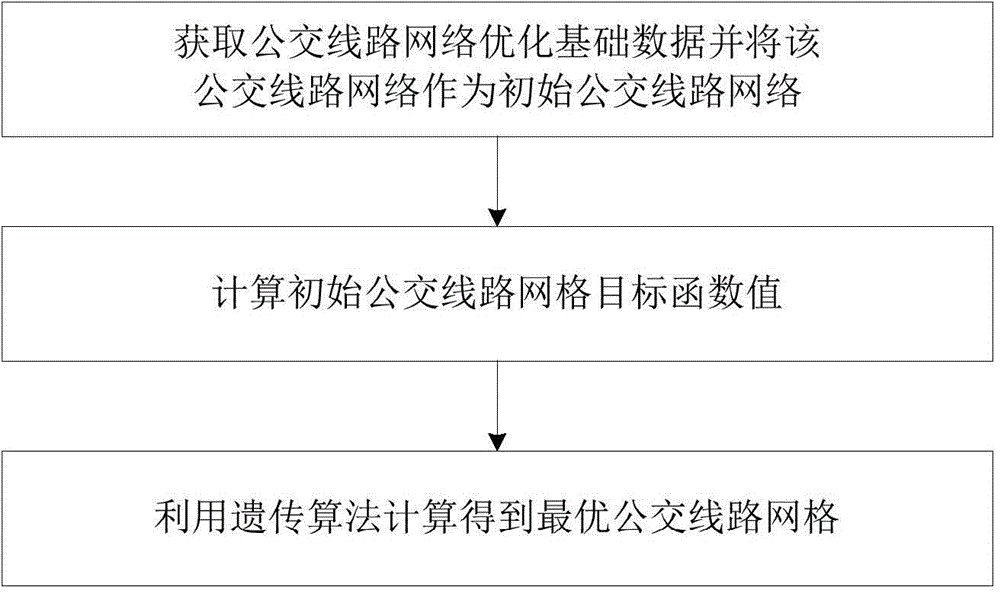

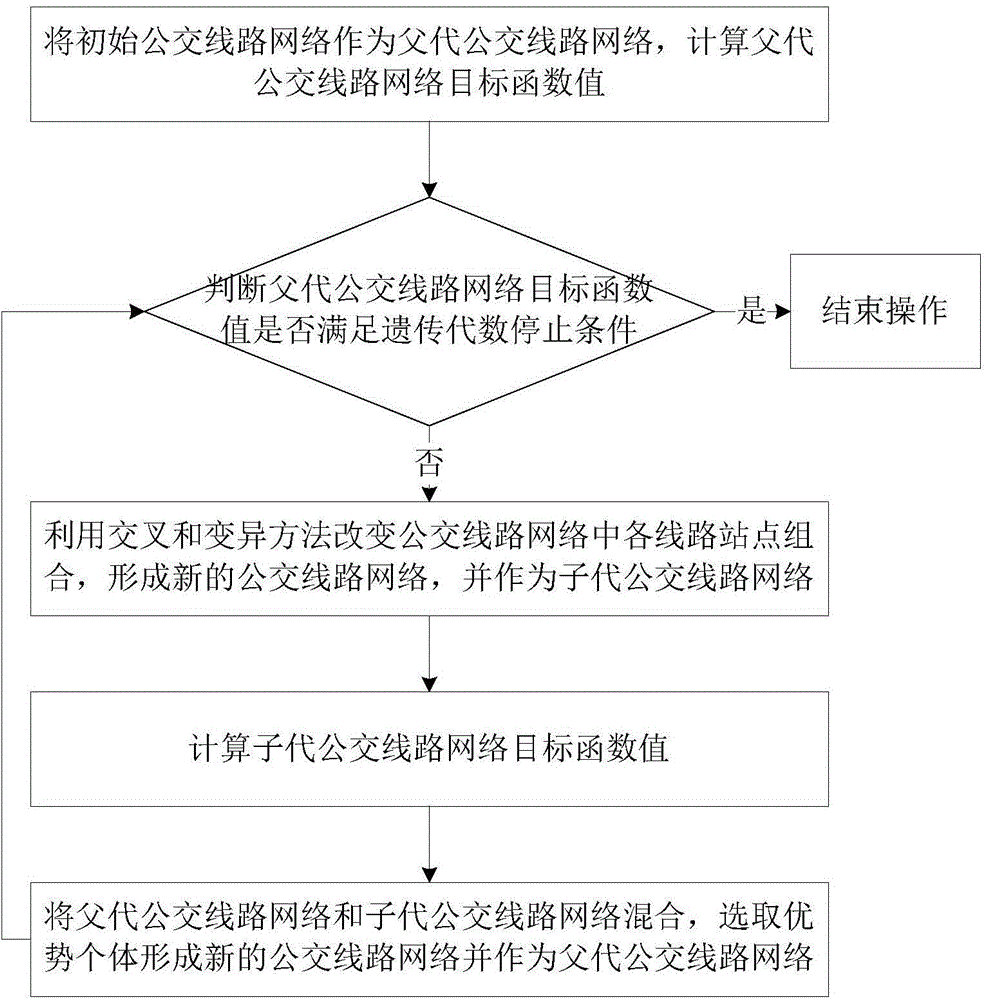

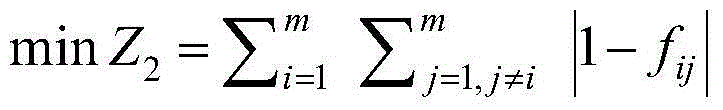

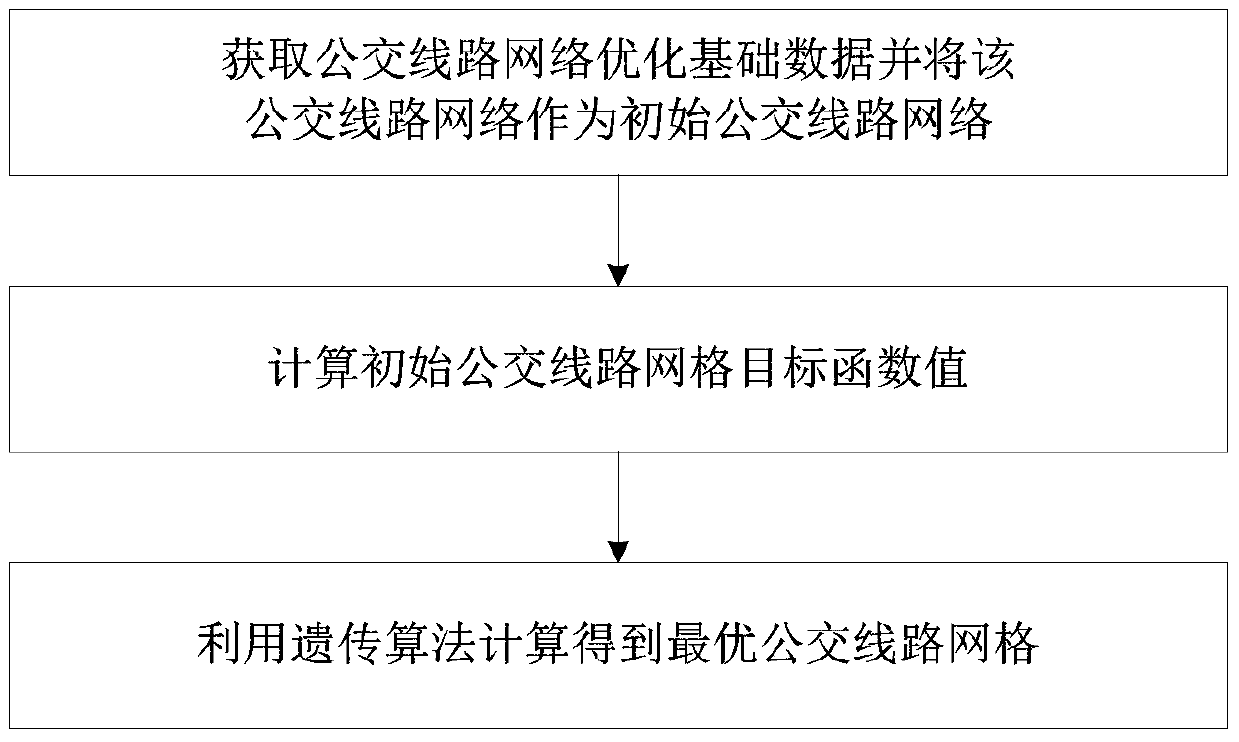

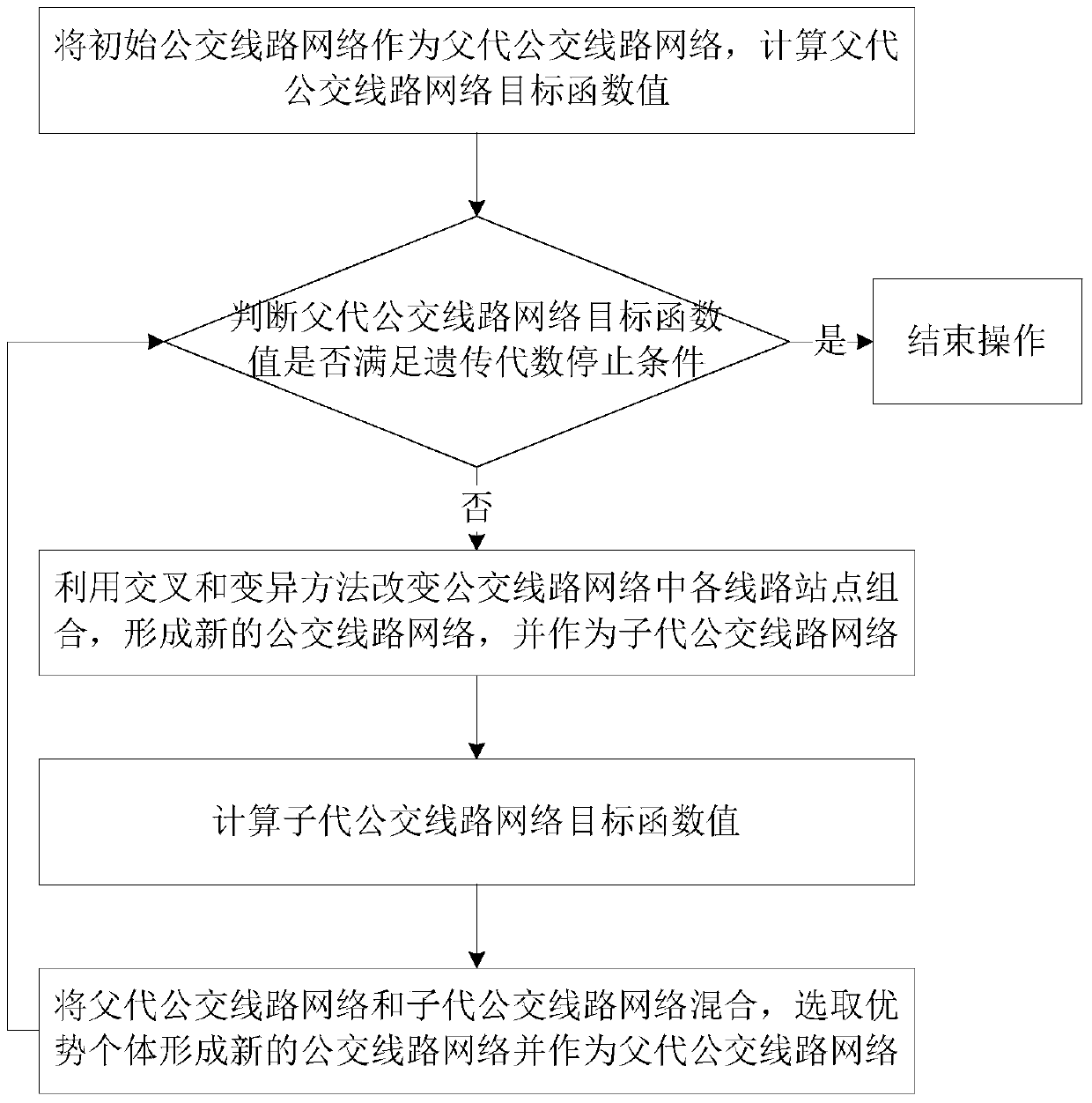

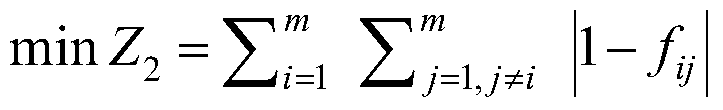

Bus route network optimization method based on reachability and reachability strength

InactiveCN104966135AReduce operating costsImprove accessibilityGenetic modelsForecastingReachabilityGenetic algorithm

The invention discloses a bus route network optimization method based on reachability and reachability strength. The method comprises the following steps: obtaining bus route network optimization basic data and serving a bus route network as an initial bus route network; and calculating object function value of the initial bus route network and obtaining an optimal bus route network by utilizing a genetic algorithm. The method can improve bus route network reachability on the service basis of meeting the original travel demands, realizes reachability strength and travel intensity matching maximization, allows the public transport operation cost to be minimum and saves public transport resources.

Owner:SOUTHWEST JIAOTONG UNIV

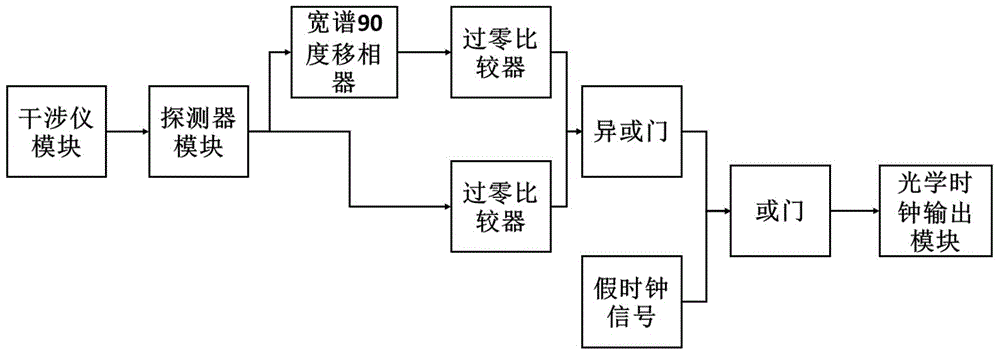

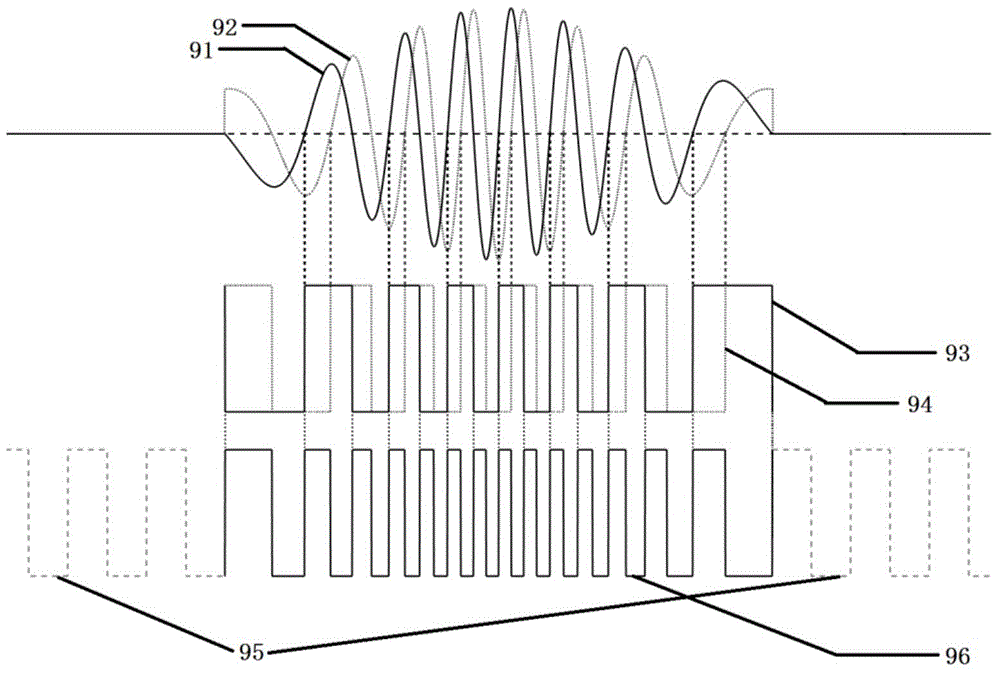

Optical clock signal generation system and method used in OCT (Optical Coherence Tomography) endoscopic scanning imaging system

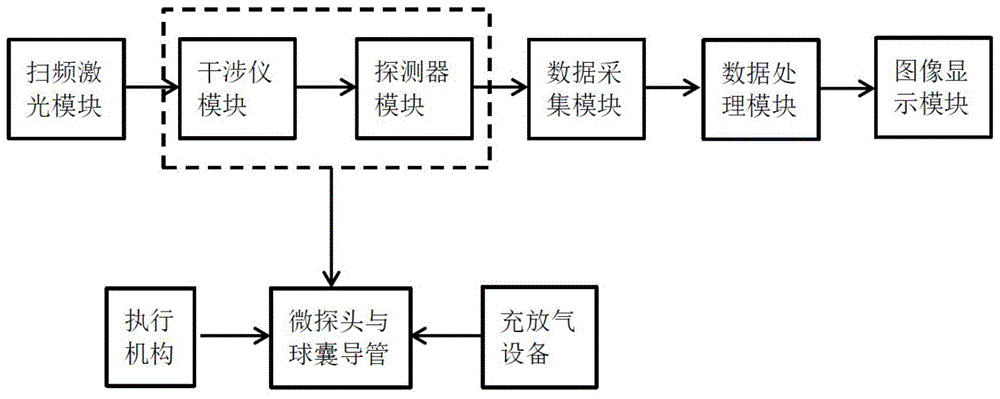

InactiveCN104825120AAffect rotationAffect concentricityGastroscopesOesophagoscopesTime domainExclusive or

The invention provides an optical clock module and a signal generation method thereof used in an OCT (Optical Coherence Tomography) endoscopic scanning imaging system. The optical clock module comprises an interference module, a detector module and an optical clock conversion circuit module, wherein the optical clock conversion circuit module comprises a wideband 90-degree phase shifter, a zero-crossing comparator, a circuit formed by an exclusive-OR gate and an OR gate, and an optical clock signal output module. The invention also provides the OCT endoscopic scanning imaging system comprising the optical clock module. According to the invention, the conversion from an MZI (Mach Zehnder Interferometer) optical interference signal to an optical clock signal with uniformity on frequency domain and frequency variation on time domain is realized, the requirement on a sampling and processing system is reduced, the collection of redundant information is reduced, and the load of a storage system is reduced, so that the integration level of the whole OCT system is improved, and the system cost is reduced.

Owner:MICRO TECH (NANJING) CO LTD

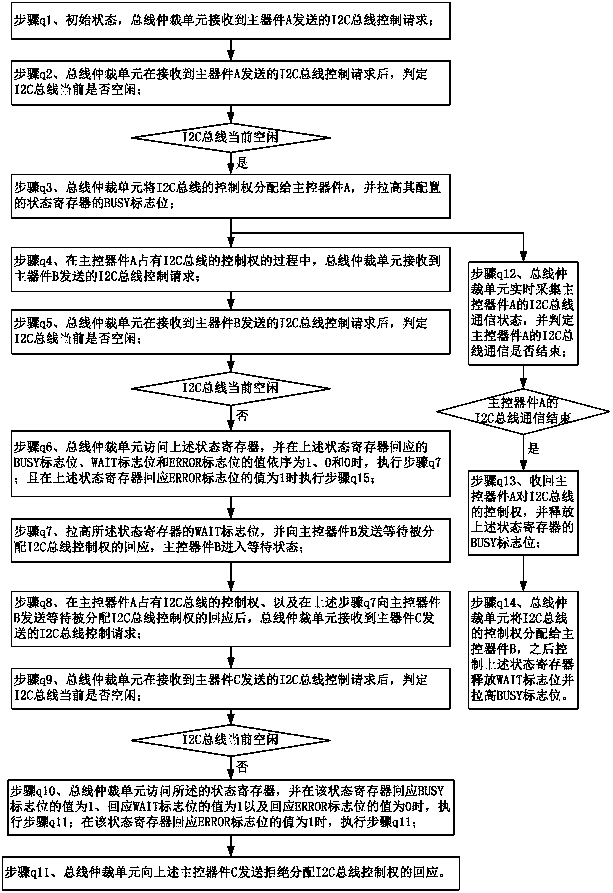

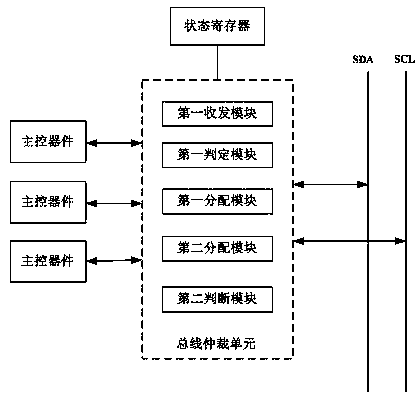

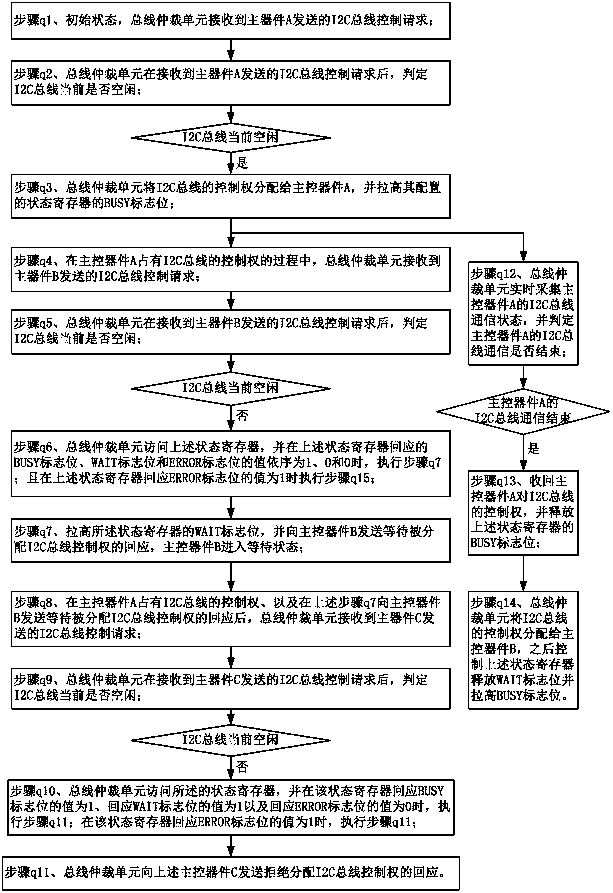

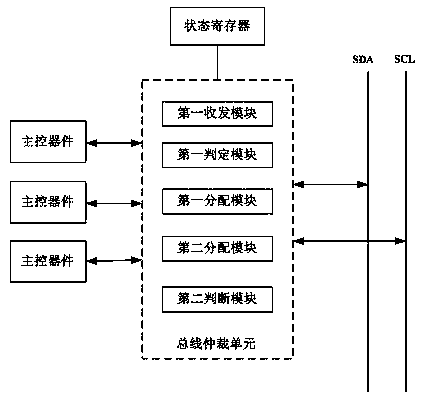

Arbitration method and system of I2C (Inter-Integrated Circuit) bus

ActiveCN107766267AHigh speedAvoid long-term occupancyElectric digital data processingCommunication qualityBus mastering

The invention provides an arbitration method and system of an I2C (Inter-Integrated Circuit) bus. According to both the method and system, control right of the I2C bus is allocated to a current main control device when the I2C bus is currently idle, and overall allocation on the bus control right of the above-mentioned current main control device is realized on the basis of received values, whichare of corresponding flag bits and currently fed back by a status register, when the I2C bus is not currently idle; and I2C bus communication status of each currently authorized main control device iscollected in real time, each time I2C bus communication ending of a corresponding currently-authorized main control device is determined, I2C bus control right of the corresponding currently-authorized main control device is taken back, and the above-mentioned status register is controlled to release the BUSY flag bit thereof, and the currently authorized main control device is a main control device with the currently allocated I2C bus control right. According to the method and system, free switching of the I2C bus control right under status of multiple main control devices can be realized, and a communication rate, communication stability and communication quality of the I2C bus are improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

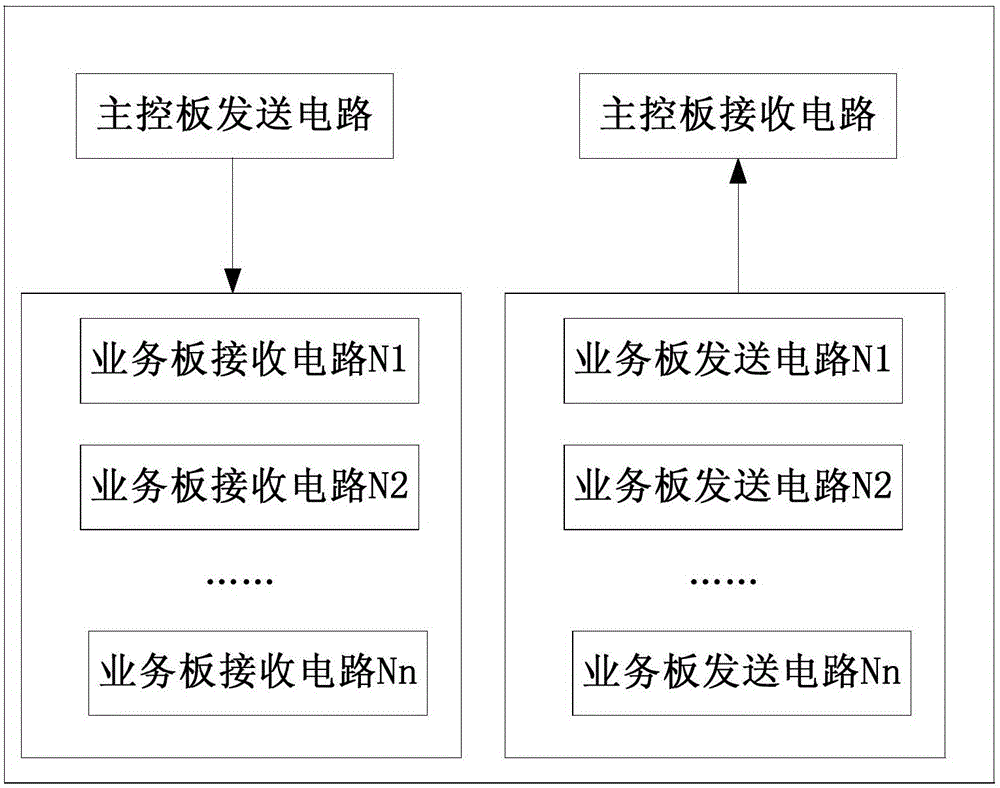

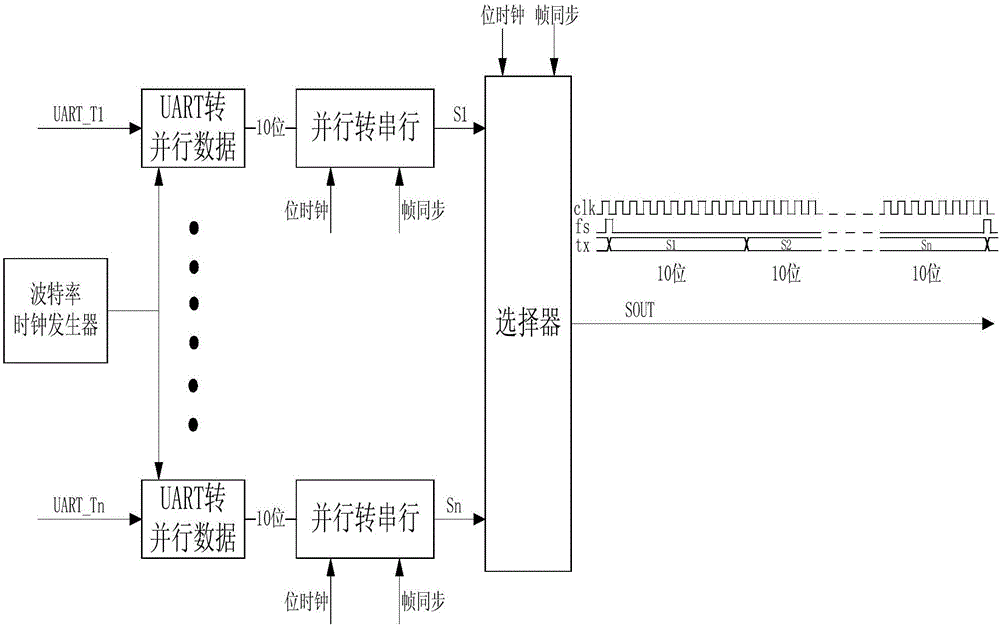

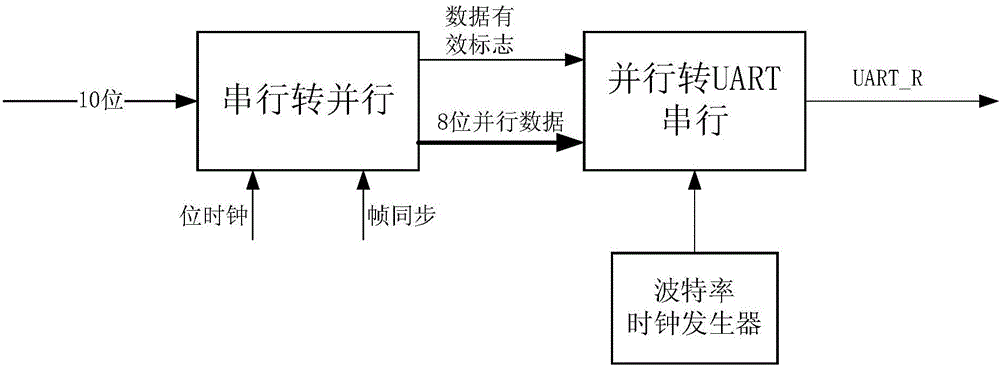

Serial interface conversion device capable of saving bus resources and serial interface conversion method

ActiveCN106372028ASave bus resourcesImprove stabilityElectric digital data processingTime-sharingUniversal asynchronous receiver/transmitter

The invention discloses a serial interface conversion device capable of saving bus resources and a serial interface conversion method. The serial interface conversion method comprises the following steps: S1, judging whether a UART (Universal Asynchronous Receiver Transmitter) has start bit change or not; when a transmitting circuit end UART of a main control board has the start bit change, turning into S2, or otherwise, turning into S5; S2, converting a serial interface of which the UART has the start bit change, and determining an output channel number of serial data; S3, finding a service board receiving circuit of a corresponding time slot according to the output channel number; S4, receiving the serial data transmitted by a transmitting circuit of the main control board by the service board receiving circuit of the corresponding time slot, and converting and outputting the serial data; S5, converting the serial interface of which the UART has the start bit change, and determining an output time slot of the serial data; S6, finding a corresponding channel number according to the output time slot, transmitting the serial data to a receiving circuit of the main control board by the channel number, and converting and outputting the serial data. According to the method, data on a bus are subjected to time sharing multiplex, so that bus resources are saved.

Owner:北京佳讯飞鸿技术有限公司

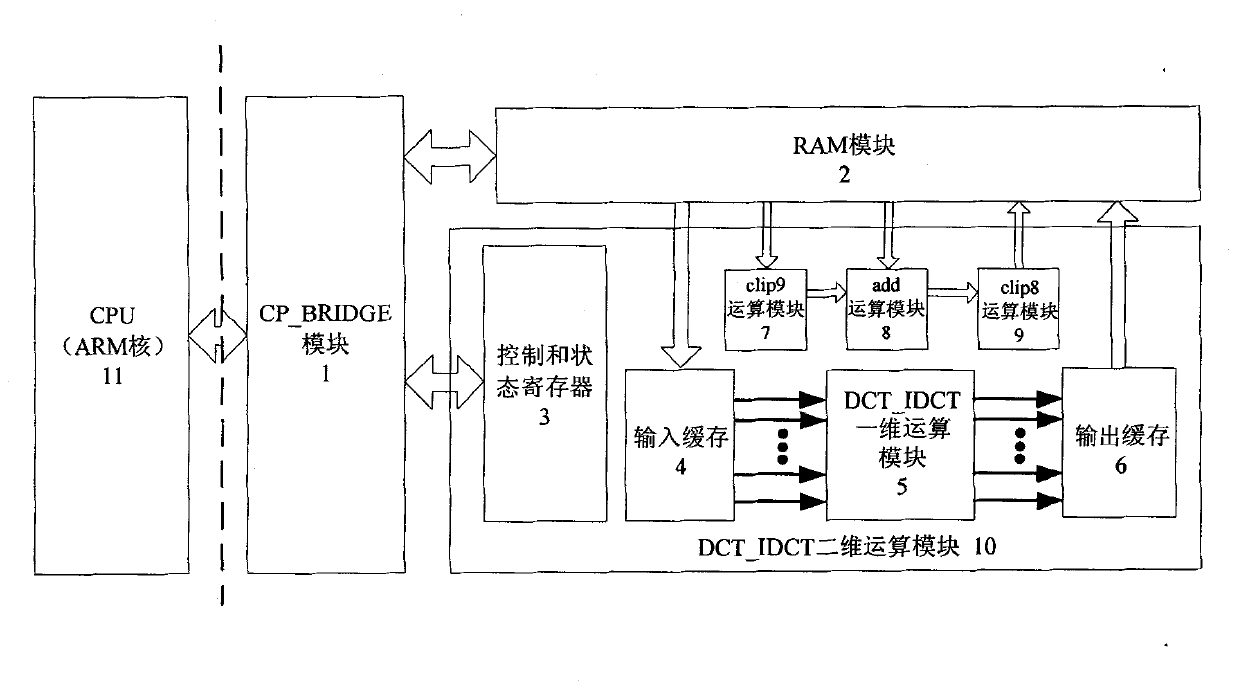

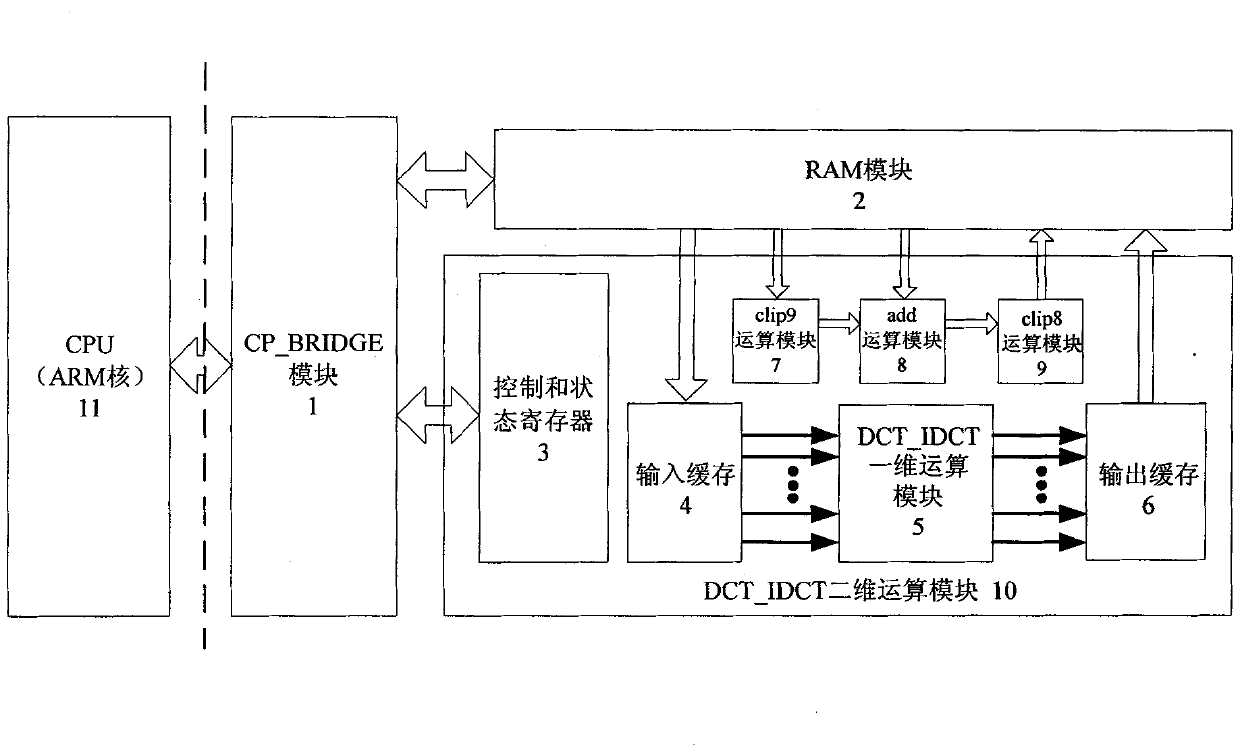

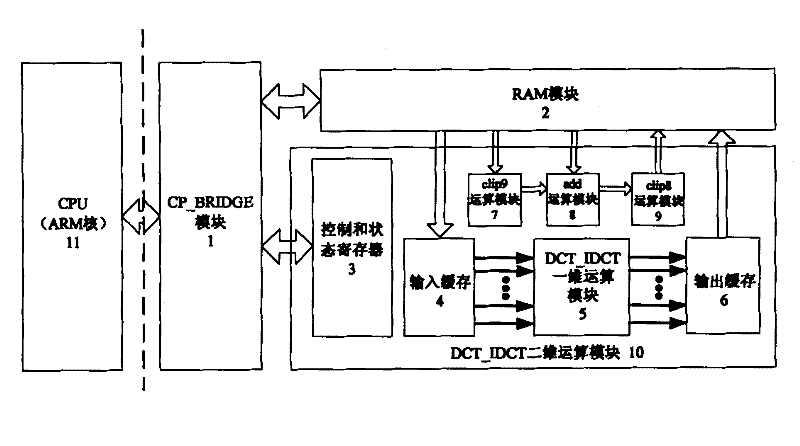

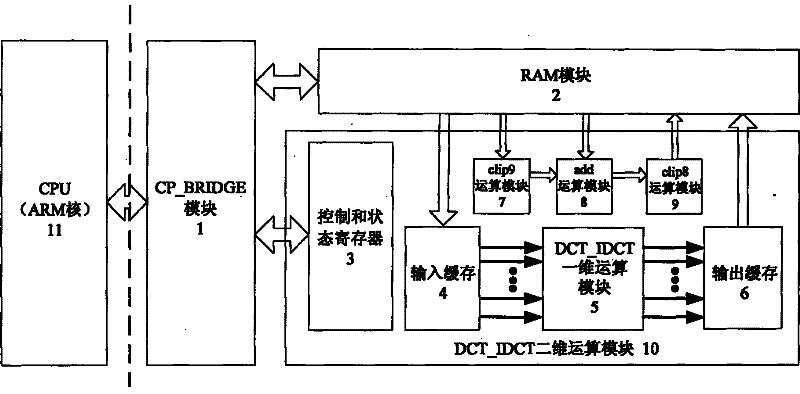

Discrete cosine transform (DCT)-inverse discrete cosine transform (IDCT) coprocessor suitable for system on chip (SOC)

InactiveCN101794276AFast operationReduce the numberDigital computer detailsComplex mathematical operationsBinary multiplierCoprocessor

The invention provides a discrete cosine transform (DCT)-inverse discrete cosine transform (IDCT) coprocessor suitable for a system on chip (SOC). The DCT-IDCT coprocessor consists of a CP-BRIDGE module, a random access memory (RAM) module, a control and state register, a DCT-IDCT two-dimensional computation module, a DCT-IDCT one-dimensional computation module, an input buffer, an output buffer, a clip computation module and an add computation module. The DCT-IDCT coprocessor is directly connected with a coprocessor interface of a central processing unit (CPU) without being additionally articulated with an advanced high-performance bus (AHB) or an advanced periphery bus (APB) so as to save the bus resource of a system to a certain degree; and an RAM, which is used for storing data to be processed and processing results, can multiplex with other coprocessor. The DCT-IDCT coprocessor has the advantages of small area, high speed, lower power consumption and the like by rationally multiplexing a multiplier and regulating cycles of operation.

Owner:东莞润风电子科技有限公司

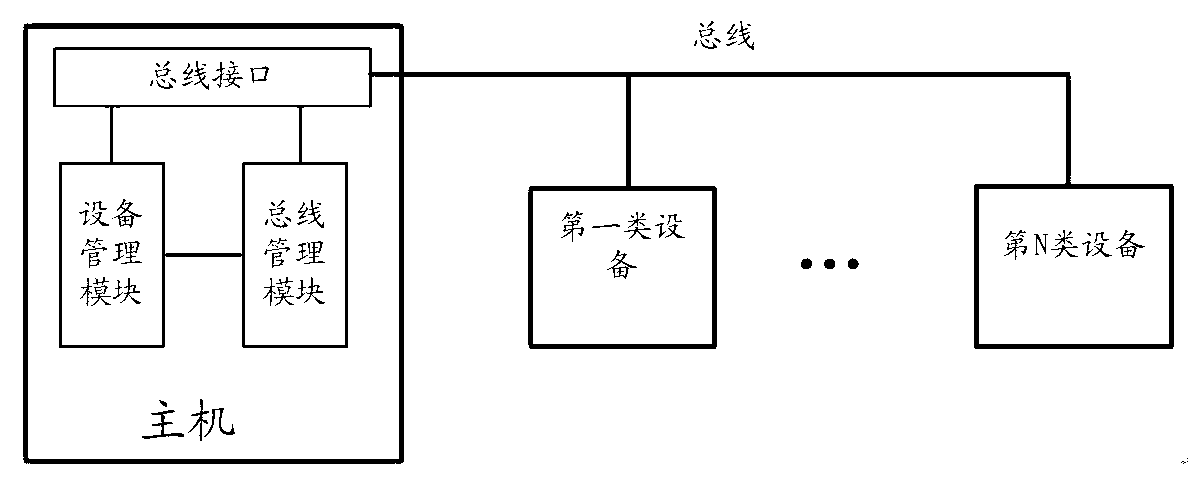

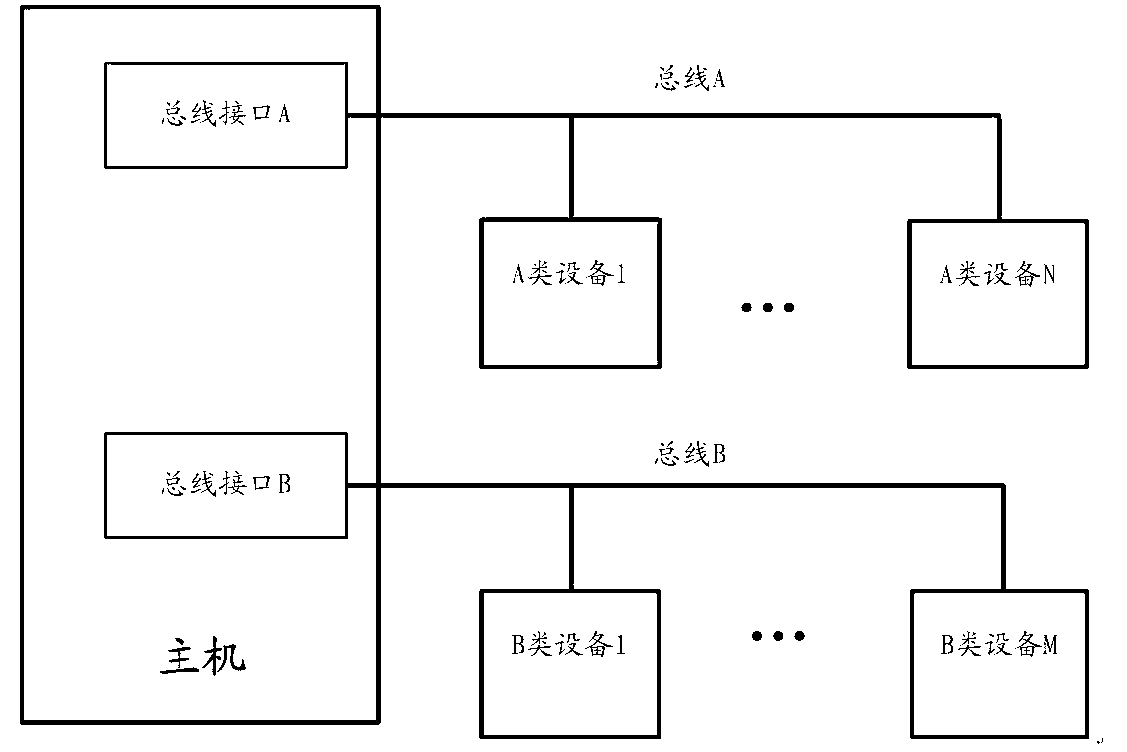

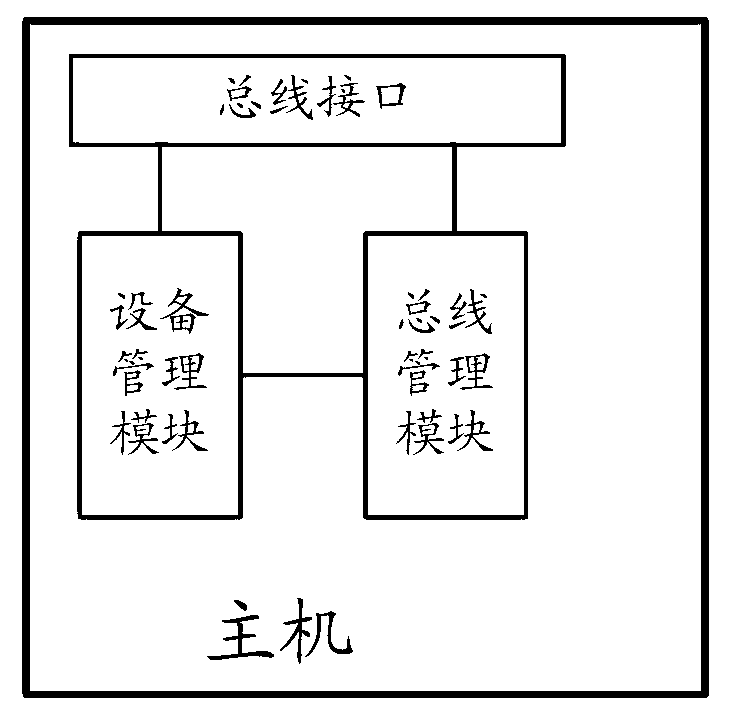

Host computer with intelligent bus interface and security system

InactiveCN102841875ASave bus resourcesReduce construction difficultyElectric digital data processingBus interfaceConnected device

The invention discloses a host computer with an intelligent bus interface, and aims at providing a host computer capable of making different devices of different types, different protocols, different addresses and different baud rates simultaneously share one bus interface to be communicated with the host computer, and the host computer comprises a bus interface which is connected with devices through a bus, and the host computer with the intelligent bus interface also comprises a bus management module which is connected with the bus interface and a device management module which is connected with the bus interface and the bus management module, wherein the occupation of the bus is gradually allocated to each device according to time slices, a parameter of the bus is adjusted to the parameter which is consistent with the device when each device acquires the bus occupation, and a communication starting instruction is transmitted; and the device management module receives the communication starting instruction and notifies the host computer to utilize a protocol corresponding to the device acquiring the occupation to be communicated with the device according to the communication starting instruction. The invention also discloses a security system. The host computer with the intelligent bus interface can be used for the security system.

Owner:SHENZHEN UNITED INNOVATION AUTO CONTROL SYST

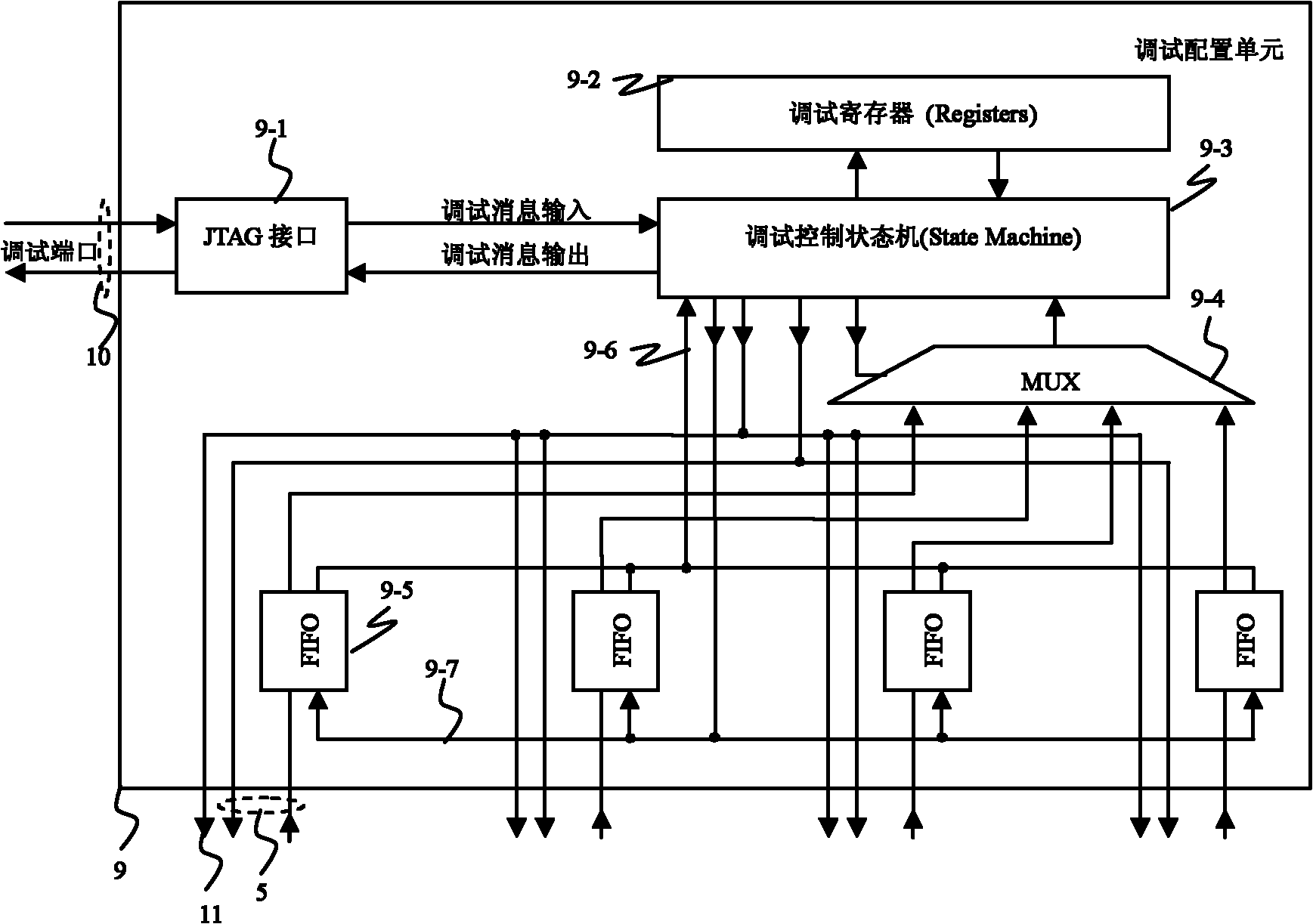

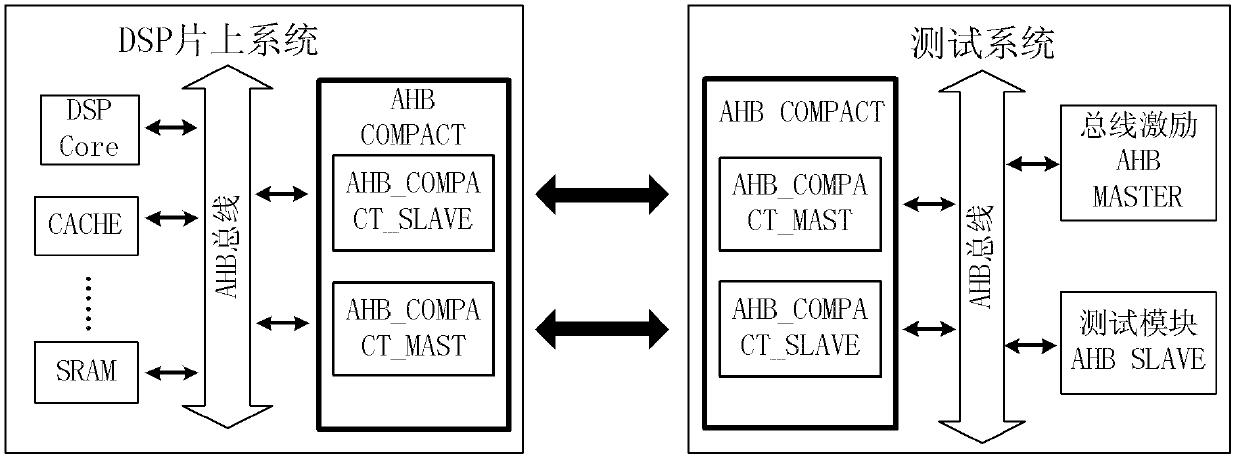

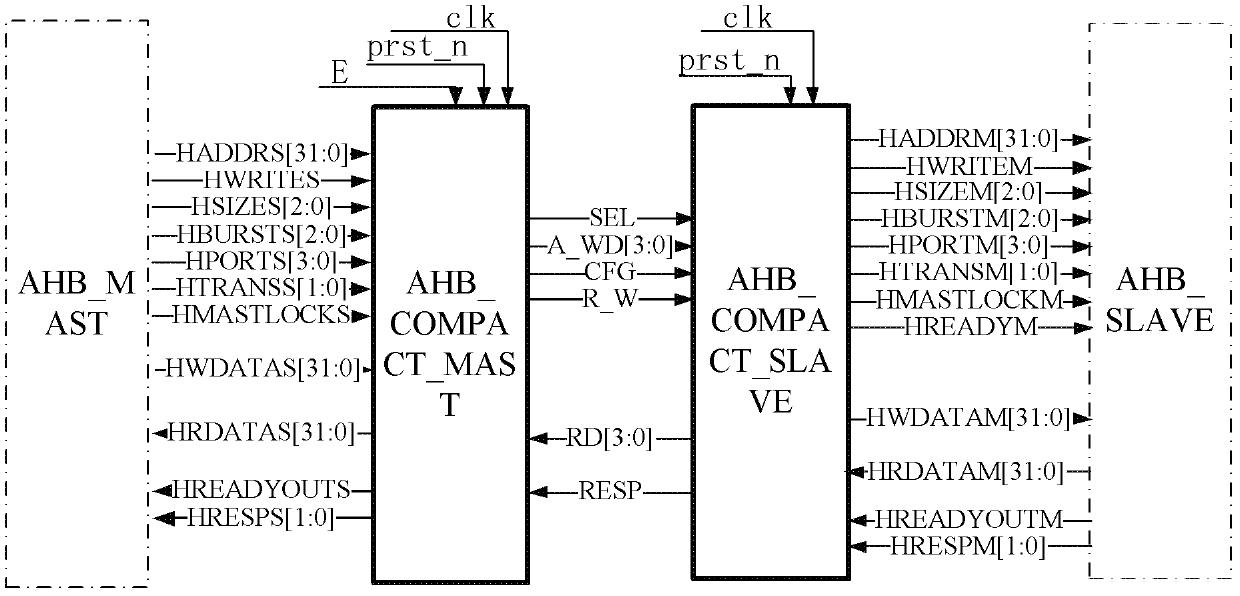

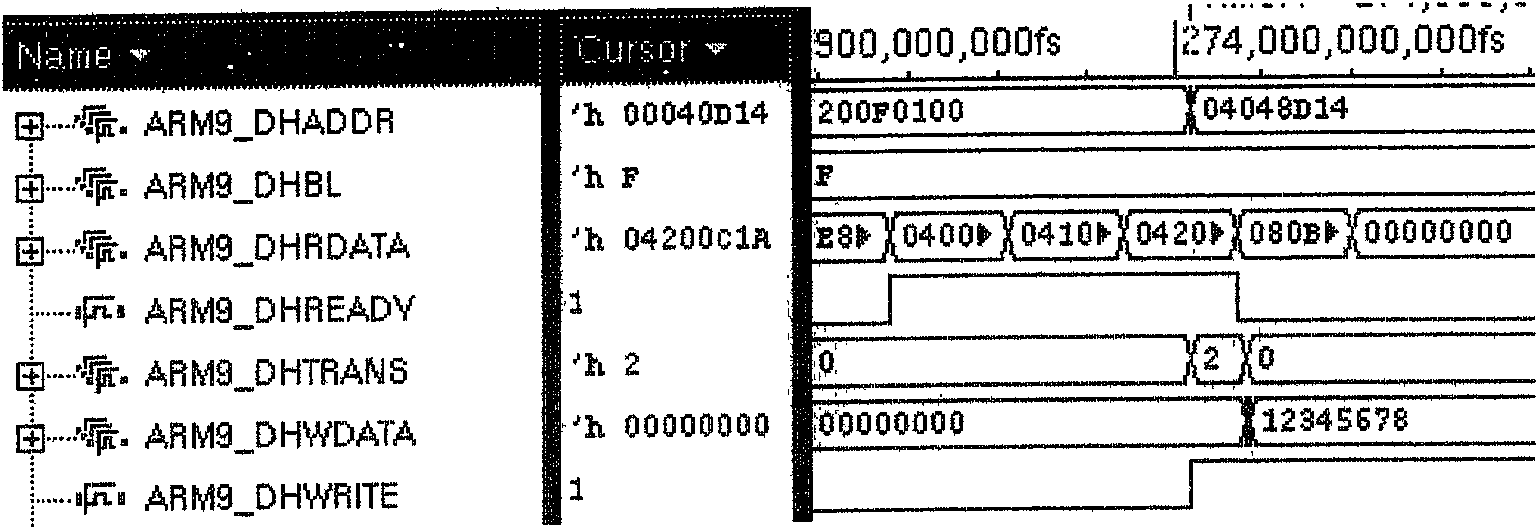

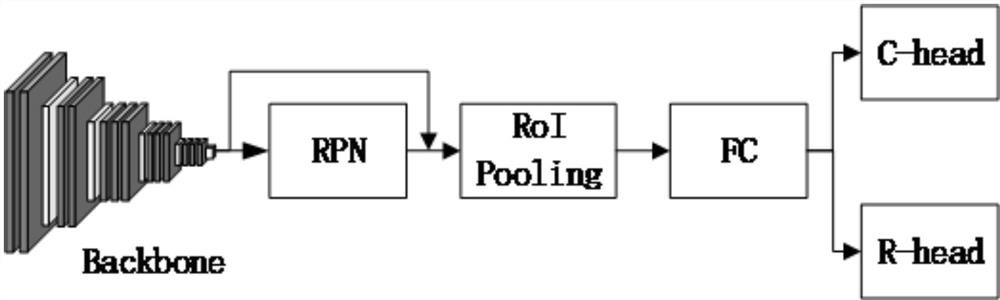

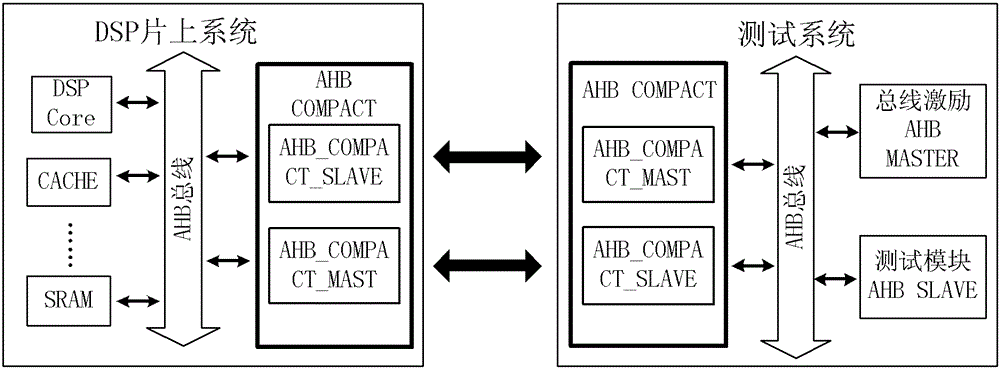

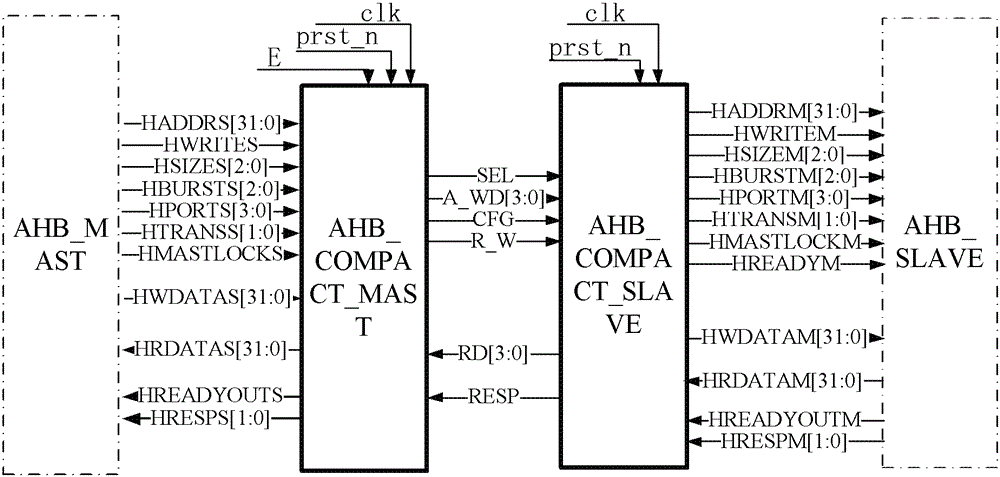

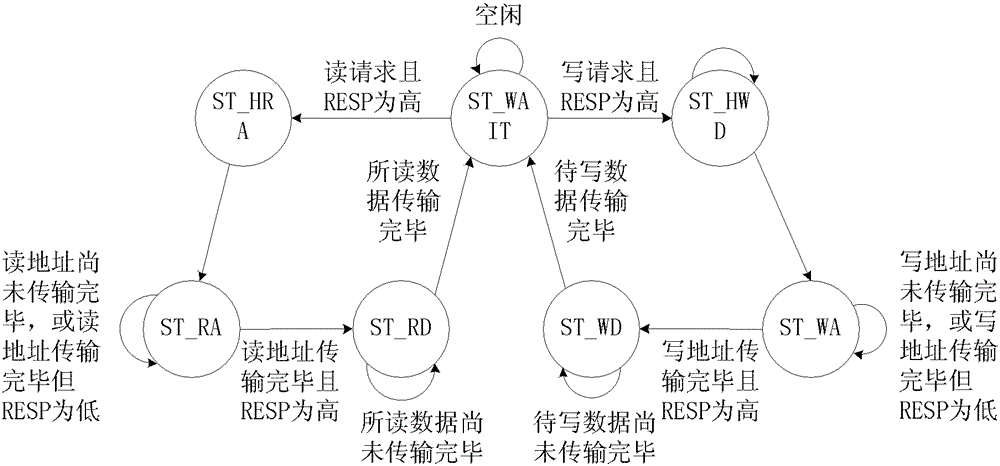

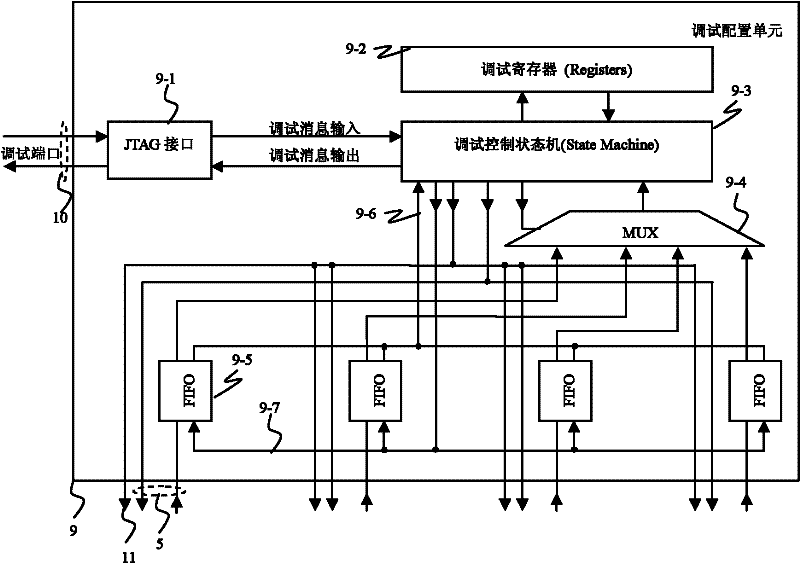

DSP (Digital Signal Processor) debugging device

InactiveCN103309798AImprove real-time performanceImprove throughputSoftware testing/debuggingComputer moduleData transmission

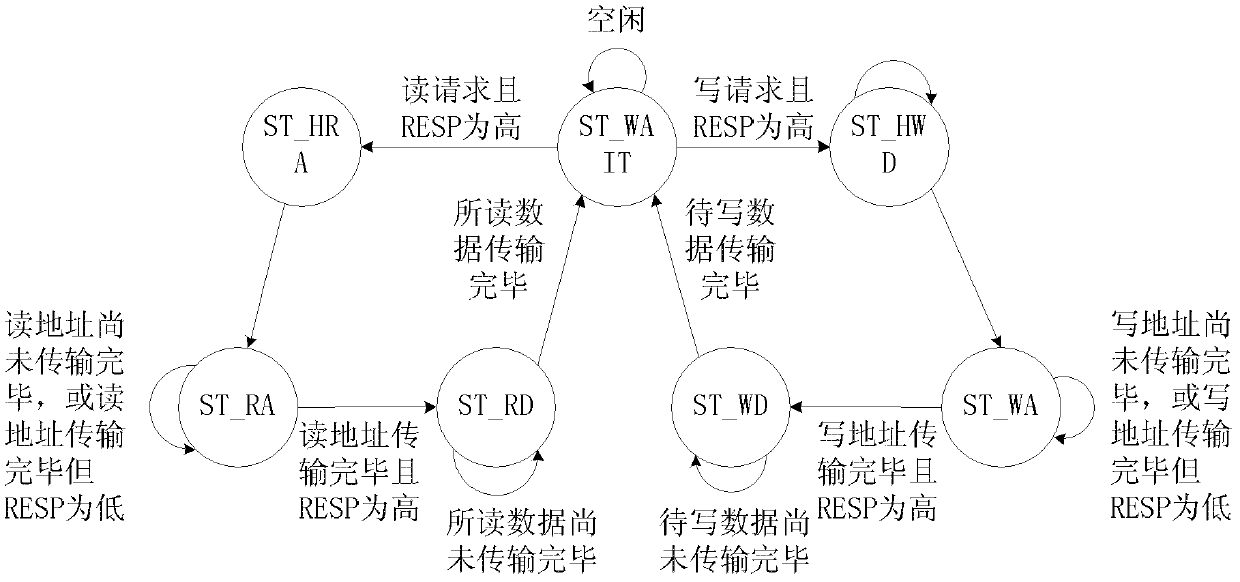

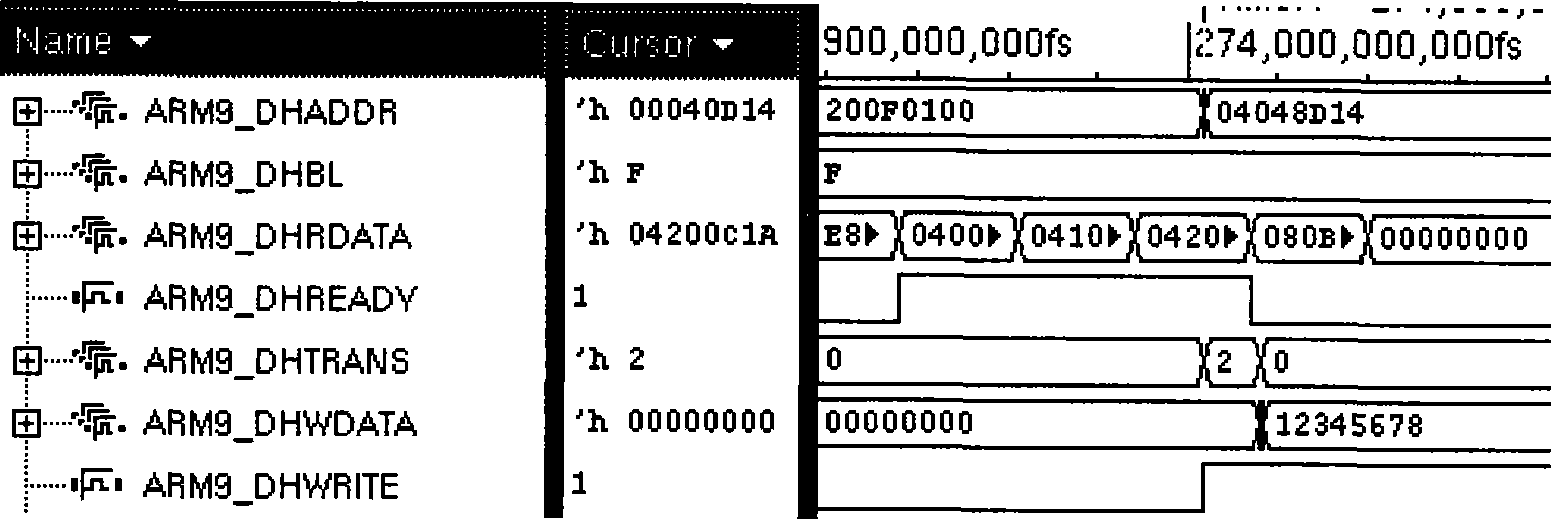

The invention provides a DSP (Digital Signal Processor) debugging device which comprises two submodules of AHB_COMPACT_MAST and AHB_COMPACT_SLAVE. The device, serving as an independent IP (Internet Protocol) module, is in cascade connection with an on-chip AHB (Advanced High performance Bus) bus, and communicates with out-chip equipment through an AHB_COMPACT interface; and meanwhile, the device, serving as a part of an out-chip debugging unit, completes conversion from the AHB_COMPACT interface to an AHB interface. The AHB_COMPACT_MAST module is connected with the MAST interface of the on-chip AHB bus, and the MAST interface is converted into the AHB_COMPACT interface to be connected with a below-chip test module. The AHB_COMPACT_SLAVE is connected with an SLAVE interface of the on-chip AHB bus, and the SLAVE interface is converted into an AHB_COMPACT interface to be connected with the below-chip test module. According to the DSP debugging device, the data transmission of the two modules is completed under different AHB transmission modes through two state machines of AHB_COMPACT_MAST_FSM and AHB_COMPACT_SLAVE_FSM. A below-chip debugging unit is used for performing conversion of signals from the AHB_COMPACT interface to the AHB interface just by using the device as well in an out-chip system so as to complete communication between a DSP on-chip system and out-chip AHB equipment. The DSP debugging device provided by the invention is more flexible, more efficient, better in real time and larger in throughput, and simultaneously bus resources are also greatly saved.

Owner:SHANGHAI JIAO TONG UNIV +1

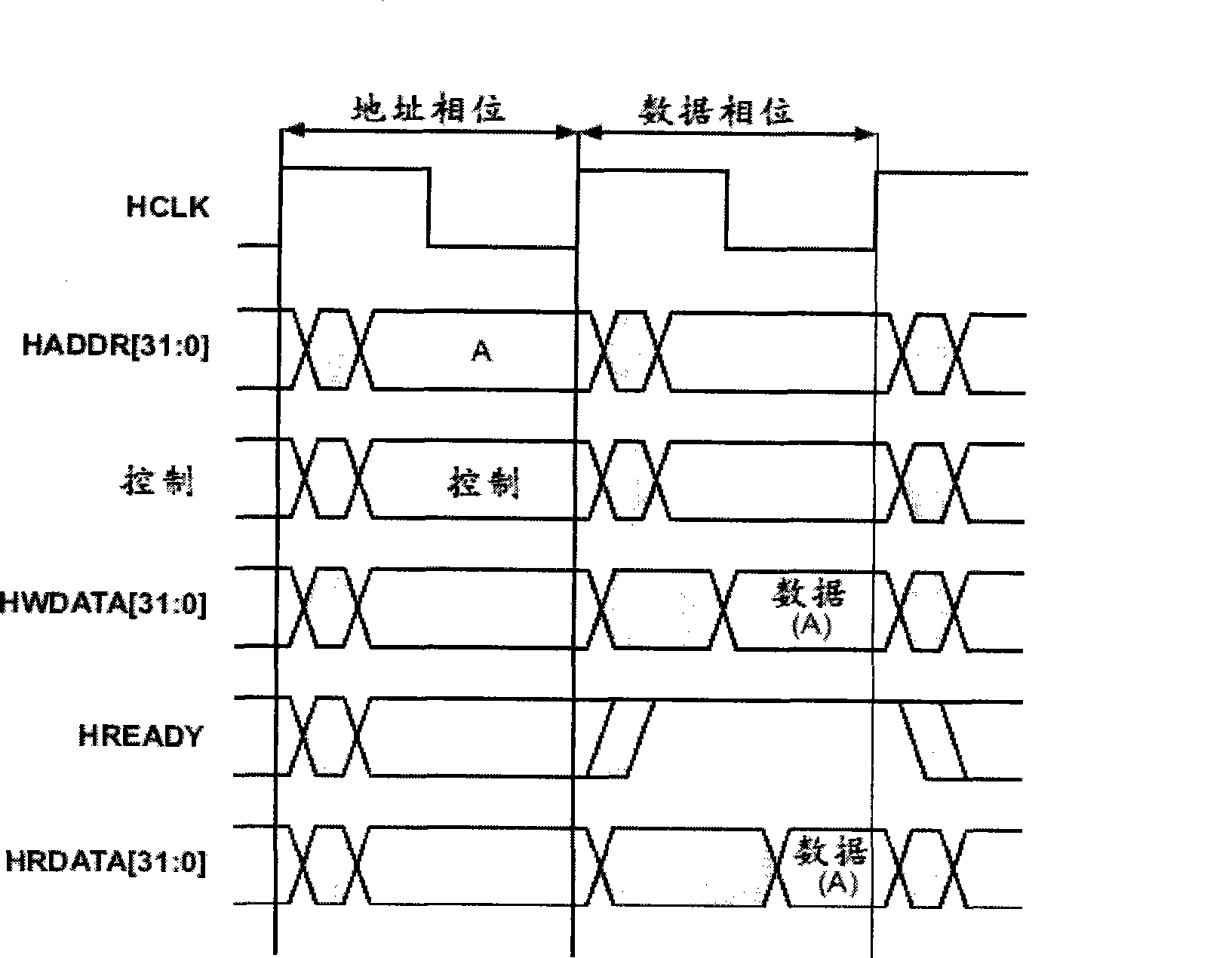

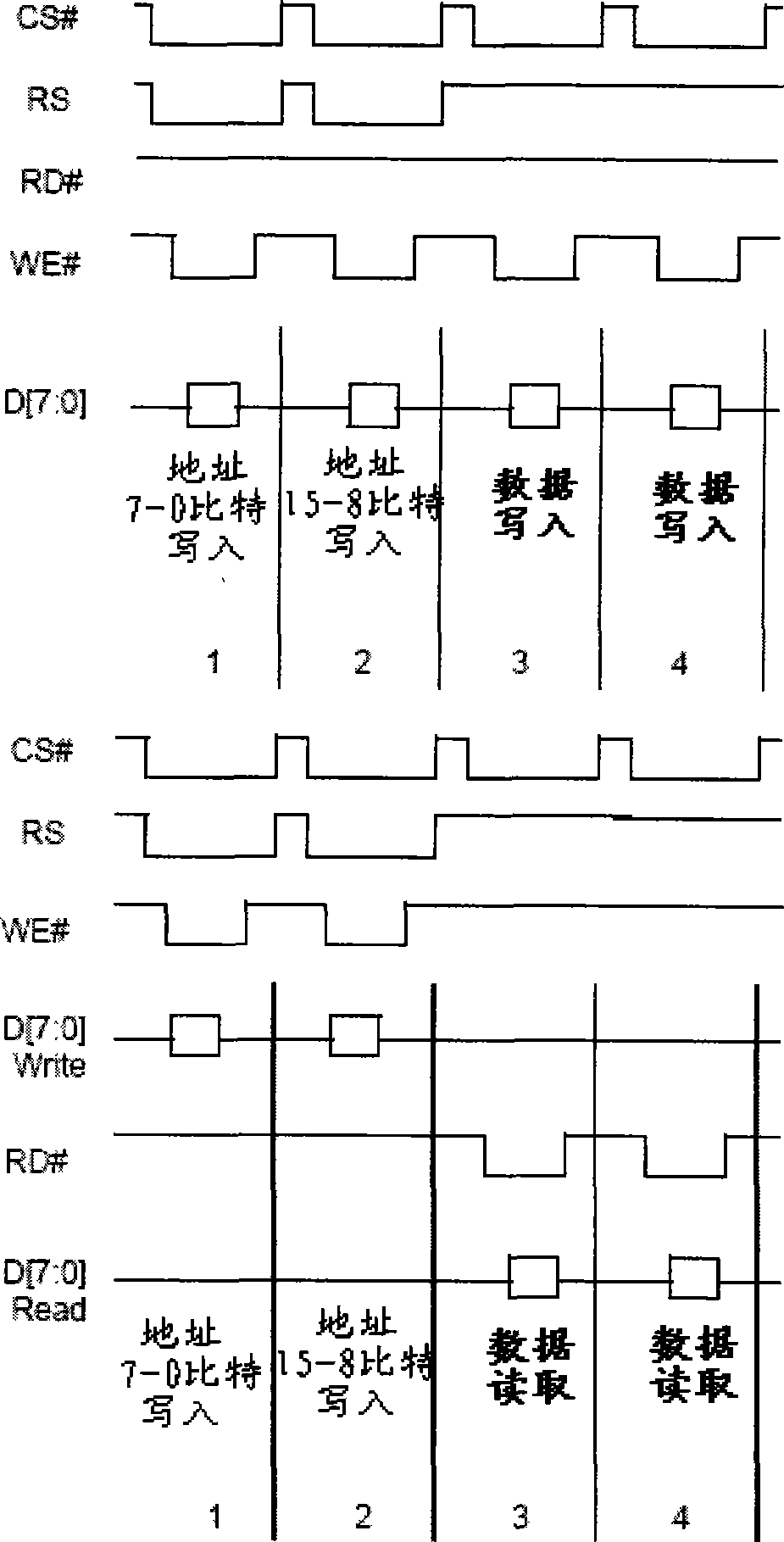

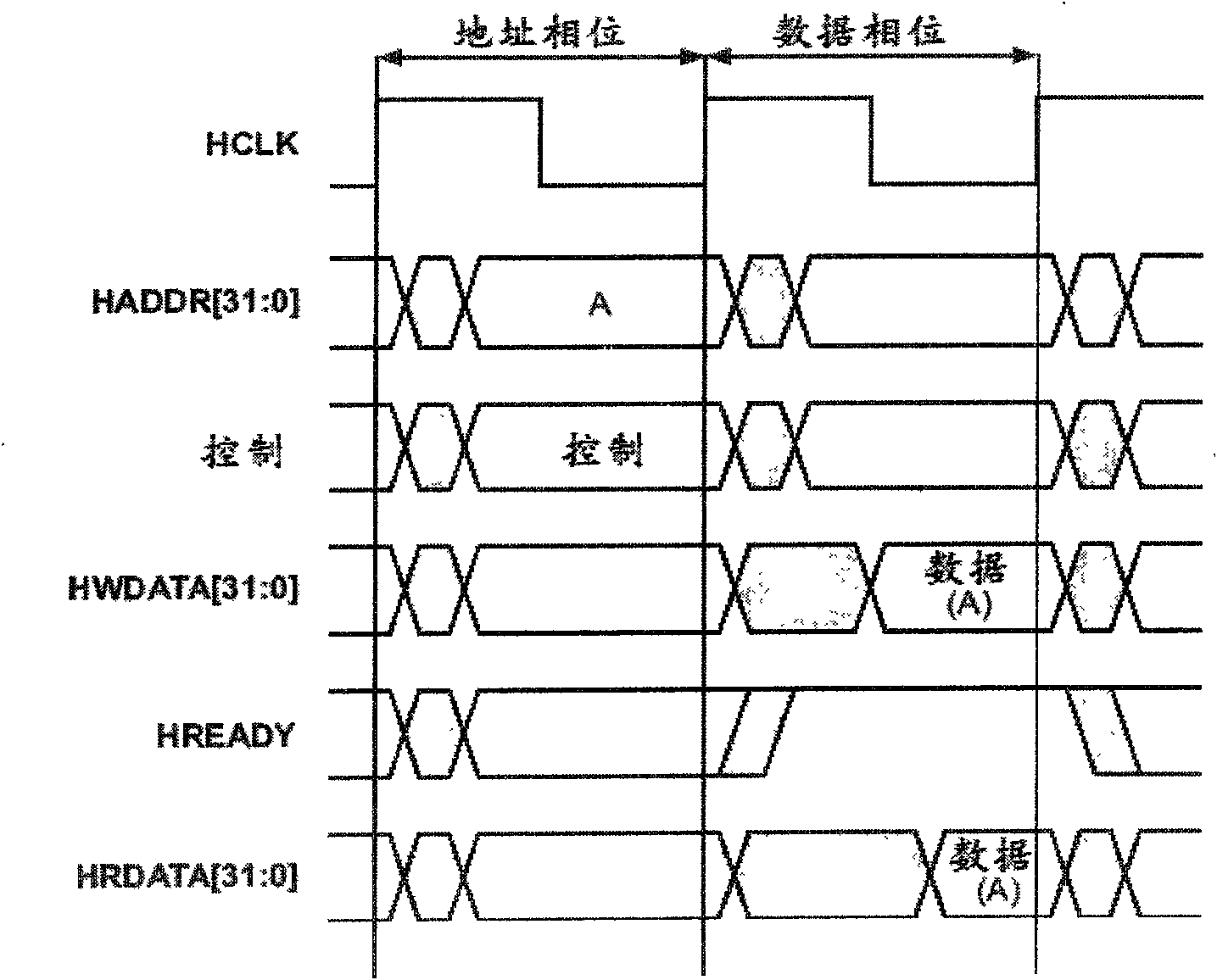

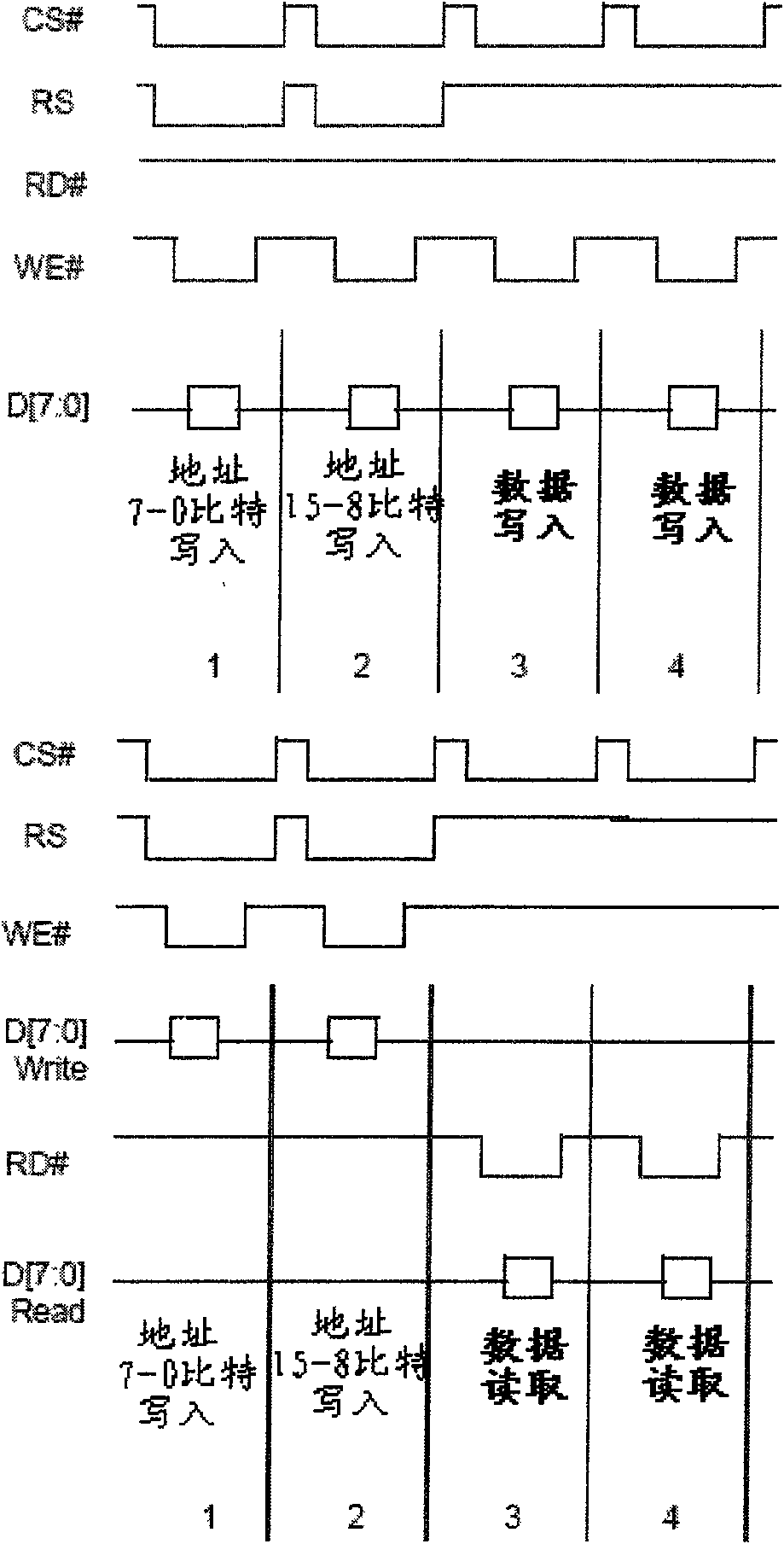

Data conversion method between AHB interface of AMBA and paralleling processor interface in RISC system

ActiveCN101382924ASave bus resourcesImprove transmission efficiencyElectric digital data processingMicrocontrollerGeneral purpose

The invention relates to a method for switching data between an AHB interface of AMBA and a parallel processor interface in an RISC system, which comprises the following steps: data switching group quantity in a single operation between a high-grade high-speed bus interface of a high-grade microcontroller bus framework and a general-purpose parallel microprocessor interface is determined, data transmitted by the high-grade high-speed bus of the high-grade microcontroller bus framework are switched into grouped data at the general-purpose parallel microprocessor interface according to the data switching group quantity, and the grouped data are transmitted by the general-purpose parallel microprocessor interface. With the adoption of the method for switching data between the AHB interface of AMBA and the parallel processor interface in an RISC system, the operation of data switching and transmission can be finished in a single operation by the AHB interface of the AMBA, thus greatly saving AMBA AHB bus resources of RM and effectively improving the transmission efficiency of data switching between interfaces. In addition, the method for switching data between the AHB interface of AMBA and the parallel processor interface in the RISC system is convenient and rapid in use, and has stable and reliable work performance and wider application scope.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

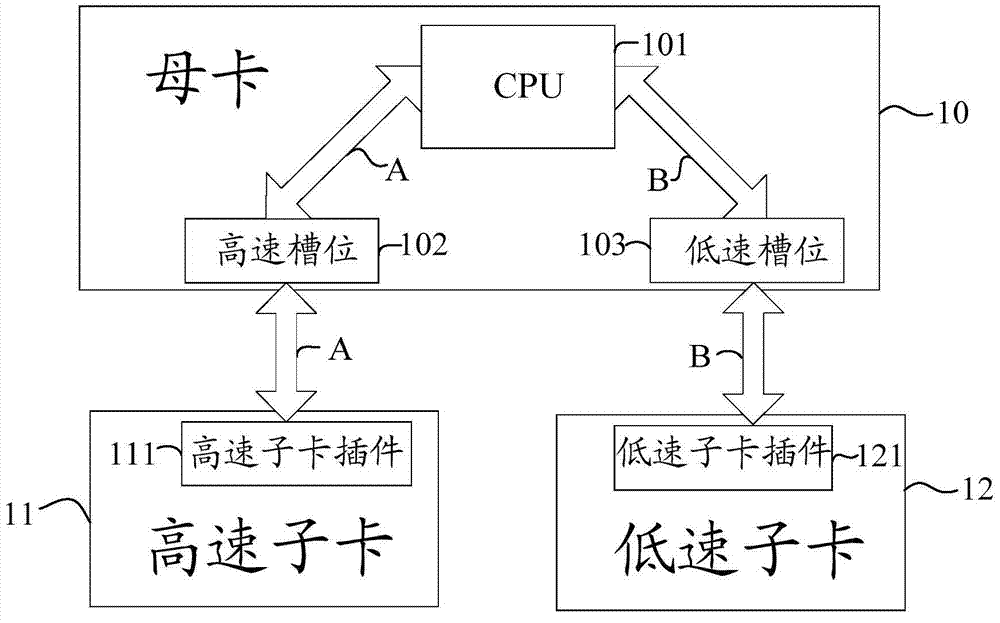

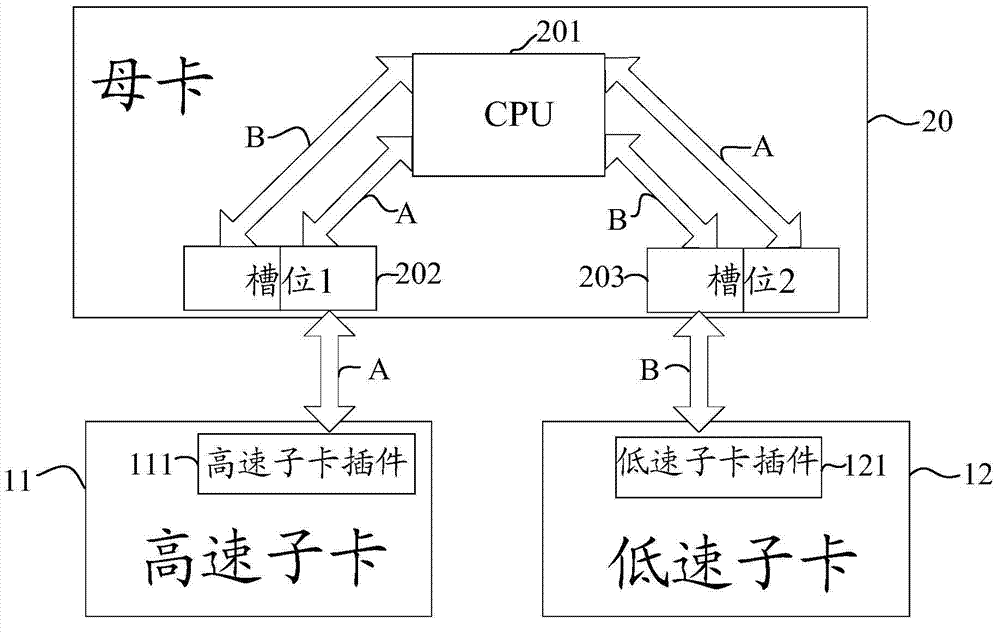

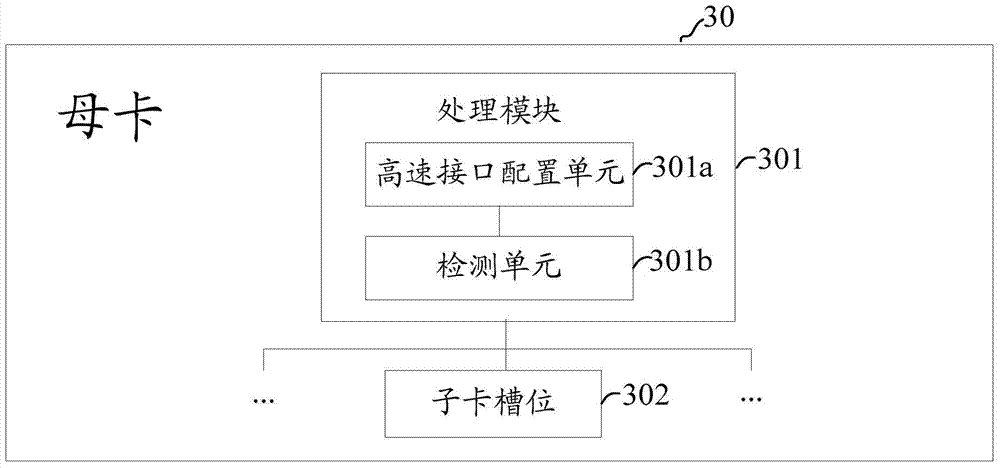

Interface configuration method, master card and high-speed daughter card

The invention provides an interface configuration method, a master card and a high-speed daughter card. Mixed insertion of a high-speed daughter card and a low-speed daughter card is realized on the premise of saving bus resources, and accordingly usability of communication equipment is improved. The interface configuration method includes: when a first daughter card is inserted into a first daughter card slot of at least one daughter card slot, a master card processing module detects daughter card types of the first daughter card, wherein the daughter card types of the first daughter card include a high-speed daughter card or a low-speed daughter card; the master card processing module sets an interface bus of a high-speed interface corresponding to the first daughter card slot into bus types corresponding to the daughter card types of the first daughter card, wherein the high-speed daughter card corresponds to a high-speed bus type while the low-speed daughter card corresponds to a low-speed bus type. The interface configuration method, the master card and the high-speed daughter card are applicable to the technical field of communication.

Owner:MAIPU COMM TECH CO LTD

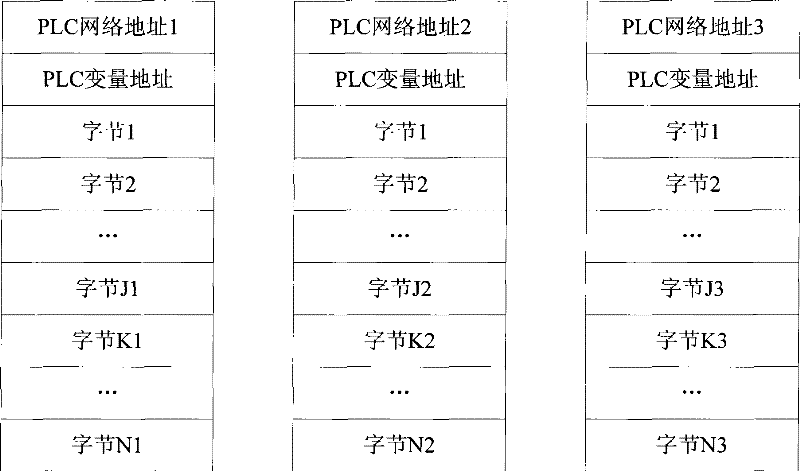

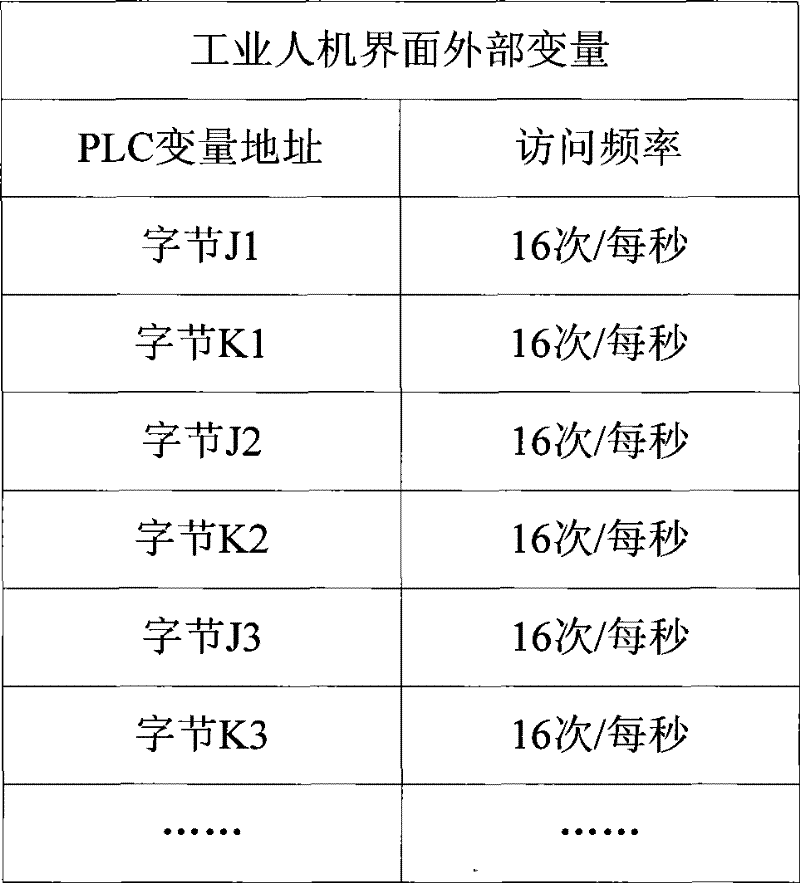

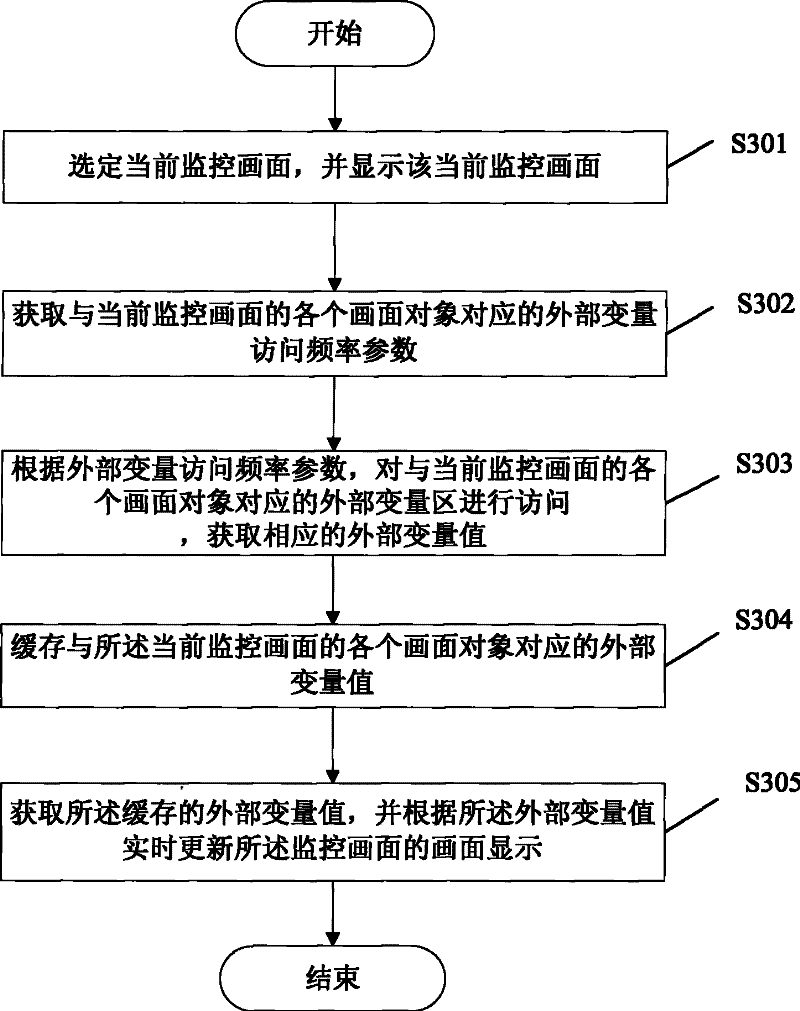

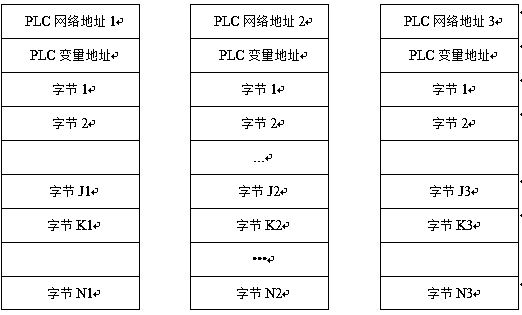

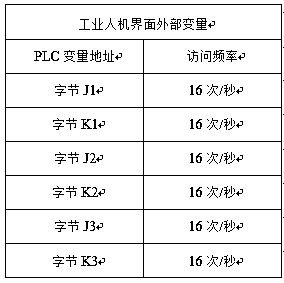

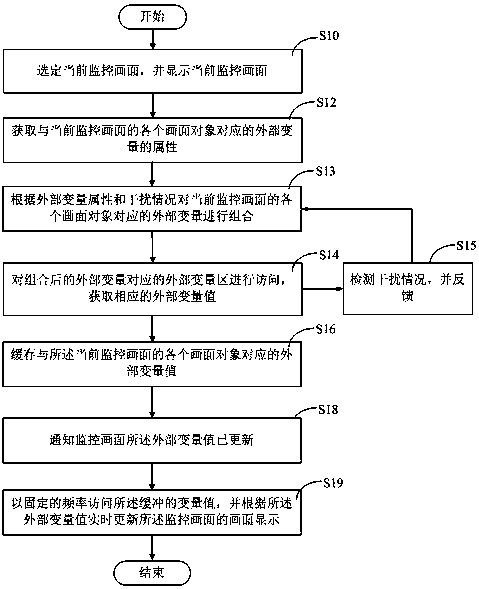

Industrial human-machine interface variable accessing method and system

InactiveCN101364088BReduce the number of visitsImprove access efficiencyComputer controlElectric programme controlHuman–machine interfaceAccess method

The invention discloses an industrial man-machine interface variable access method. The method comprises the following steps: selecting a current monitoring picture and displaying the current monitoring picture; extracting external variable access frequency parameters relative to the picture objects respectively in the current monitoring picture, visiting external variable regions corresponding to the picture objects respectively according to the external variable access frequency parameters and extracting relevant external variable values; storing the external variable values in a cache memory; and extracting an external variable value of the cache memory and updating the picture display of the monitoring picture in real time according to the external variable value. Accordingly, the invention also discloses an industrial man-machine interface variable access system. By adopting the technical proposals, the network resource is saved and the communication efficiency is increased.

Owner:深圳市合信自动化技术有限公司

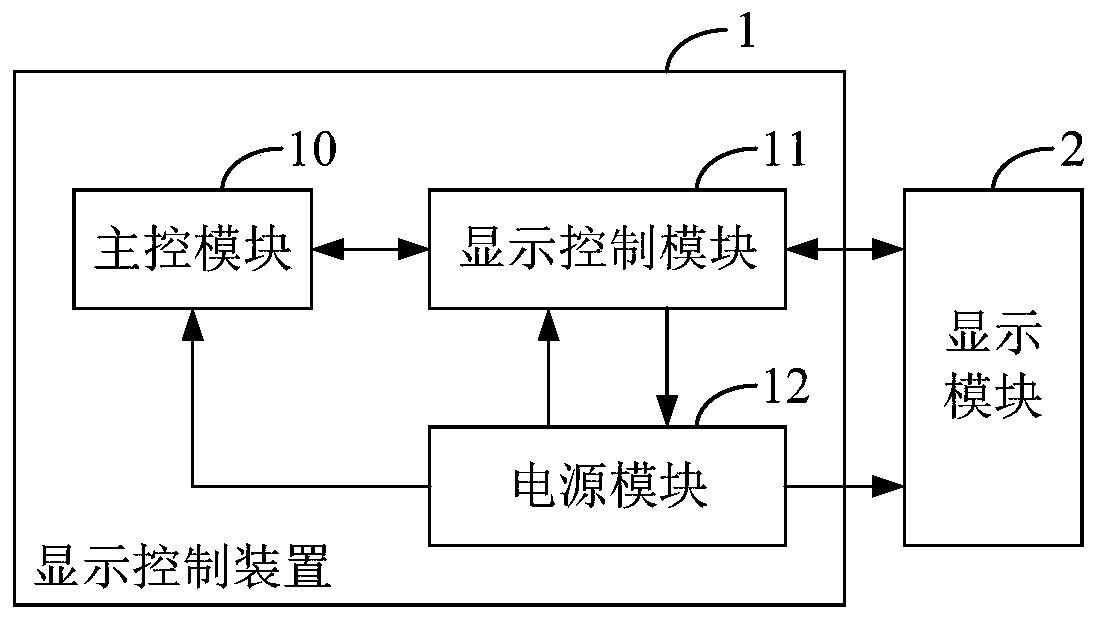

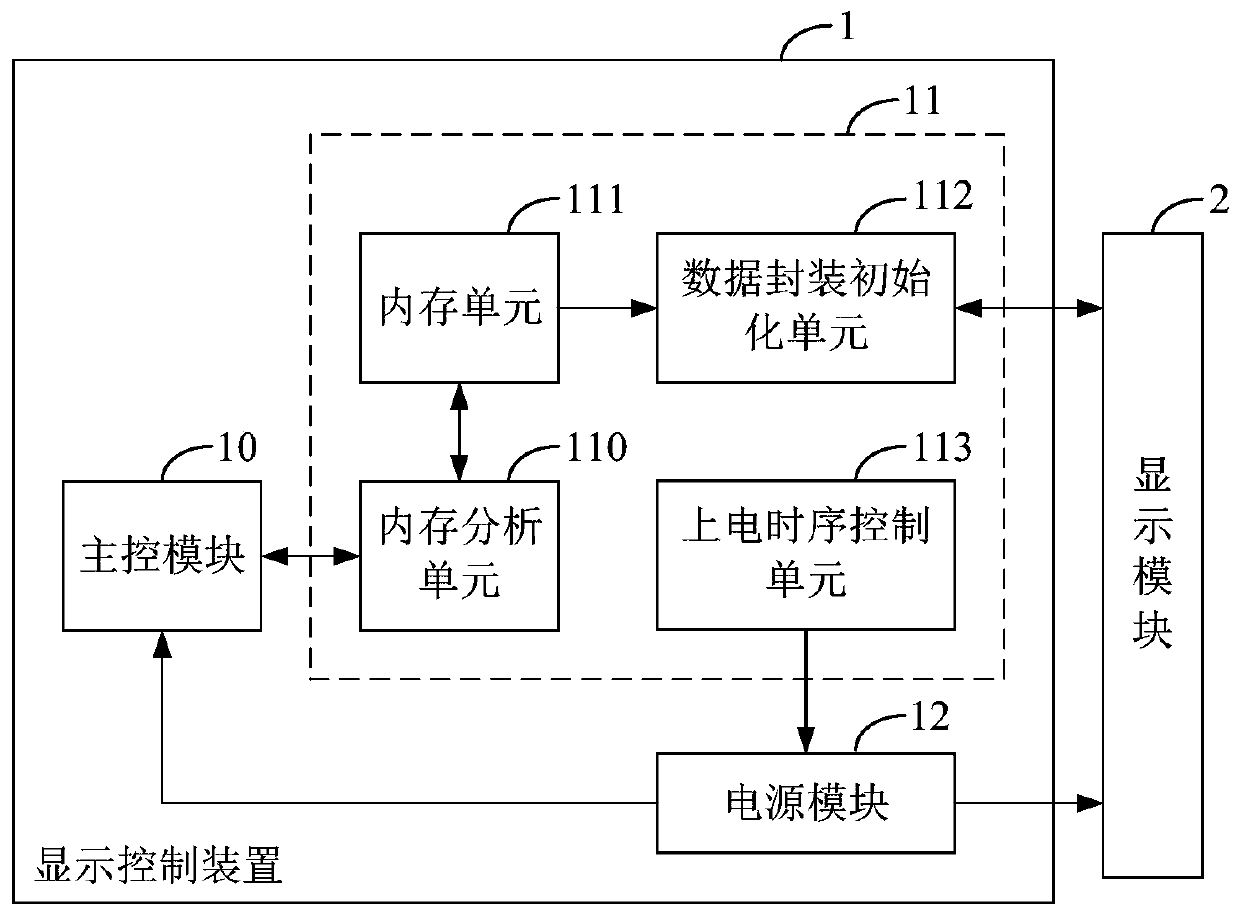

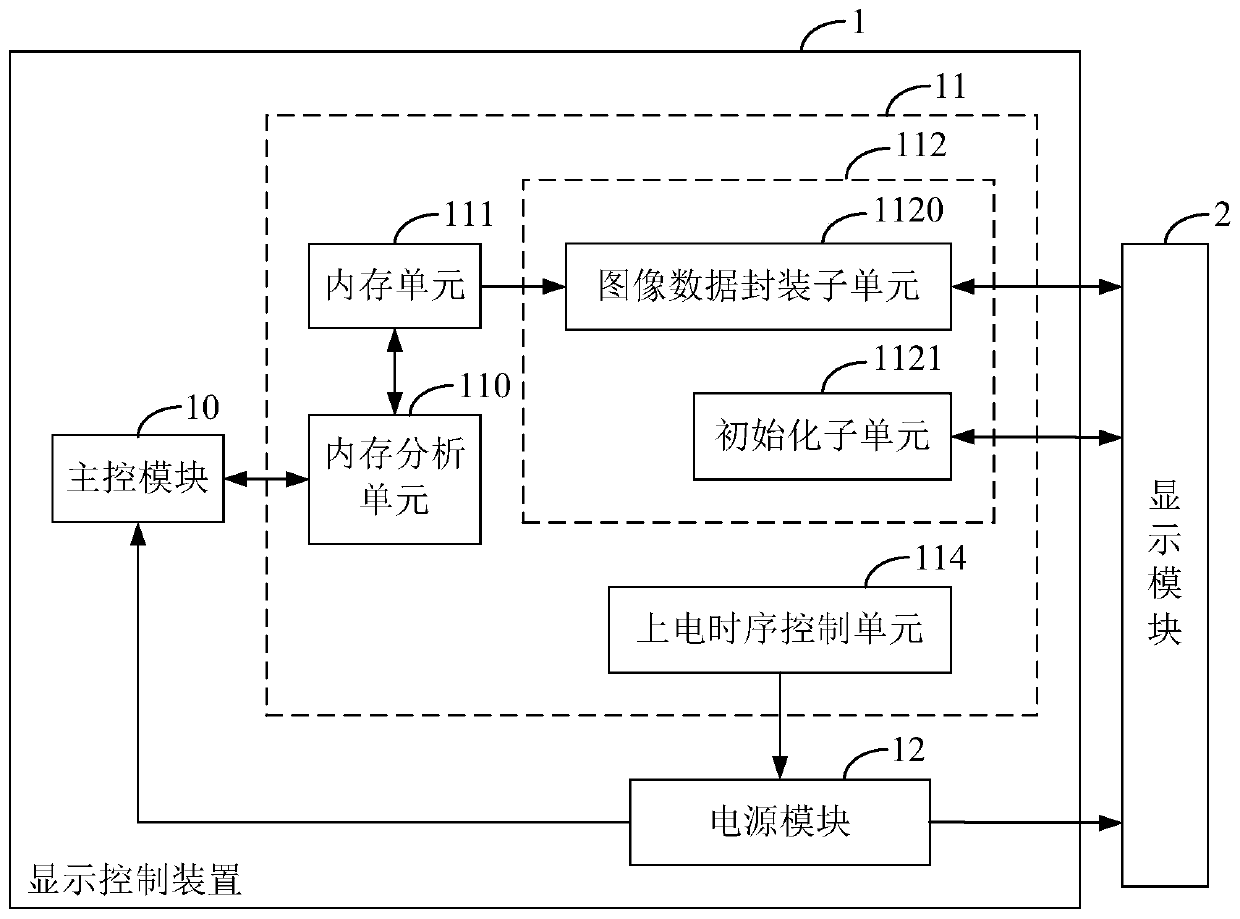

A kind of oled display screen and display control device thereof

ActiveCN106297655BSave bus resourcesImprove general performanceStatic indicating devicesElectricityCommunication interface

The present invention belongs to the image display technology field, and provides an OLED display screen and a display control device thereof. The display control device comprising a master control module, a display control module and a power module in the OLED display screen is employed; the display control module controls the power-on time sequence, the communication interface time sequence and the initialization process of the display module, the display control module performs buffer memory of the image data outputted by the master control module, after the power-on of the display module is completed, the image data is packaged as the corresponding OLED display data, and the OLED display data is outputted to the display module to allow the display module to display the OLED display data, and because the display control module employs a programmable logic controller which has strong interface resource, and therefore, different interface time sequences are configured for different display modules through the display control module, the development is simple, the versatility is high, and the bus resource of the master control module is saved.

Owner:深圳市华讯方舟光电技术有限公司

A kind of arbitration method and system of i2c bus

ActiveCN107766267BHigh speedAvoid long-term occupancyElectric digital data processingCommunication qualityEngineering

The invention provides an arbitration method and system of an I2C (Inter-Integrated Circuit) bus. According to both the method and system, control right of the I2C bus is allocated to a current main control device when the I2C bus is currently idle, and overall allocation on the bus control right of the above-mentioned current main control device is realized on the basis of received values, whichare of corresponding flag bits and currently fed back by a status register, when the I2C bus is not currently idle; and I2C bus communication status of each currently authorized main control device iscollected in real time, each time I2C bus communication ending of a corresponding currently-authorized main control device is determined, I2C bus control right of the corresponding currently-authorized main control device is taken back, and the above-mentioned status register is controlled to release the BUSY flag bit thereof, and the currently authorized main control device is a main control device with the currently allocated I2C bus control right. According to the method and system, free switching of the I2C bus control right under status of multiple main control devices can be realized, and a communication rate, communication stability and communication quality of the I2C bus are improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

An intelligent bus card swiping management system and method

InactiveCN104574654BShorten the timeSave moneyData processing applicationsCoded identity card or credit card actuationUser inputComputer module

The invention provides an intelligent bus card swiping management system and method. The intelligent bus card swiping management system comprises a card swiping machine module and bus card modules, wherein the card swiping machine module is mounted on a bus, and the bus card modules are used by users during bus taking; the card swiping machine module comprises a main controller, a card reader module, a memory module 1, a display module and a voice prompt module, and each bus card module comprises an IC (Integrated Circuit) card module, a controller, a memory module 2 and a human-machine interaction module. According to the system and the method, before bus taking, a user inputs a bus line or destination and selects to take the most reasonable bus; when the corresponding user gets on the bus and swipes the corresponding card, the card swiping machine module reads information from the corresponding IC card module, judges whether the line needed to be ridden by the corresponding user is consistent with that of the bus or not, prompts the corresponding user of wrong-bus taking with voice if the line needed to be ridden by the corresponding user is inconsistent with that of the bus, further judges whether the balance of the corresponding card of the corresponding user is sufficient or not if the line needed to be ridden by the corresponding user is consistent with that of the bus, prompts the corresponding user of insufficient balance if the balance of the corresponding card of the corresponding user is insufficient, and charges if the balance of the corresponding card of the corresponding user is sufficient; thus, unsuspecting waste caused the wrong-bus taking of the users can be avoided, the time and money of the users are saved, and meanwhile, bus resources are saved.

Owner:CHANGZHOU UNIV

Balloon catheter applied to oct endoscopic scanning imaging, usage method and oct imaging system

The invention relates to the technical field of medical devices, and provides a balloon catheter that can be used in conjunction with an endoscope and an OCT optical probe, an OCT imaging system and a use method. The balloon catheter includes a handle, a double-lumen tube, a balloon, an inner tube, and a soft head. To ensure the concentricity of the inner tube and the balloon, it is convenient for optical imaging.

Owner:MICRO TECH (NANJING) CO LTD

Method for converting data between interface of parallel processor and AHB interface of AMBA in RISC system

ActiveCN100592274CSave bus resourcesImprove transmission efficiencyElectric digital data processingGeneral purposeMicrocontroller

The invention relates to a method for switching data between an AHB interface of AMBA and a parallel processor interface in an RISC system, which comprises the following steps: data switching group quantity in a single operation between a high-grade high-speed bus interface of a high-grade microcontroller bus framework and a general-purpose parallel microprocessor interface is determined, data transmitted by the high-grade high-speed bus of the high-grade microcontroller bus framework are switched into grouped data at the general-purpose parallel microprocessor interface according to the dataswitching group quantity, and the grouped data are transmitted by the general-purpose parallel microprocessor interface. With the adoption of the method for switching data between the AHB interface ofAMBA and the parallel processor interface in an RISC system, the operation of data switching and transmission can be finished in a single operation by the AHB interface of the AMBA, thus greatly saving AMBA AHB bus resources of RM and effectively improving the transmission efficiency of data switching between interfaces. In addition, the method for switching data between the AHB interface of AMBAand the parallel processor interface in the RISC system is convenient and rapid in use, and has stable and reliable work performance and wider application scope.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

Discrete cosine transform (DCT)-inverse discrete cosine transform (IDCT) coprocessor suitable for system on chip (SOC)

InactiveCN101794276BFast operationReduce the numberDigital computer detailsComplex mathematical operationsComputer architectureCoprocessor

Owner:东莞润风电子科技有限公司

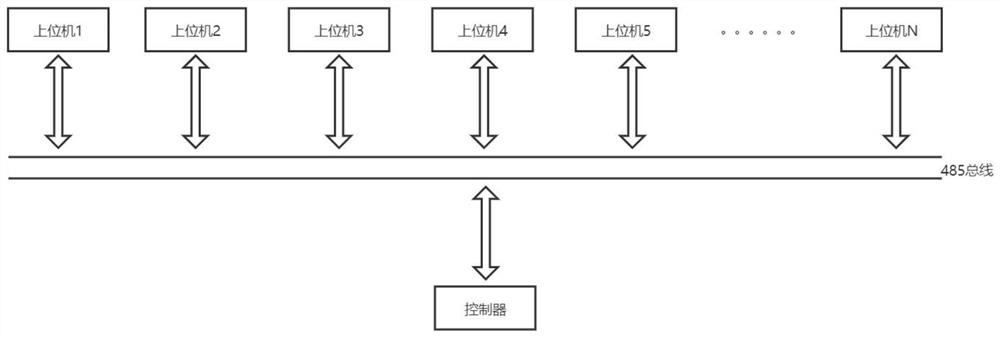

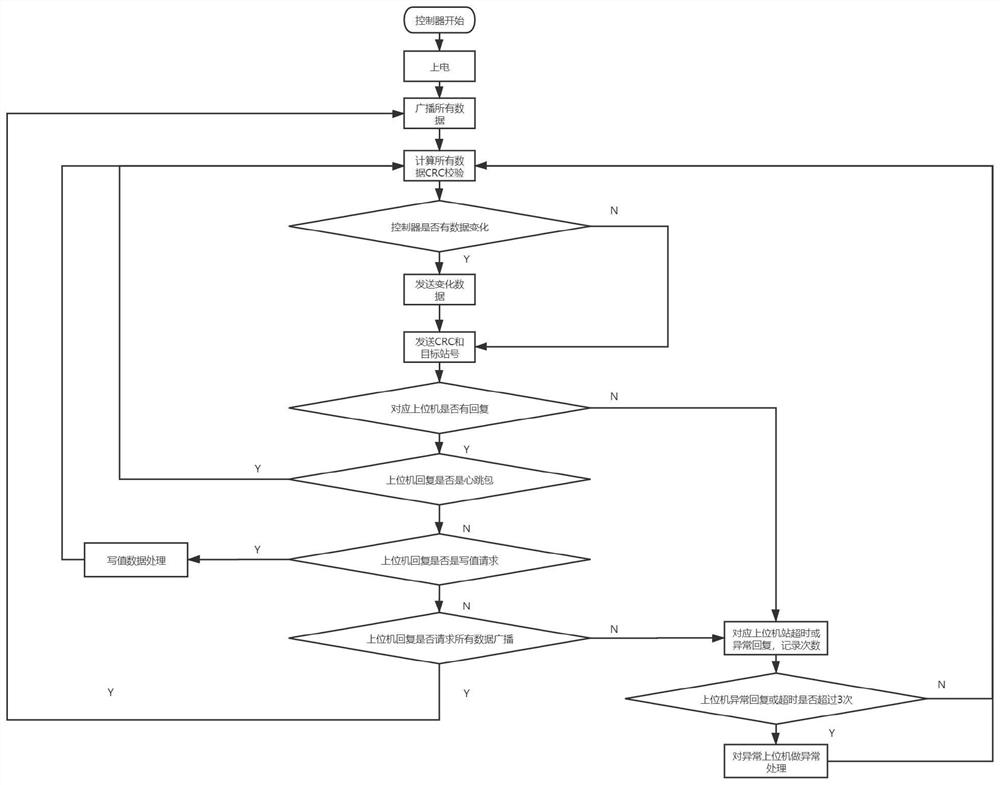

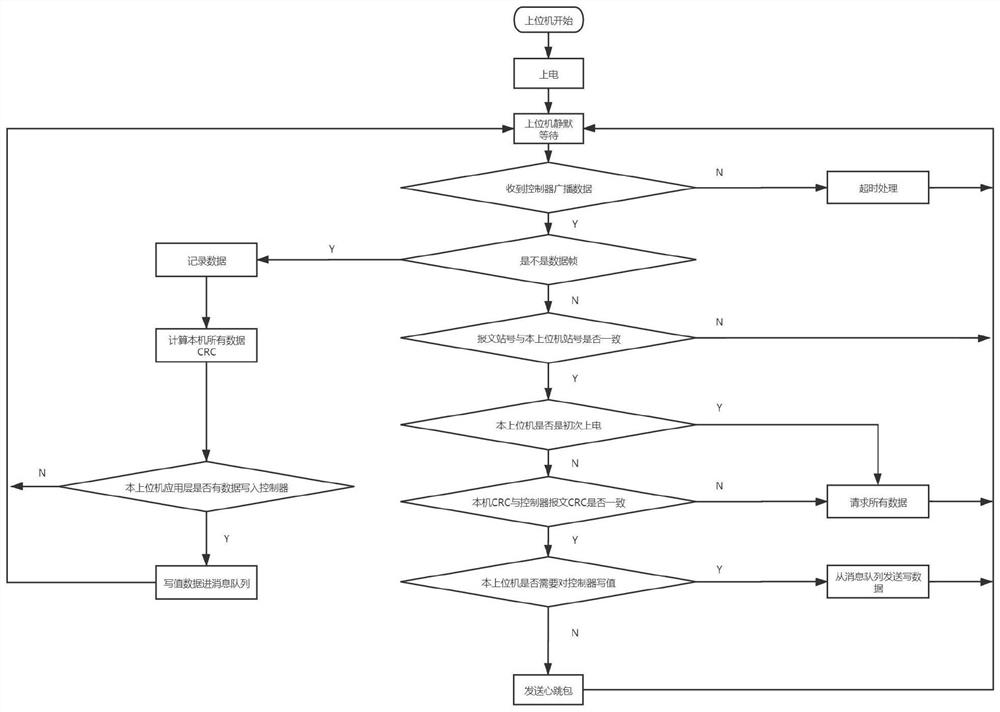

Rapid communication structure and rapid communication method for multiple upper computers and controller based on RS485 bus

ActiveCN114244753AShorten the timeSave bus resourcesForward error control useBus networksComputer hardwareMessage queue

The invention relates to the field of industrial communication, and discloses a rapid communication structure and a rapid communication method for multiple upper computers and controllers based on an RS485 bus, the controllers are powered on for the first time, data are sent to the upper computers in a broadcast mode, the data are transmitted in one step, and the time for polling the controllers one by one by the upper computers is saved; in the subsequent operation process, the controller only broadcasts changed data, and a large number of bus resources occupied by unchanged data communication are saved; meanwhile, the controller can respond to a request command and a value writing command of the upper computer to all data, and value writing of the upper computer adopts a message queue to ensure that the value writing command is not lost; most importantly, the controller and the upper computer respectively carry out CRC verification on all data of the computer, if the data are not consistent, the controller broadcasts all data again, and the consistency of the data of the controller and the upper computer is ensured. By using the communication method, on the premise of ensuring the data consistency, the communication speed of the upper computers and the controller can be greatly improved, and the more the upper computers are, the more obvious the effect is.

Owner:上海繁易信息科技股份有限公司

A novel industrial man-machine interface variable access method and system

ActiveCN105892432BReduce the number of visitsImprove access efficiencyTotal factory controlProgramme total factory controlReal variableAccess method

The invention discloses a novel industrial human-computer interface variable access method, comprising the steps of selecting and displaying the current monitored picture; acquiring external variable access frequency parameters corresponding to picture objects of the current monitored picture; detecting interference of external variable areas corresponding to the picture objects of the current monitored picture, and combining external variables corresponding to the picture objects of the current monitored picture according to the interference; accessing the external variable areas after the picture objects of the current monitored picture are correspondingly combined according to the external variable access frequency parameters to acquire corresponding external variable values, and caching the variable values corresponding to the picture objects of the current monitored picture; when updated variable values are determined, notifying the monitored picture that the external variable values have been updated; acquiring the updated external variable values among the external variable values corresponding to the picture objects of the current monitored picture, and updating the picture display of a display module in real time according to the updated external variable values. The invention further discloses a corresponding system. By adopting the method and the system, network resources can be saved, the communication efficiency can be improved, and interference can be prevented.

Owner:深圳市合信自动化技术有限公司 +1

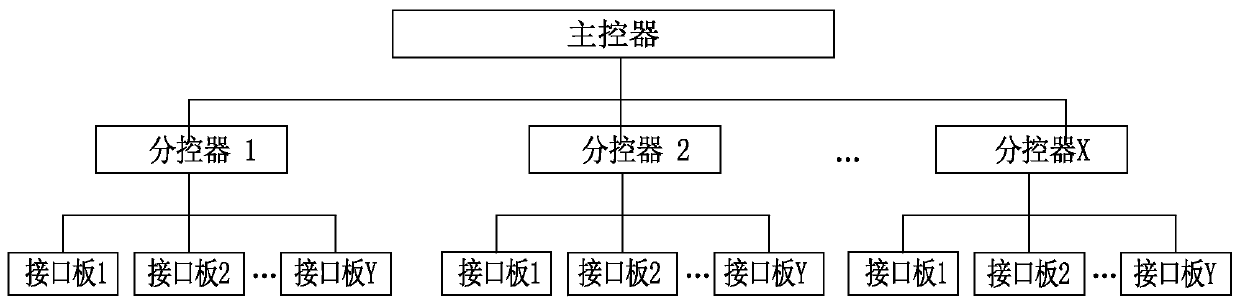

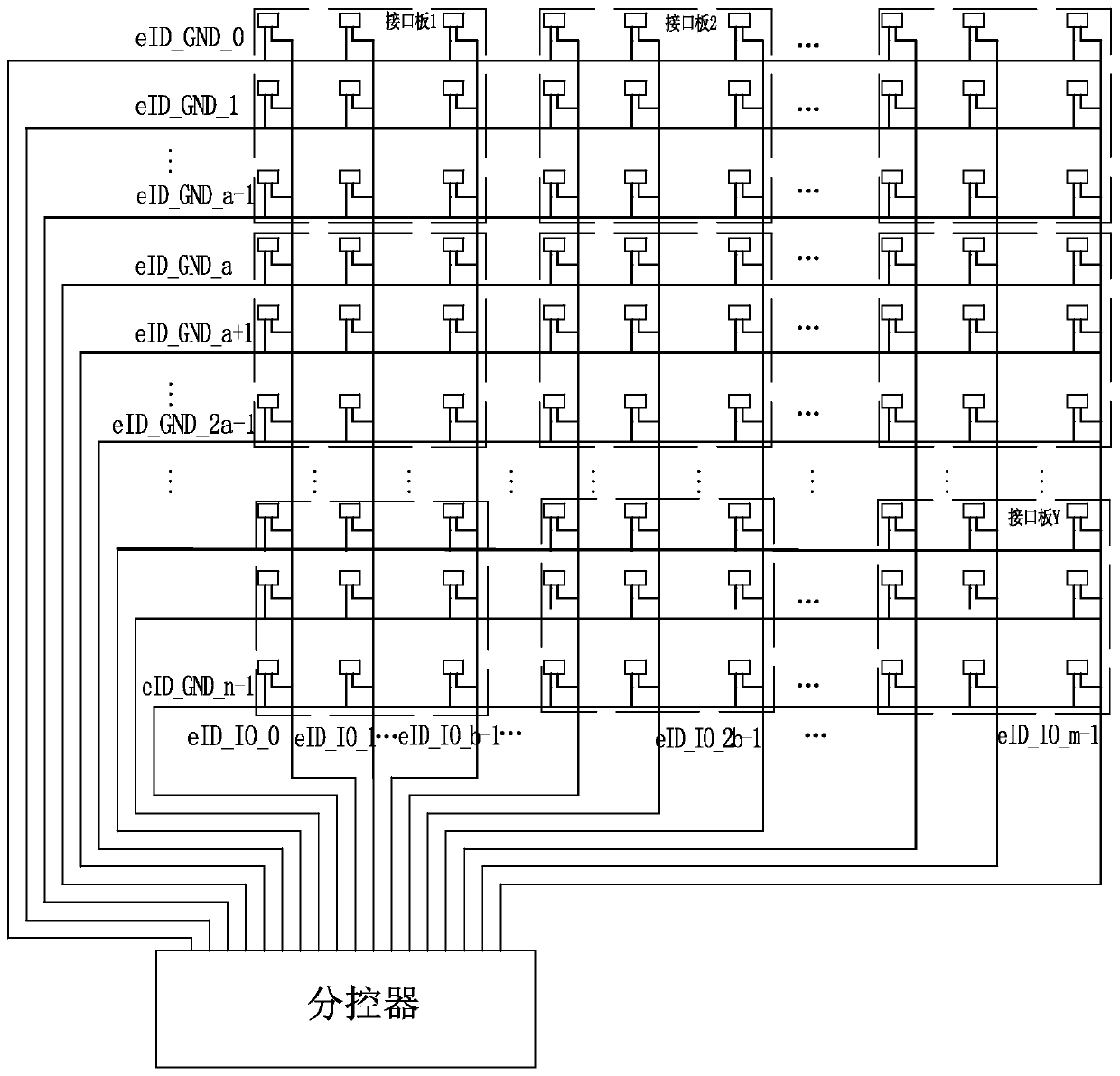

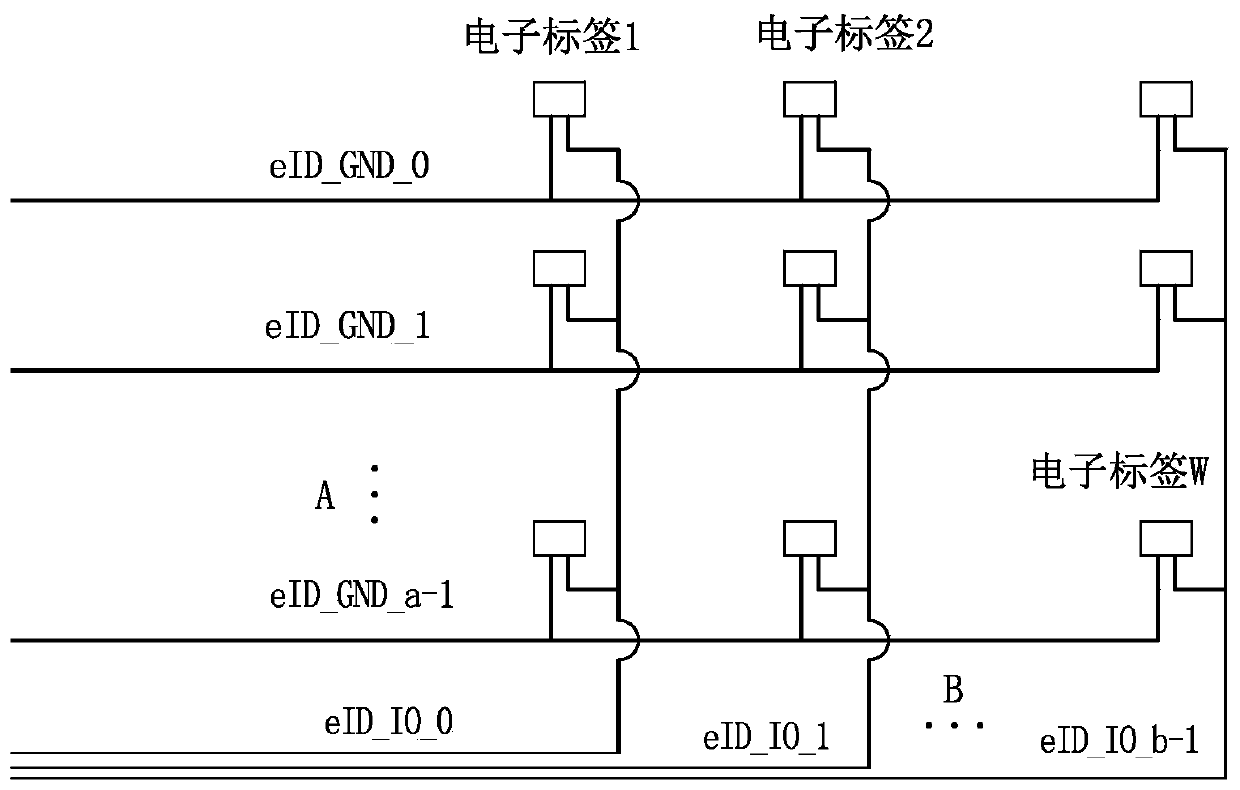

Nested matrix-based electronic tag reading system and a reading method thereof

PendingCN109829347AHigh data efficiencyImprove real-time performanceEnergy efficient computingElectric digital data processingData efficiencyLow power dissipation

The invention relates to an electronic tag reading system based on a nested matrix, which is characterized in that a main controller is connected with a plurality of sub-controllers, the main controller is used for commanding each sub-controller to simultaneously acquire, upload and display data of an electronic tag, and each sub-controller is respectively connected with a respective correspondinginterface board unit through a data bus; Each interface board unit is provided with a plurality of interface boards arranged in a matrix mode, and each interface board is connected with a plurality of electronic tags arranged in a matrix mode. The sub-control MCU of each sub-controller is provided with a plurality of transverse and longitudinal GPIO buses; Each transverse GPIO bus is connected with the grounding pins of the electronic tags in the same row on the corresponding interface board in the same row, and each longitudinal GPIO bus is connected with the IO pins of the electronic tags in the same column on the corresponding interface board in the same column to form a matrix bus control structure. Bus resources can be greatly saved, power consumption and cost are effectively reduced, physical delay is reduced, and the data reading efficiency and accuracy of the electronic tag and the system stability are improved.

Owner:CHANGZHOU TAIPING COMM SCI & TECH

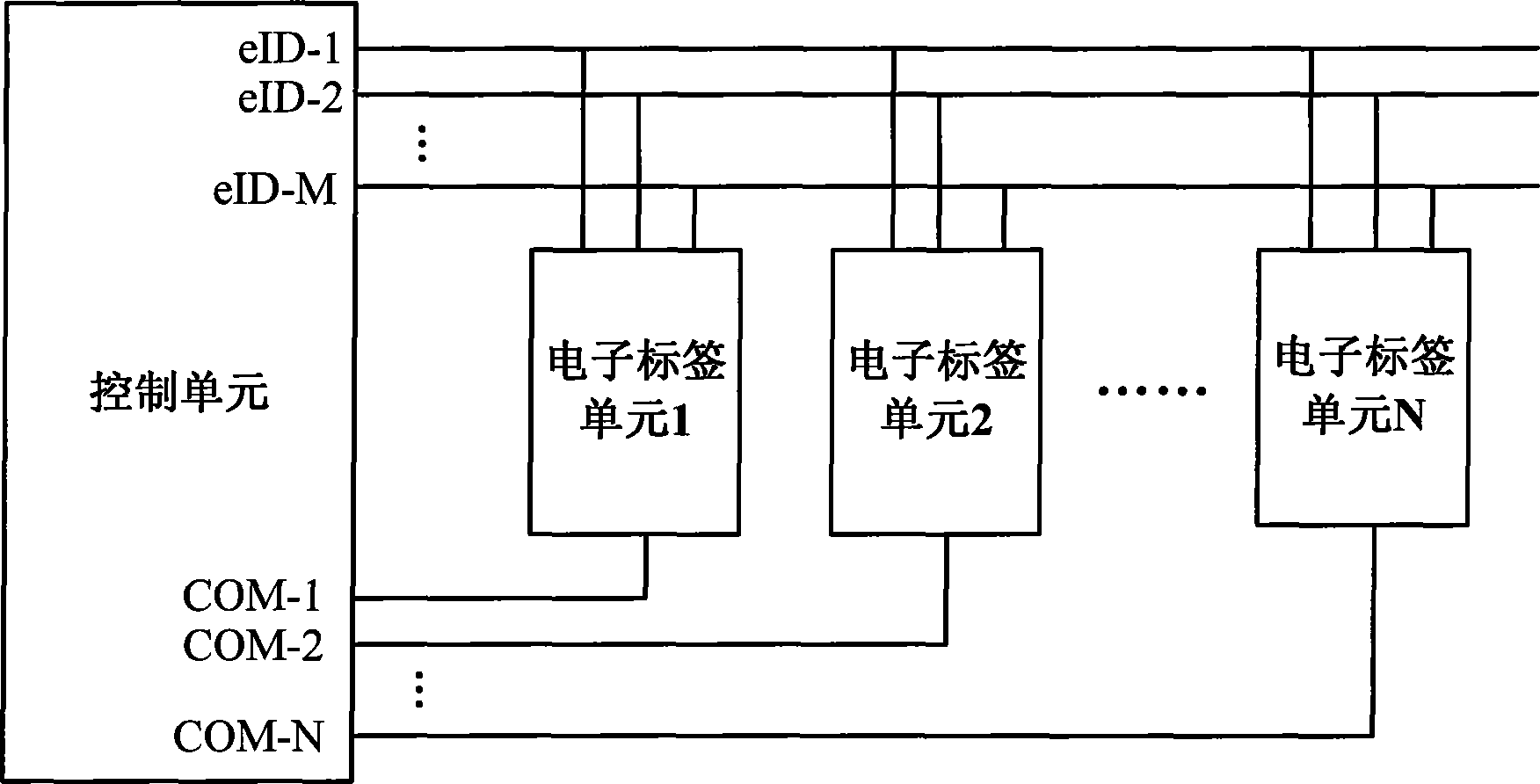

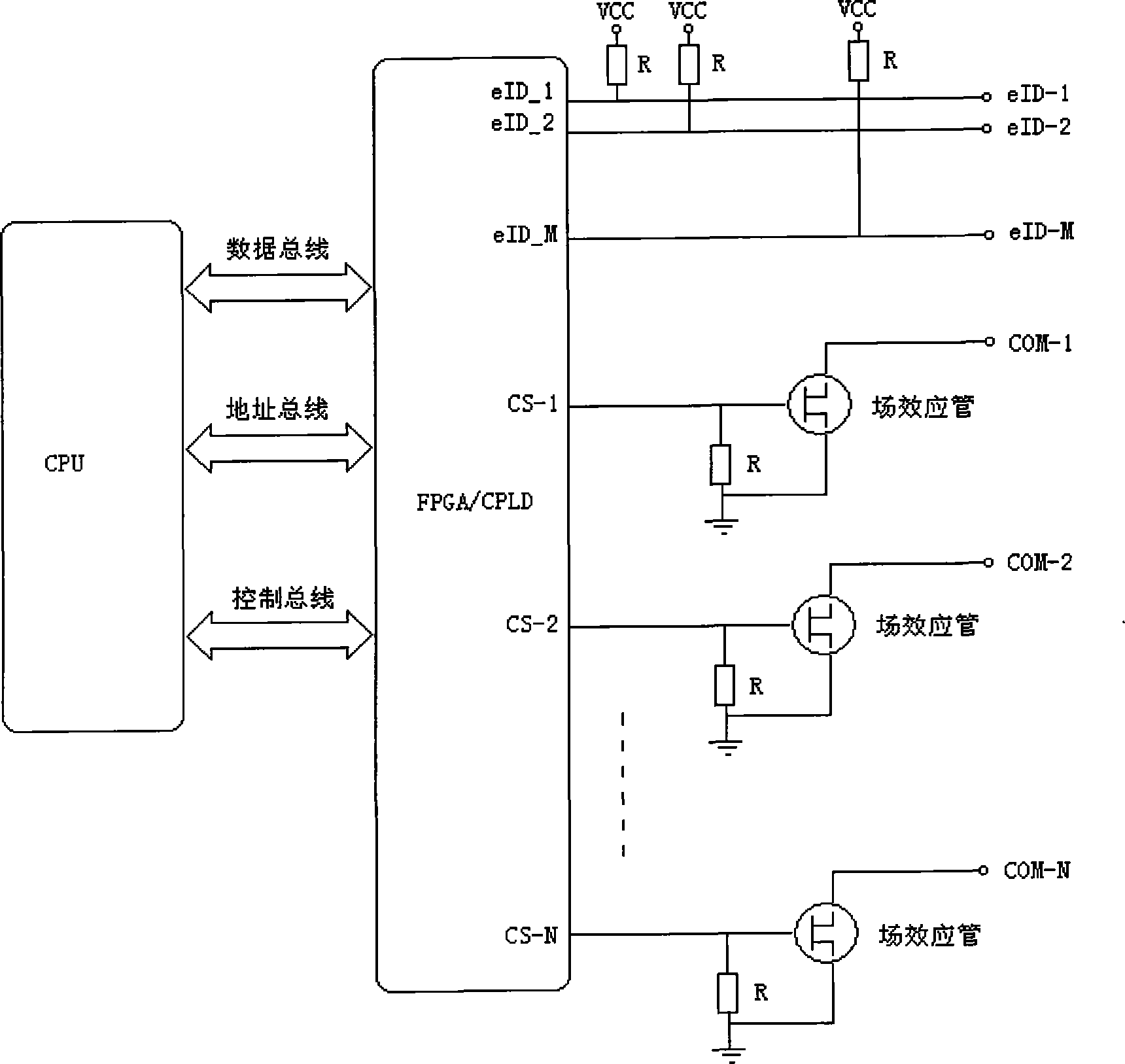

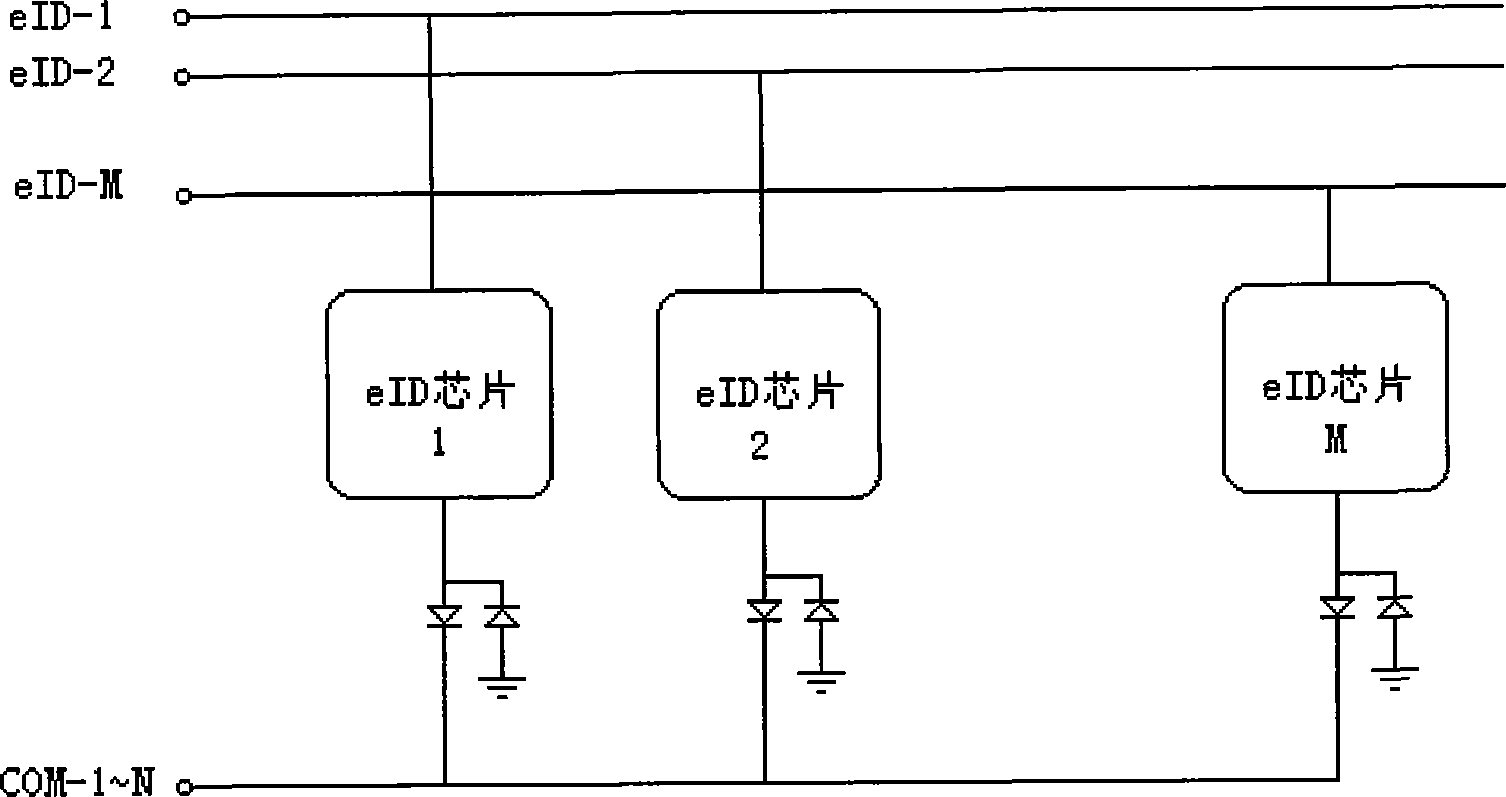

A matrix eid bus circuit

ActiveCN102761793BSave bus resourcesRead without errorMultiplex system selection arrangementsBus networksControl busEmbedded system

The invention closes a matrix eID bus circuit which comprises a control unit and a plurality of electric tag units, wherein data buses eID-1, eID-2,... and eID-M led out from the control unit are respectively connected with I / O ports of 1-M eID chips respectively on electric tag units from 1-N, so as to form a transverse bus frame, wherein the M as well as the N is an integer larger than 2; and control buses COM-1,COM-2... And COM-N led out form the control unit are respectively with grounded terminals of the 1-M eID chips respectively on electric tag units from 1-N, so as to form a longitudinal bus frame; and the transverse bus frame and the longitudinal bus frame together form the matrix eID bus circuit. According to the invention, the bus resource is saved, hundreds of eID chips can be accurately read at the same time, and the number of the eID chips on one bus is not limited.

Owner:FENGHUO COMM SCI & TECH CO LTD

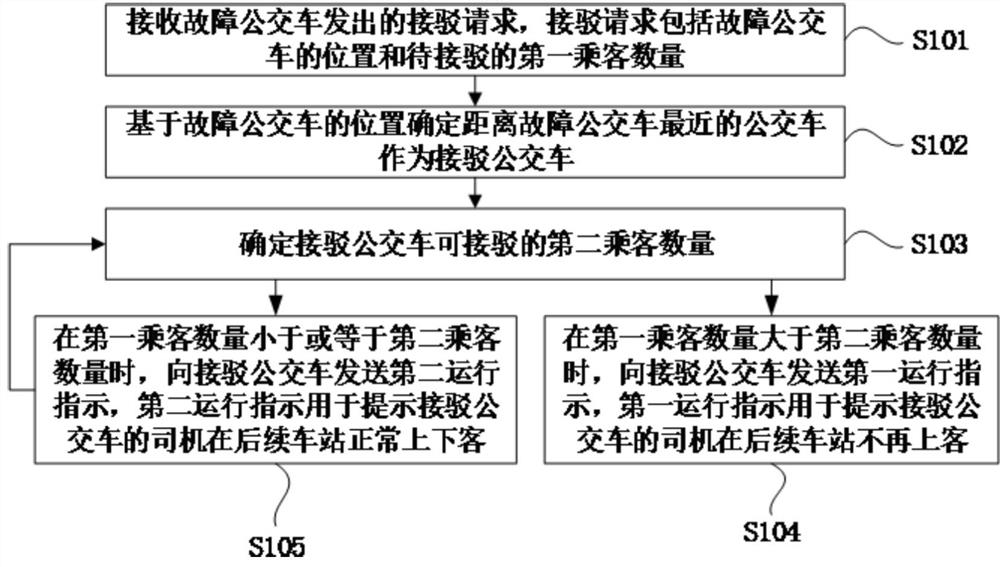

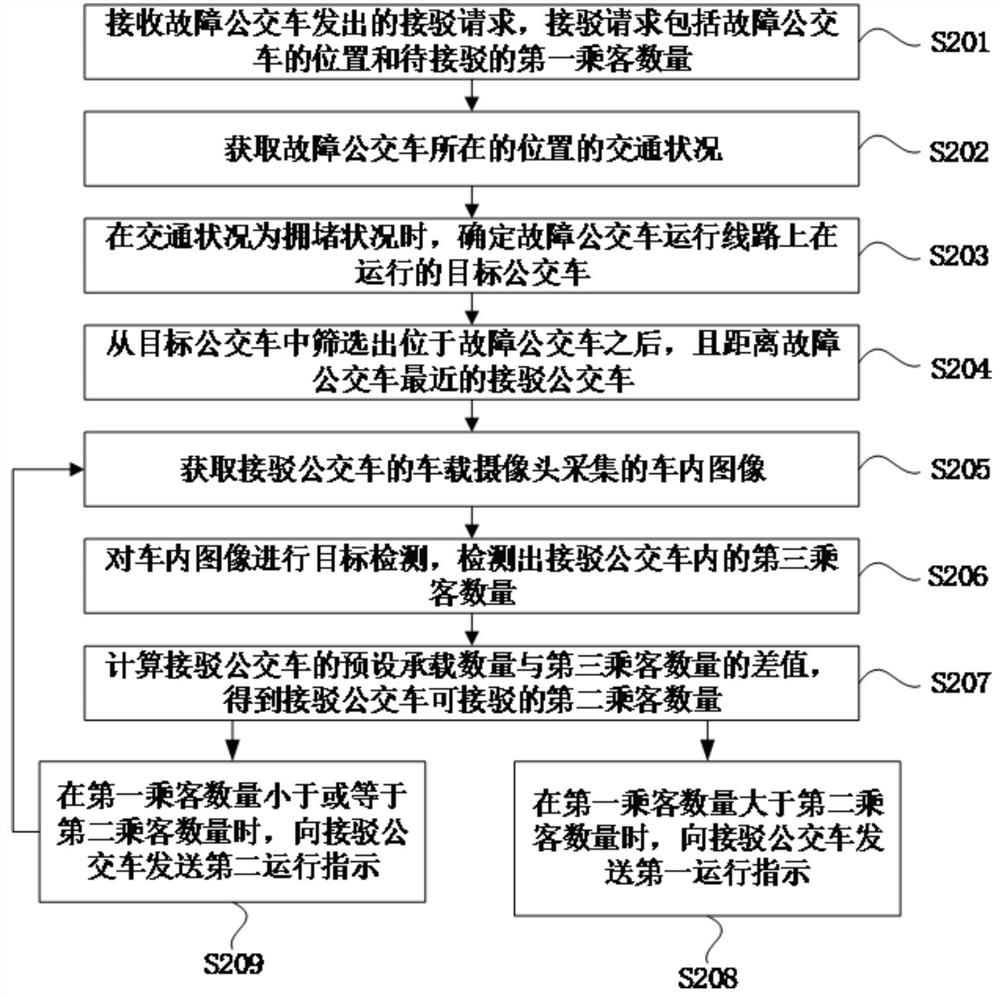

Bus fault connection method and device, equipment and storage medium

PendingCN113962582AReduce waiting timeAvoid congestionOffice automationResourcesEngineeringTraffic crash

The invention discloses a bus fault connection method and device, equipment and a storage medium. According to the invention, the nearest bus located behind a fault bus on the same running route is used as the connection bus for receiving passengers, so that the waiting time of the passengers to be received is shortened, the risk of congestion or traffic accidents caused by long-time waiting of the passengers to be received on the roadside is avoided; meanwhile, there is no need to specially dispatch an empty bus does for connection, and bus resources are saved. Besides, it can be guaranteed that enough space is always reserved in a connection bus to contain all or most passengers to be received; the risk that due to the fact that the bearing space of a connection bus is insufficient, redundant passengers wait on the roadside for a long time, and consequently congestion or traffic accidents are caused is avoided, and safety is improved.

Owner:GUANGZHOU TONGDA AUTO ELECTRIC +1

A dsp debugging device

InactiveCN103309798BImprove real-time performanceImprove throughputSoftware testing/debuggingData transmissionThroughput

Owner:SHANGHAI JIAOTONG UNIV +1

Multi-core processor

InactiveCN101882127BIt is not easy to change the numberImprove scalabilityMultiple digital computer combinationsMulti-core processorVery long instruction word

Owner:HUNAN UNIV

Optimizing Method of Bus Line Network Based on Accessibility and Accessibility Strength

InactiveCN104966135BReduce operating costsImprove accessibilityGenetic modelsForecastingReachabilityGenetic algorithm

The invention discloses a bus line network optimization method based on accessibility and reachability strength; it comprises the following steps: obtaining the basic data for optimizing the bus line network and using the bus line network as an initial bus line network, and calculating the initial bus line network The objective function value is calculated by genetic algorithm to obtain the optimal bus line network. The invention can improve the accessibility of the line network on the basis of satisfying the original travel demand service, realize the maximum matching between the reachable intensity and the travel intensity, minimize the bus operation cost, and save bus resources.

Owner:SOUTHWEST JIAOTONG UNIV

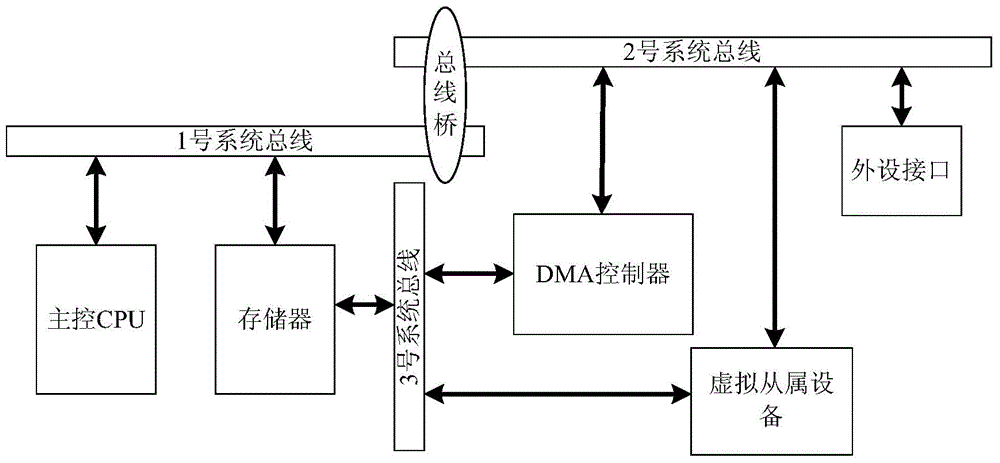

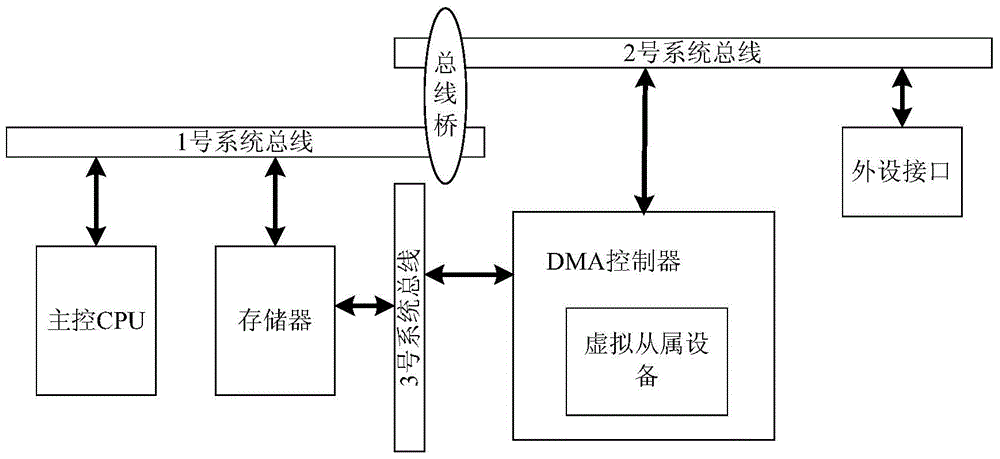

DMA-based real-time streaming data transmission system and method

ActiveCN103678205BSave resourcesAchieve readElectric digital data processingStreaming dataDirect memory access

The invention relates to a direct memory access (DMA)-based real-time streaming data transfer system and a DMA-based real-time streaming data transfer method. The transfer system comprises a master control central processing unit (CPU), a DMA controller, a storage, a system bus, a peripheral interface and a virtual slave unit, wherein the DMA controller controls the real-time data transfer between the storage and the peripheral interface through the system bus; the DMA controller can read default padding data from the virtual slave unit to pad streaming data output by the storage, also can write streaming data which is required to be discarded and input externally into the virtual slave unit to match the DMA controller to pad or discard the streaming data in the real-time streaming data transfer process; the virtual slave unit realizes single-period write and read on the system bus, the speed is higher, and the bus resource is saved; moreover, the virtual slave unit does not occupy storage resource, the default padding data can be configured, and the storage resource is saved.

Owner:HANGZHOU SILAN MICROELECTRONICS

High-precision clock synchronization method and system for communication equipment

ActiveCN109818701BHigh synchronization accuracyEliminate the effects ofSynchronisation arrangementTime-division multiplexClock phaseEmbedded system

The invention discloses a high-precision clock synchronization method and system for communication equipment, and relates to the field of clock synchronization. The steps of the method include: the clock unit of the communication device sends the transmission delay value to the service disk, and the transmission delay value sends a signal according to the clock sent by the clock unit to the service disk, and the clock of the clock signal uploaded to the clock unit by the service disk The phase difference is obtained; after the service disk performs phase compensation on the clock transmission signal according to the transmission delay value, a clock signal basically consistent with the clock phase of the clock transmission signal is formed. After the invention performs phase compensation on the clock signal by receiving and transmitting the time delay value, the compensated clock signal can be aligned with the output phase of the clock sending signal, thereby eliminating the problem caused by the transmission time delay of the clock signal in the prior art. Influence, and then greatly improve the clock synchronization accuracy.

Owner:FENGHUO COMM SCI & TECH CO LTD