DSP (Digital Signal Processor) debugging device

A test system and interface technology, applied in the field of DSP debugging devices, can solve problems such as poor real-time performance, occupation of bus resources, and reduced debugging communication rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

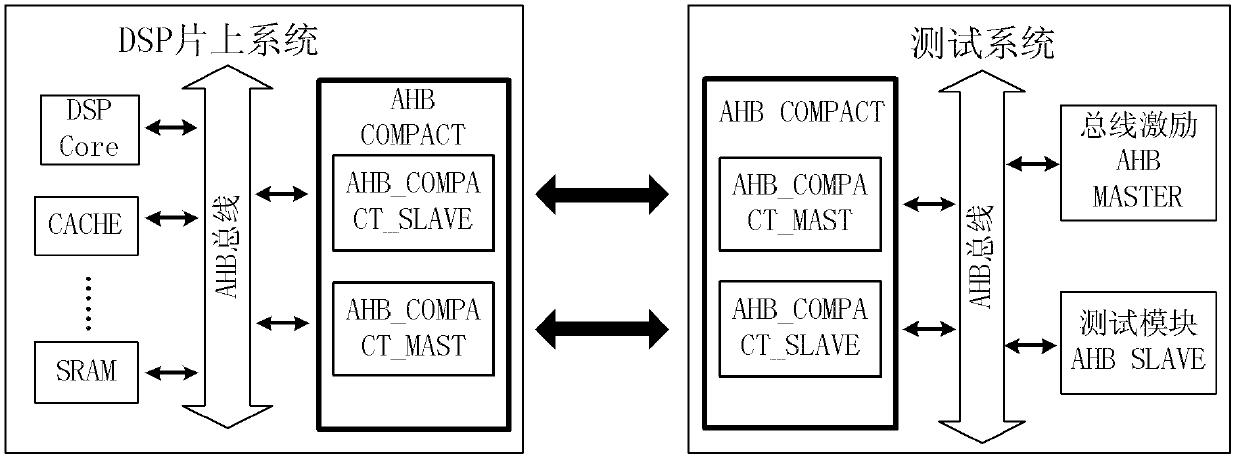

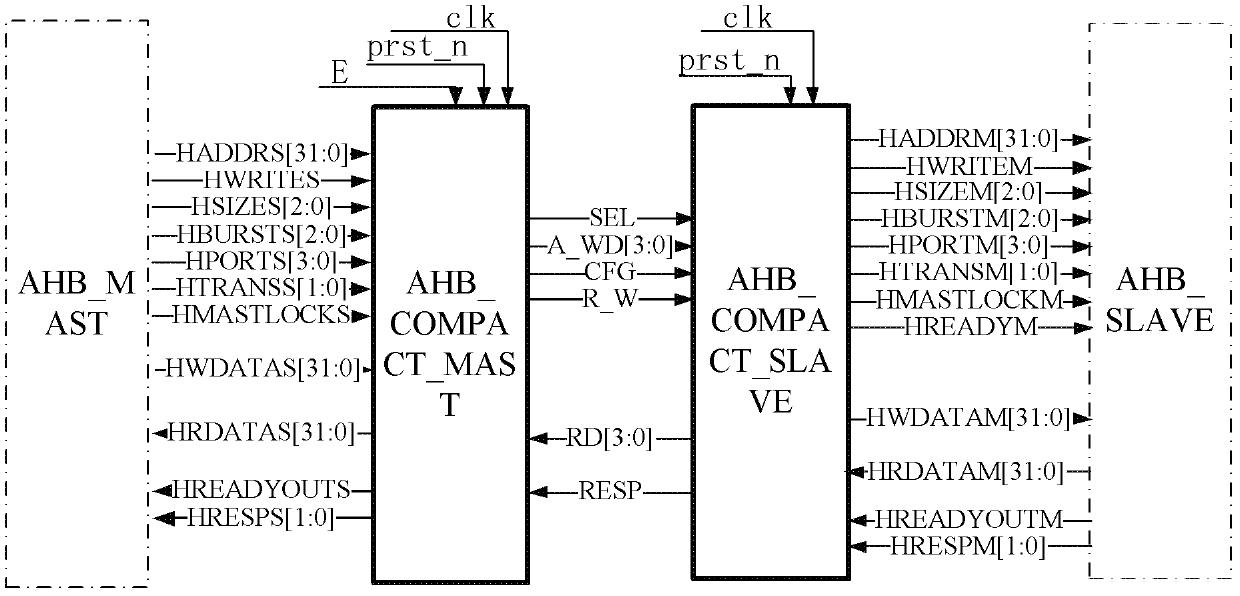

[0075] A kind of DSP debugging device provided by the invention (such as figure 1 The AHB_COMPACT module shown in ) mainly includes two submodules AHB_COMPACT_MAST and AHB_COMPACT_SLAVE, respectively having an AHB interface and an AHB_COMPACT interface, and the position of the DSP debugging device in the DSP debugging system is as follows figure 1 shown. The IP modules in the DSP system-on-chip are interconnected through the AHB on-chip bus, and the AHB_COMPACT module is mounted on the AHB bus as an IP module, and communicates with the off-chip debugging system through the simplified AHB_COMPACT interface. The off-chip test system also needs to include the AHB_COMPACT module to convert the AHB_COMPACT interface signal into an AHB interface signal in reverse. Thus, the bus stimulus module AHB MSATER in the test system can input stimulus signals into the DSP system-on-chip through the AHB_COMPACT_SLAVE interface of the DSP system-on-chip, or read the data that needs to be obser...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More