A dsp debugging device

A test system and address technology, applied in software testing/debugging, instrumentation, electrical digital data processing, etc., can solve problems such as system difficulties, occupation of bus resources, and many pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

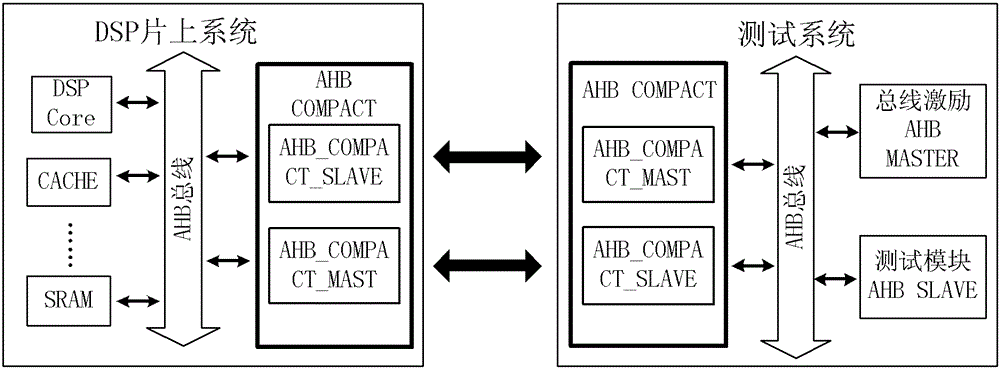

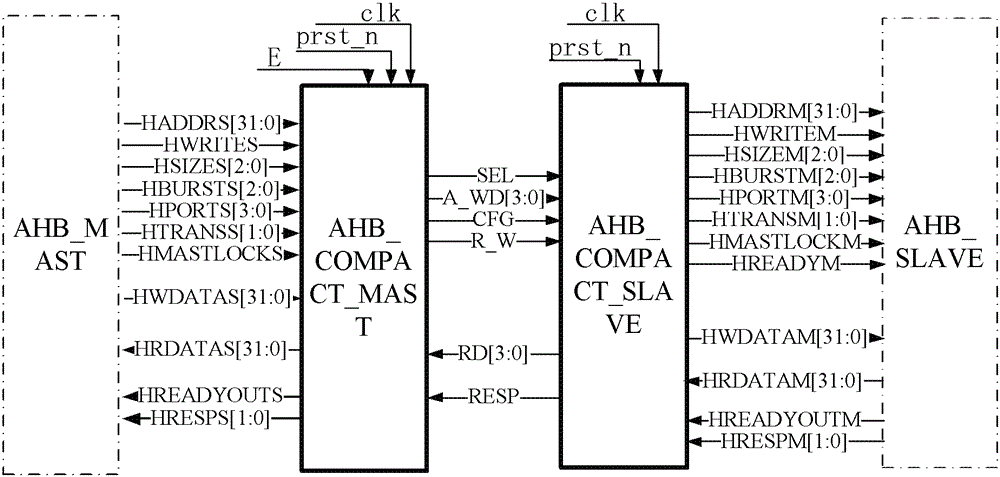

[0075] A kind of DSP debugging device provided by the invention (such as figure 1 The AHB_COMPACT module shown in ) mainly includes two submodules AHB_COMPACT_MAST and AHB_COMPACT_SLAVE, respectively having an AHB interface and an AHB_COMPACT interface, and the position of the DSP debugging device in the DSP debugging system is as follows figure 1 shown. The IP modules in the DSP system-on-chip are interconnected through the AHB on-chip bus, and the AHB_COMPACT module is mounted on the AHB bus as an IP module, and communicates with the off-chip debugging system through the simplified AHB_COMPACT interface. The off-chip test system also needs to include the AHB_COMPACT module to convert the AHB_COMPACT interface signal into an AHB interface signal in reverse. Therefore, the bus excitation module AHBMSATER in the test system can input the excitation signal to the DSP system on chip through the AHB_COMPACT_SLAVE interface of the DSP system on chip, or read the data that needs to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More