Discrete cosine transform (DCT)-inverse discrete cosine transform (IDCT) coprocessor suitable for system on chip (SOC)

A technology of coprocessor and status register, which is applied in the direction of electrical digital data processing, instruments, complex mathematical operations, etc., to achieve the effect of reducing chip area, increasing speed, and saving bus resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

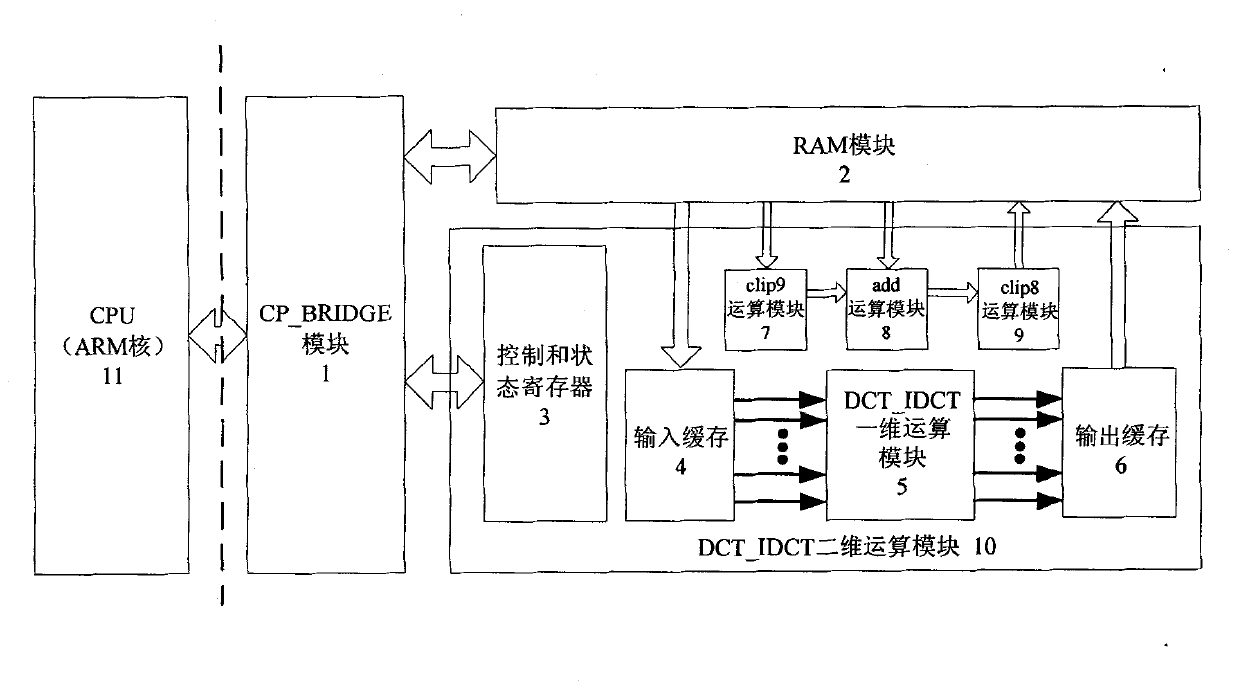

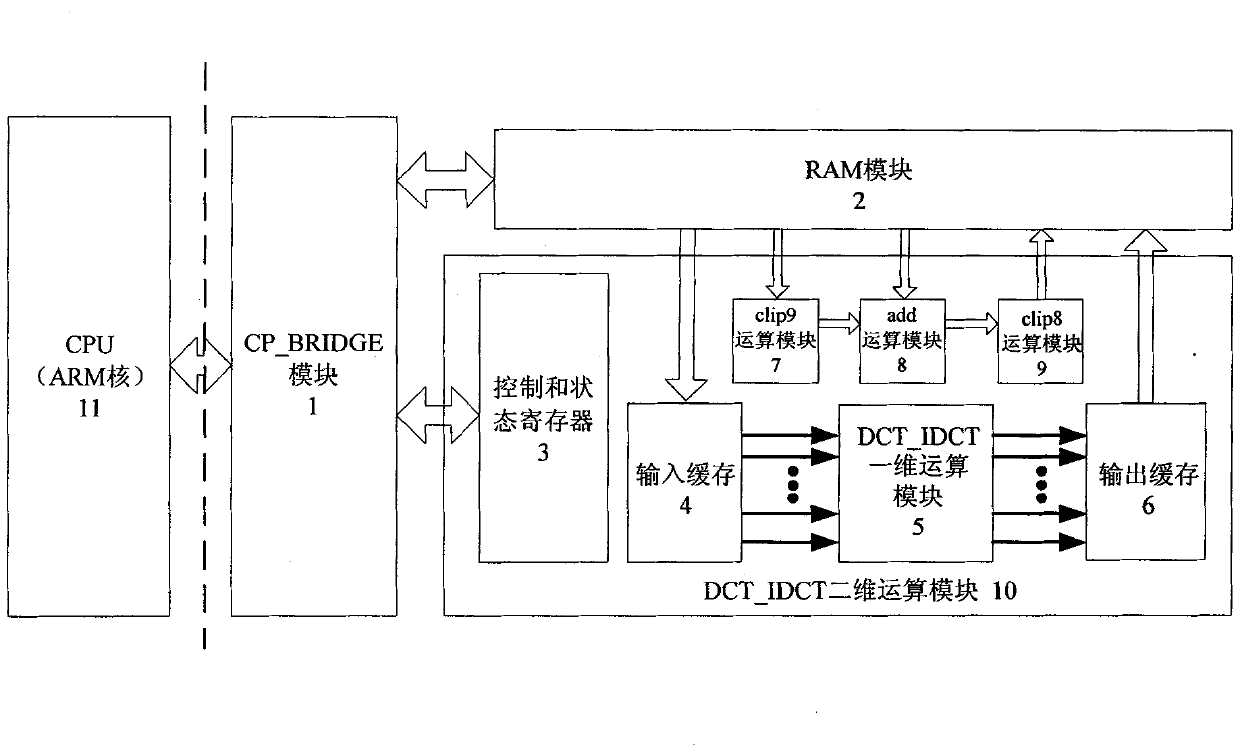

[0026] The present invention will be specifically described through embodiments below in conjunction with the accompanying drawings.

[0027] Before the DCT_IDCT operation, the CPU usually needs to pass parameters to the DCT_IDCT coprocessor, and then load the data through the LDC instruction. When the data is loaded, the coprocessor starts the operation; when the operation is over, the coprocessor stores the result of the operation in its In the internal RAM module, when the CPU knows the completion of the operation through polling, the CPU reads out the operation result through the STC instruction.

[0028] It can be seen that the efficiency of the DCT_IDCT acceleration algorithm depends on the following three items: 1. The speed at which the CPU loads data into the coprocessor; 2. The speed at which the coprocessor operates; speed.

[0029] Because the 1st, 3rd items are realized by LDC and STC instructions, the speed that these two instructions are carried out generally c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More