Linear feedback shift register (LFSR)-based random test device for external storage interface

A technology for random testing and external storage, used in static memory, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

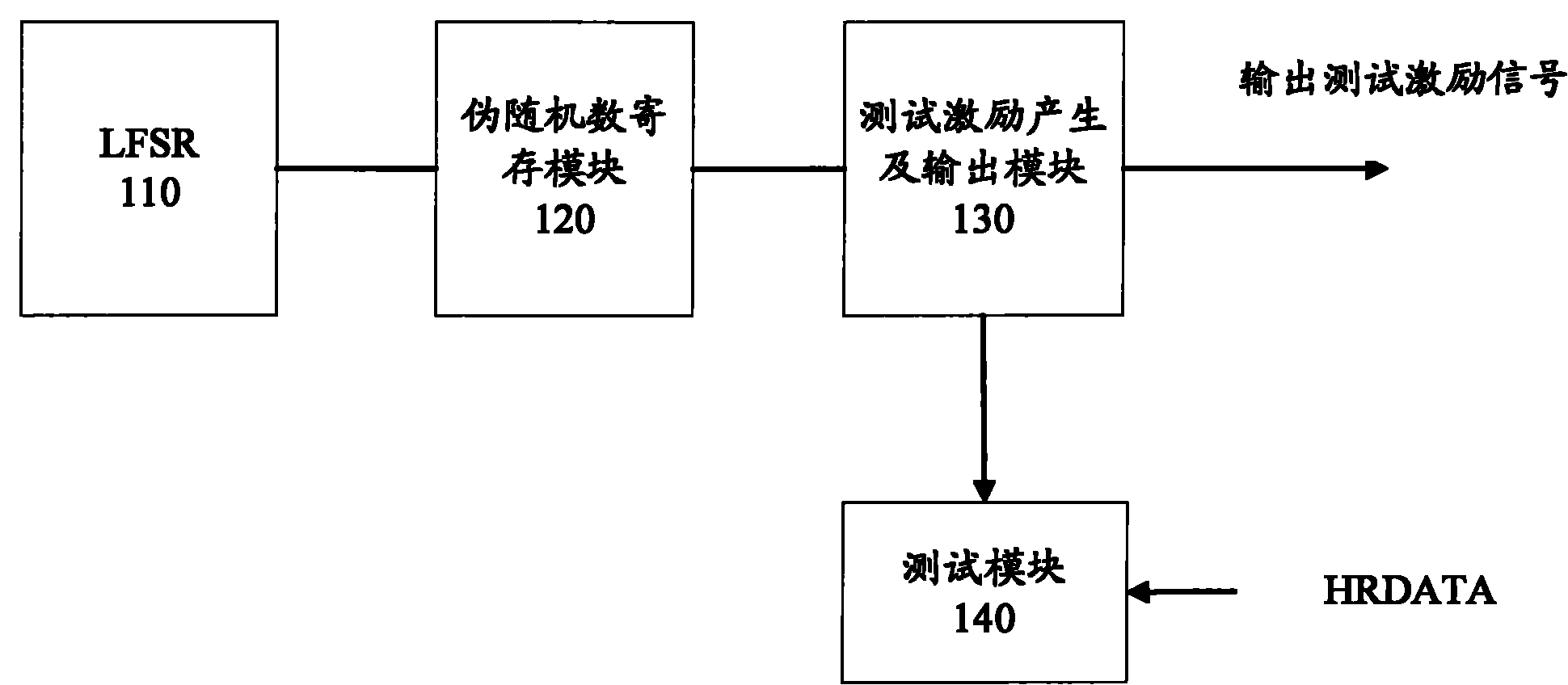

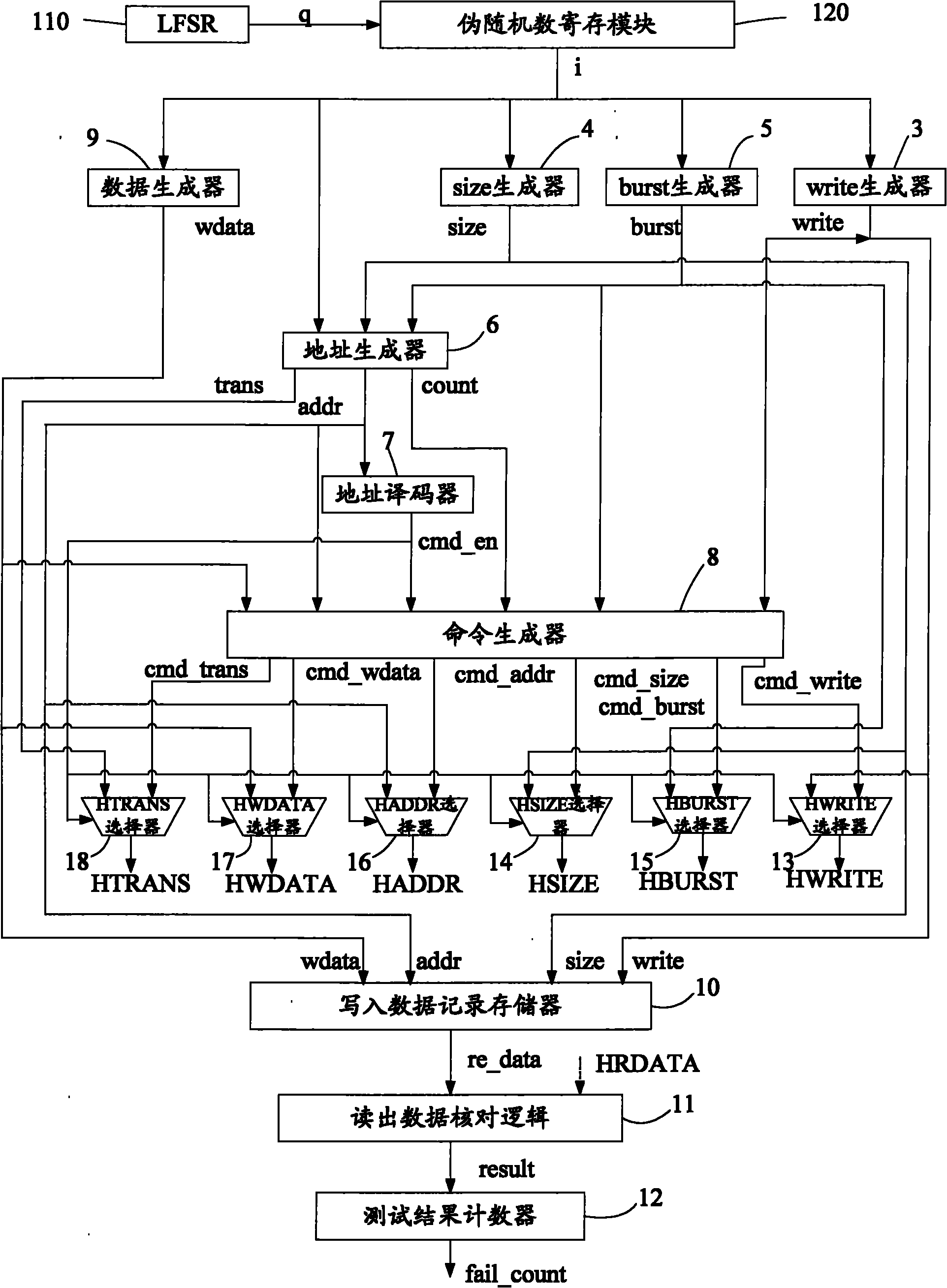

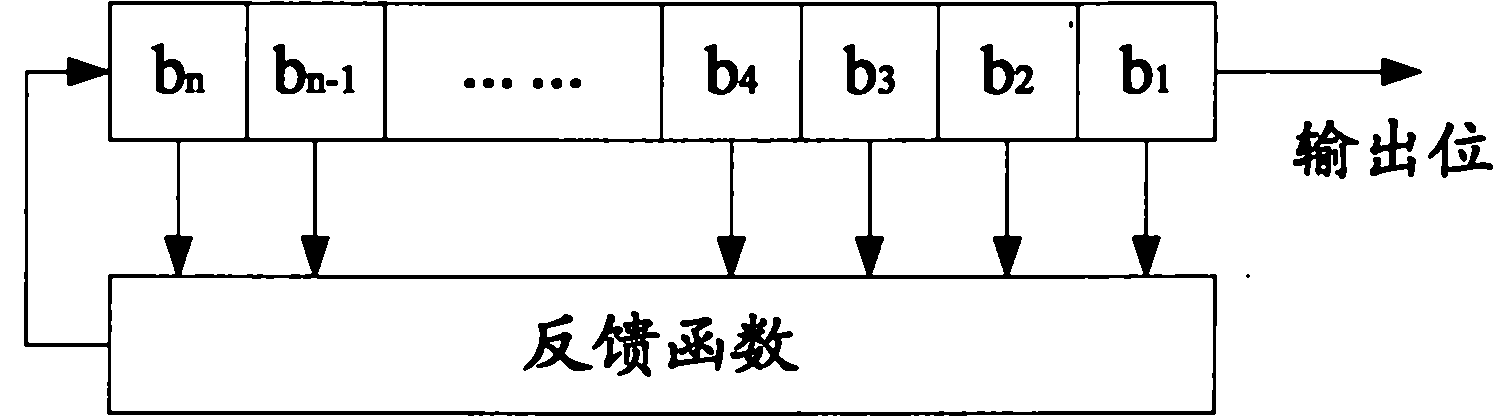

[0023] The present invention mainly lies in that, based on the pseudo-random numbers generated by the LFSR, the generated pseudo-random numbers are converted into random test excitations conforming to the AHB bus protocol, and random test excitations for external storage interfaces are generated, thereby realizing random testing for external storage interfaces.

[0024] Specifically, the AHB bus signals include: clock signal HCLK, global reset signal HRESET, slave device selection signal HSEL, read and write signal HWRITE, transmission le...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More