Message speed limitation method, device and network equipment

A speed limiting device and message technology, applied in the field of network communication, can solve the problems of waste of CPU resources and poor practicability, and achieve the effect of improving the utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

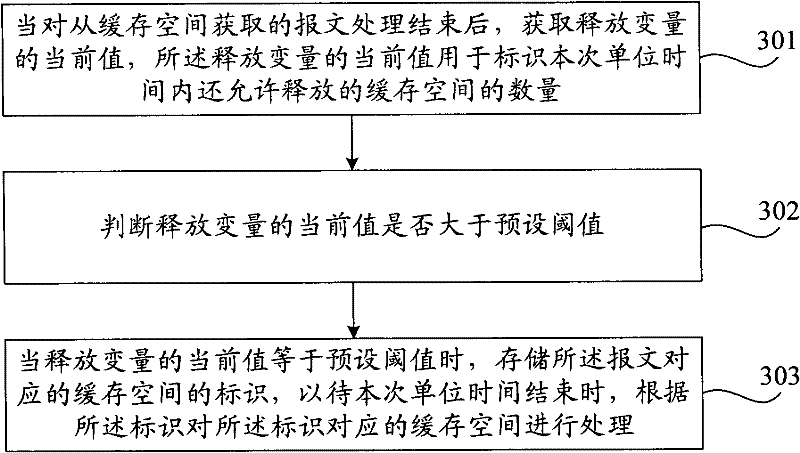

[0036] image 3 It is a flow chart of the packet rate limiting method provided by Embodiment 1 of the present invention. The execution subject of this embodiment is a communication device, combined with figure 1 shown in the structure, image 3 The packet rate limiting method in this embodiment shown includes:

[0037] Step 301, after the processing of the message obtained from the cache space is completed, obtain the current value of the release variable, and the current value of the release variable is used to identify the amount of cache space that is still allowed to be released per unit time;

[0038] Wherein, the release variable represents the amount of cache space that is allowed to be released per unit time, and the value of the release variable changes with time (actually, it refers to the release of the cache space). Specifically, when the CPU in the communication device determines that the current acquired location is valid according to the validity identifier i...

Embodiment 2

[0045] Figure 4 It is a flow chart of the packet rate limiting method provided by Embodiment 2 of the present invention. This embodiment can be implemented based on the first embodiment, and the similarities thereof will not be repeated here. Such as Figure 4 As shown, the message rate limiting method in this embodiment includes:

[0046] In step 401, the CPU acquires the message from the cache space, sends the message to the software processing module for processing, and moves the acquired position to the next cache space.

[0047] Step 402, the software module of the CPU processes the message, and releases the cache space after the message is processed.

[0048] In step 403, the message processing ends, and the CPU obtains the current value of the released variable, and judges whether the current value of the released variable is 0; wherein, in this embodiment, the preset threshold is taken as 0. When the judgment result is that the current value of the released variab...

Embodiment 3

[0056] Figure 5a A flow chart of a method for obtaining the initial value of the release variable provided in Embodiment 3 of the present invention; Figure 5b It is a flow chart of another method for obtaining the initial value of the released variable provided by Embodiment 3 of the present invention. Specifically, in this embodiment, the initial value of the release variable is obtained according to the preset packet rate limit rate and the number of invalid buffer spaces in the packet receiving ring. Wherein, the invalid cache space refers to the cache space whose validity flag is invalid in the acquired packet receiving ring when the technical solution of the present invention is about to be implemented. Wherein, the timing for implementing the technical solution of the present invention may be when the communication device is in an initial state or in a non-initial state. Wherein, if the communication device executes the technical solution of the present invention in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More