Method for doping fin field-effect transistors

A fin-type field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve the effect of improving electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

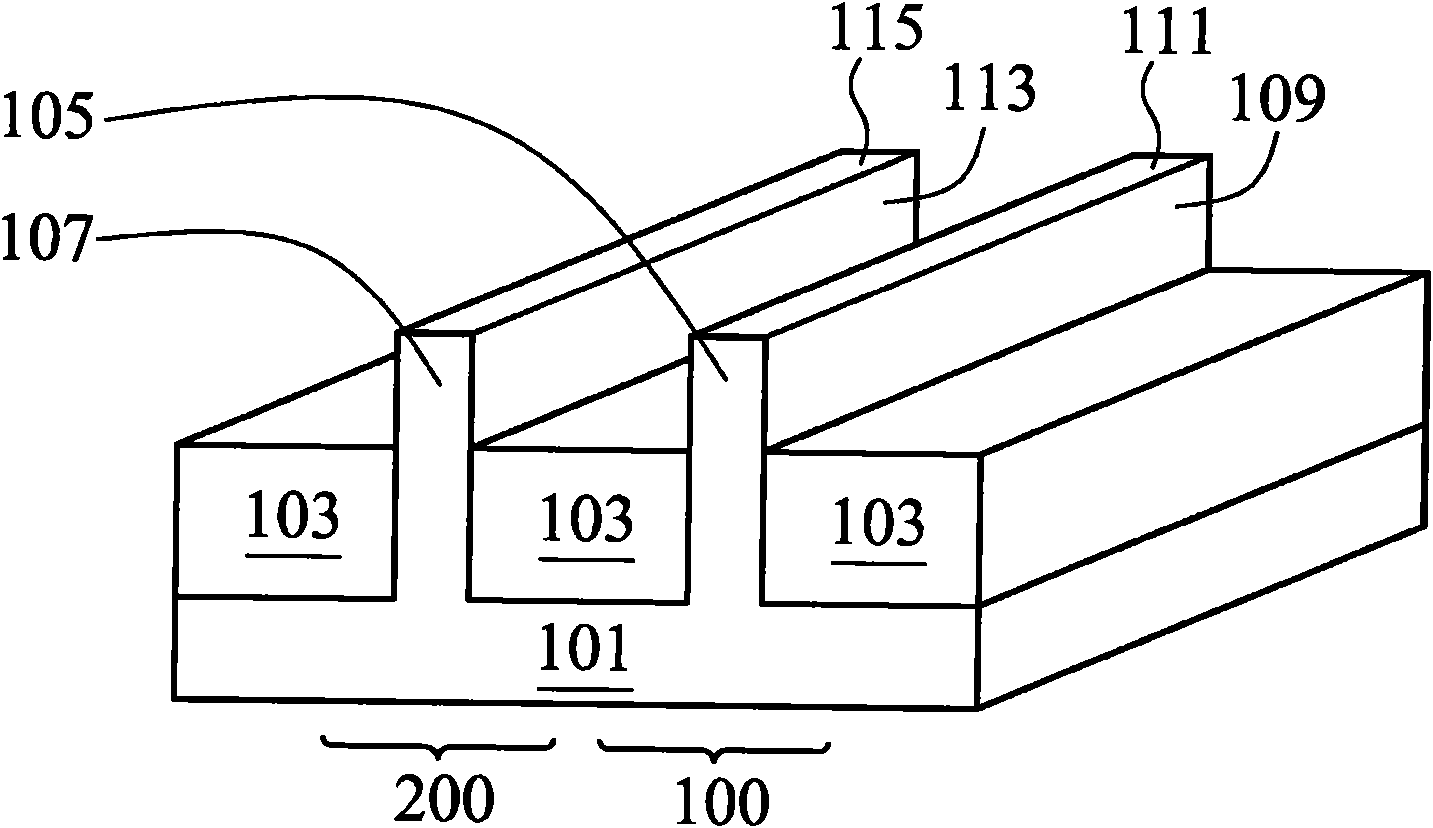

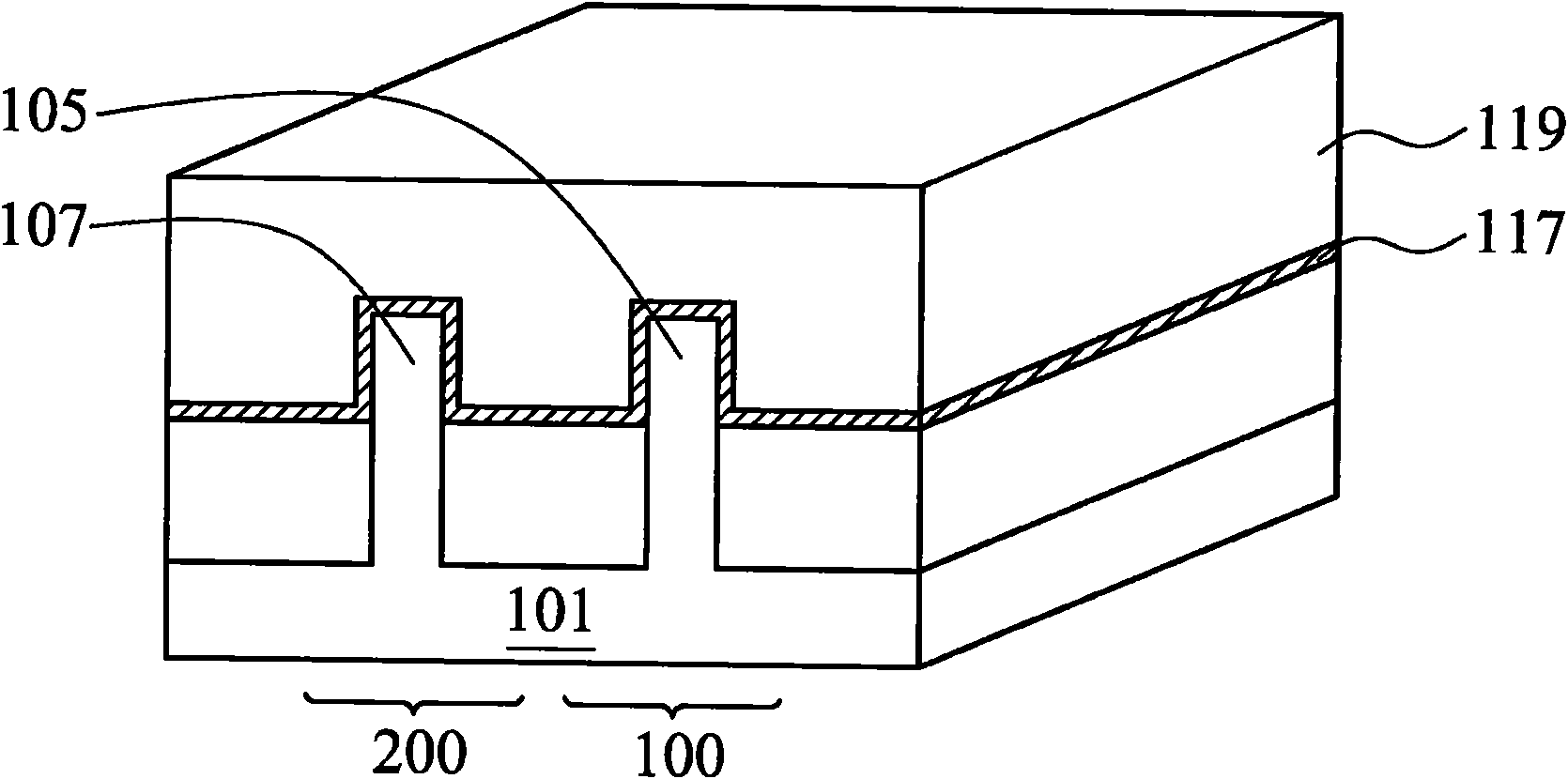

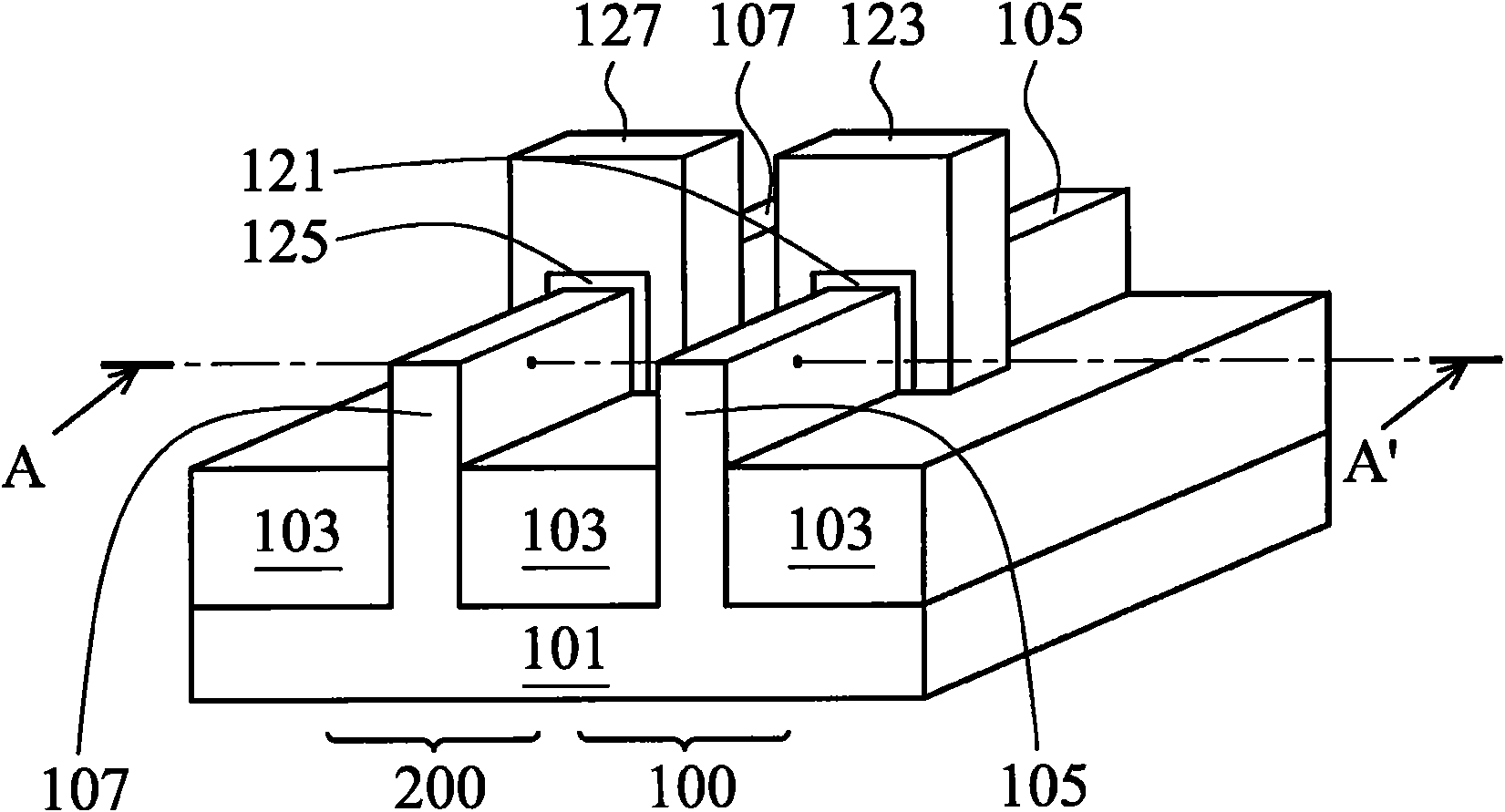

[0028] Figure 1 to Figure 8 Perspective and cross-sectional views of the different stages of making a FinFET. Figure 11 A flowchart depicting a method 500 of fabricating a FinFET structure according to an embodiment of the invention.

[0029] figure 1 and Figure 11 As shown, process step 501 provides a substrate including a first fin 105 and a second fin 107 . In some embodiments, the substrate 101 may be a silicon substrate, a germanium substrate or a substrate of other semiconductor materials. The substrate 101 may be doped with p-type or n-type dopants. An isolation region such as a shallow trench isolation region 103 (shallow trench isolation region, STI region) may be formed in or above the substrate 101 . The first semiconductor fin 105 and the second semiconductor fin 107 extend above the top surface of the STI region 103 . The first semiconductor fin 105 has a top surface 111 and sidewalls 109 . The second semiconductor fin 107 has a top surface 115 and side...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More