Method and system for detecting false capacity memory

A memory and false capacity technology, applied in the detection field, can solve the problems of imperfect detection methods and slow detection speed of false capacity memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

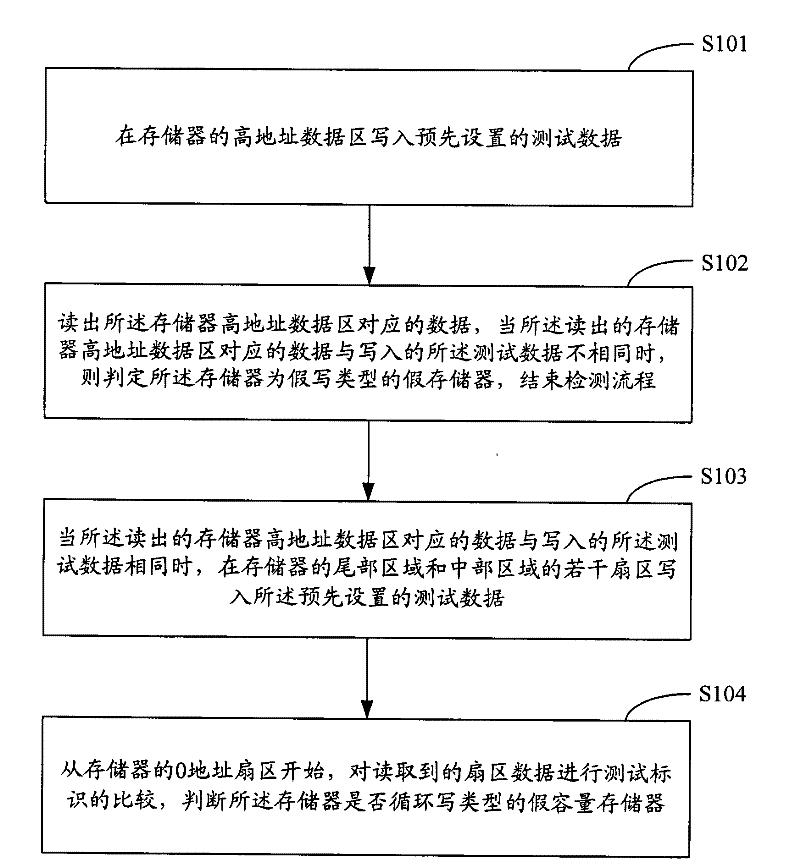

[0039] figure 1 It shows the implementation flow of the detection method of the false capacity memory provided by the embodiment of the present invention, and its specific steps are as follows:

[0040] In step S101, the preset test data is written in the high address data area of the memory.

[0041] In the embodiment of the present invention, it is necessary to pre-configure and generate test data before performing this step. The specific implementation steps are given below, and will not be repeated here, but they are not intended to limit the present invention.

[0042]Wherein, the memory may be a Nand Flash flash memory, and the following uses the Nand Flash flash memory as an example for description.

[0043] In step S102, the data corresponding to the high address data area of the memory is read out, and when the data corresponding to the high address data area of the memory read out is different from the written test data, it is determined that the memory is Th...

Embodiment 2

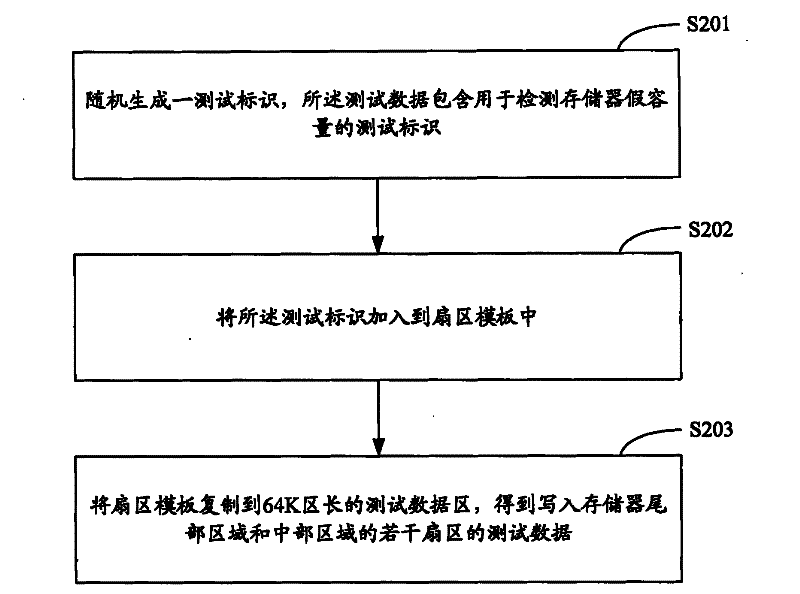

[0050] figure 2 It shows the implementation process of generating test data with preset settings provided by the embodiment of the present invention, and its specific steps are as follows:

[0051] In step S201, a test identifier is randomly generated, and the test data includes the test identifier for detecting the false capacity of the memory.

[0052] In the embodiment of the present invention, the test mark is stored in a buffer with a length of 512 bytes. As a specific embodiment of the present invention, the test mark can adopt 2 DWORD (double word), when 2 DWORD , its random repetition probability is set to 1 / 18446744073709551616 of 2 to the 64th power.

[0053] In step S202, the test identifier is added to the sector template.

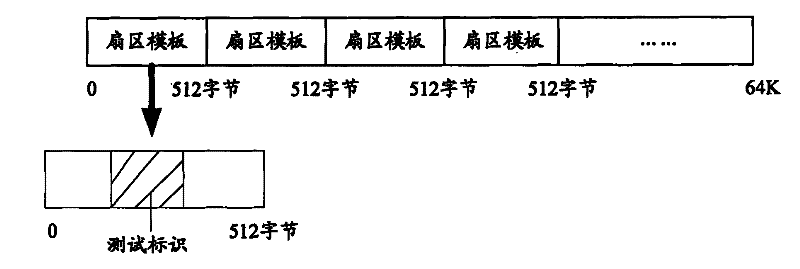

[0054] In step S203, the sector template is copied to the test data area with a length of 64K to obtain test data written into several sectors in the tail area and the middle area of the memory.

[0055] In the embodiment of the present i...

Embodiment 3

[0057] Figure 4 It shows the implementation flow of starting from the 0 address sector of the memory, comparing the read sector data with the test identification, and judging whether the memory is a cyclic write type pseudo-capacity memory provided by the embodiment of the present invention. The steps are as follows:

[0058] In step S401, the sector data at address 0 of the memory is read.

[0059] In the embodiment of the present invention, sector data is read starting from the logical address 0 sector.

[0060] In step S402, it is judged whether the data at the specified position of the sector data contains the test identifier contained in the test data, if yes, execute step S403, otherwise execute step S404.

[0061] In the embodiment of the present invention, at the identification bit (the data that must be carried in the sector data) at the specified position of the read sector data, it is judged whether the identification bit is the same as the test identification co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More