Integrated circuit, device and manufacture method thereof

A manufacturing method and circuit technology, applied in the field of integrated circuits, devices and their manufacturing, can solve the problems of lower layout efficiency, inability of inductive amplifiers to cooperate with memory cell structures, and slow reading speed of high-density memory arrays, etc., so as to reduce bit line load , Reduce the effect of reading access time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The manufacture and use of this preferred embodiment are discussed in detail below. It should be understood that although the present invention provides inventive concepts that can be applied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

[0060] The embodiments of the present invention described in detail now provide novel circuits and methods for high-density memory arrays. Using these embodiments can reduce bit line loading without corresponding silicon area penalty, thereby reducing the read access time of the memory cell.

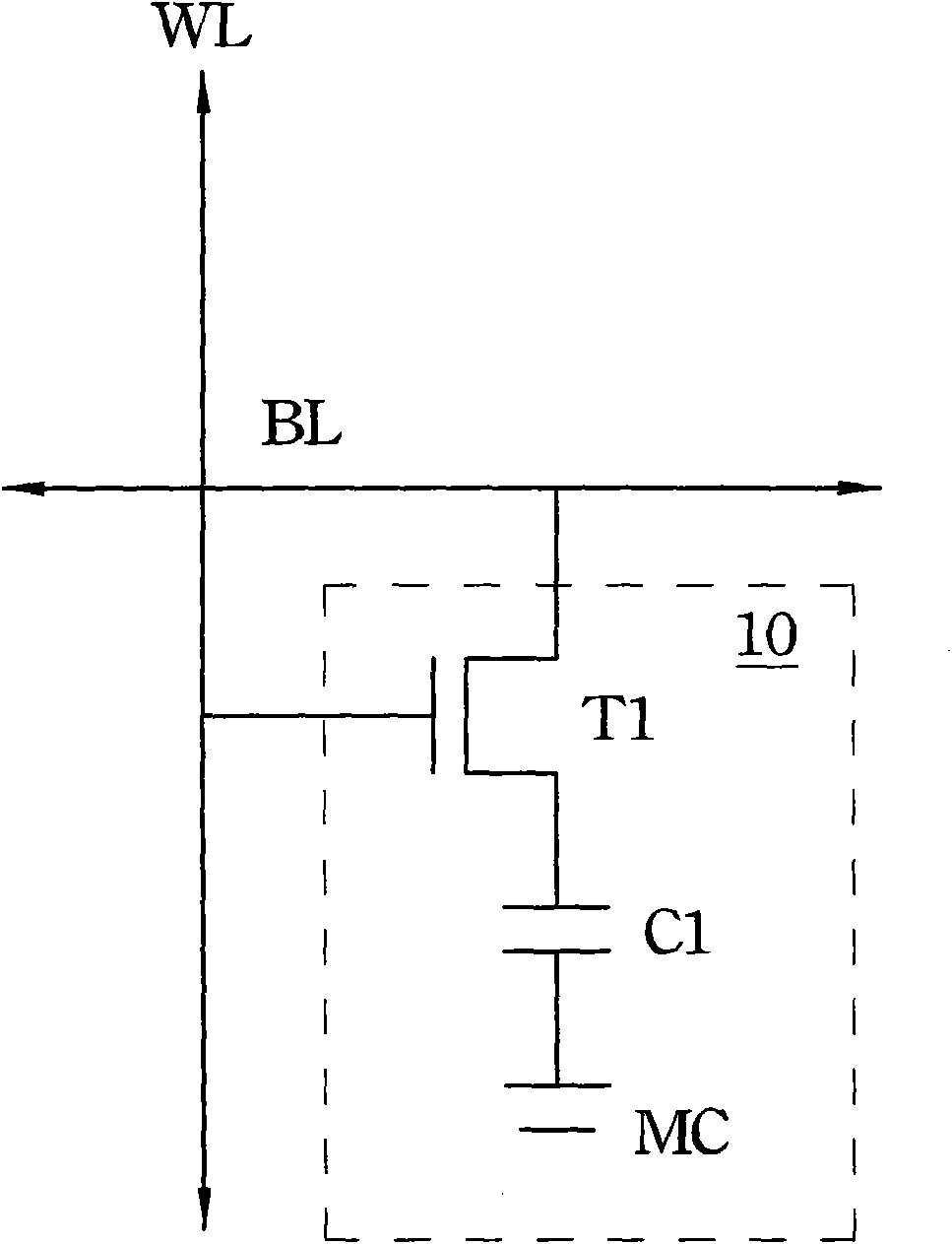

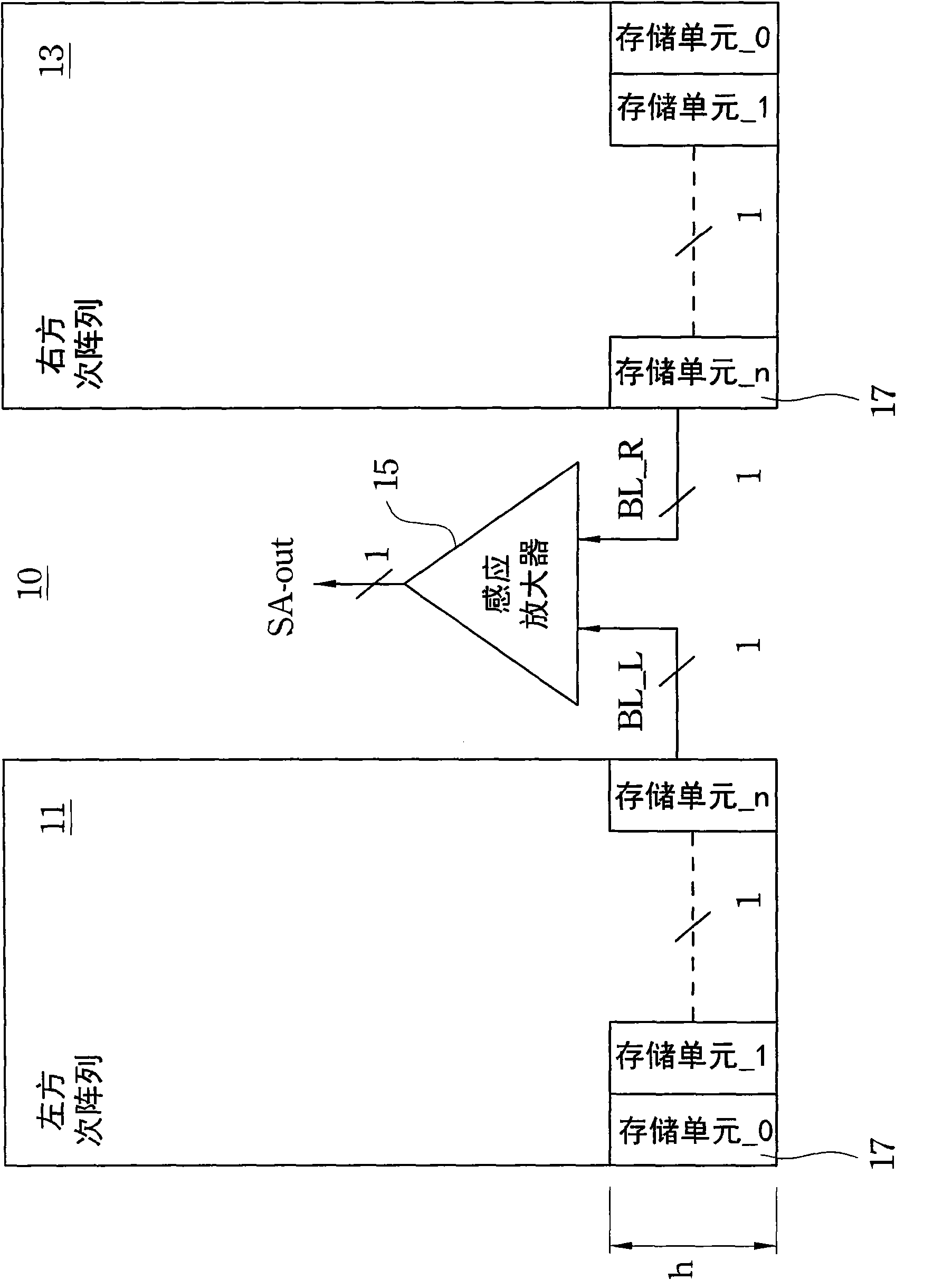

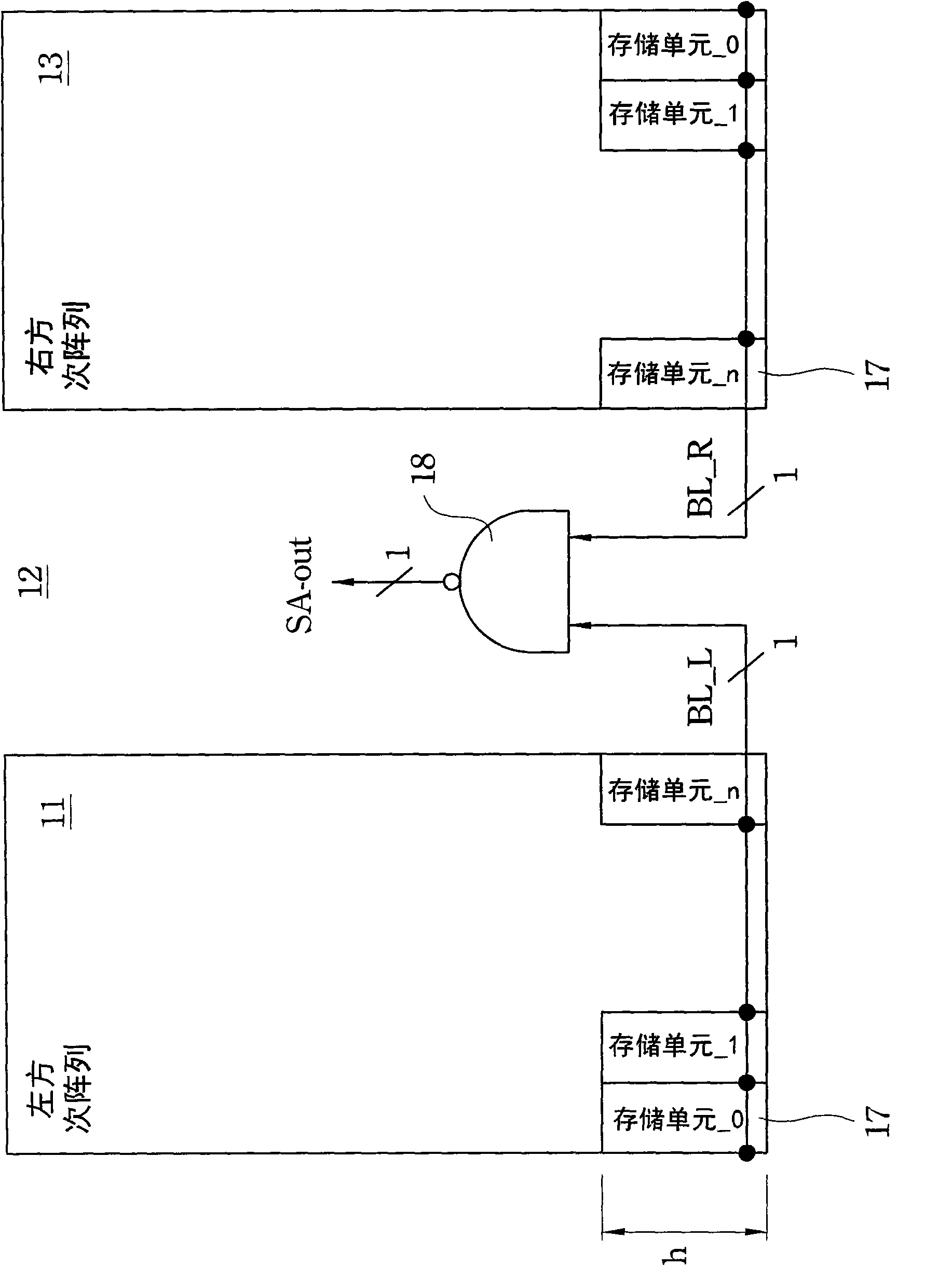

[0061] Figure 4 The storage array 40 of the first exemplary embodiment is shown. The left sub-array 51 and the right sub-array 53 are shown therein. In each array, a plurality of adjacent memory cells 17 are arranged in columns. Although not shown, examples of each memory cell column, bit lines BL_L an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More