FPGA (Field Programmable Gate Array)-based spike potential signal parallel detection device and method

A signal detector and spike technology, which is applied in the field of FPGA-based spike signal parallel detection device, can solve the problems of parallel real-time detection of multi-channel spike signals, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

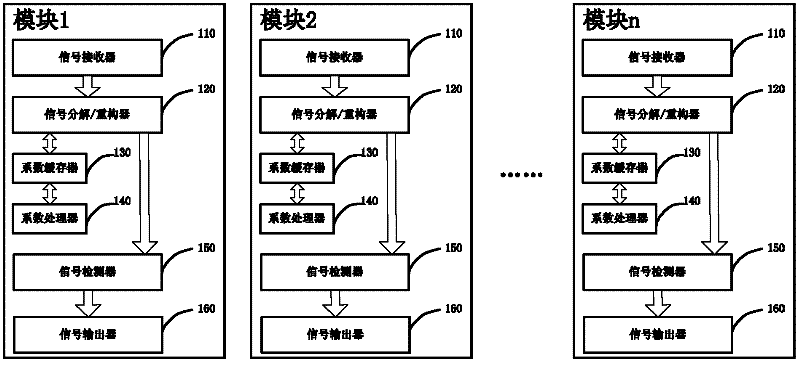

[0056] Such as figure 1 As shown, an FPGA-based spike signal parallel detection device is composed of n parallel modules, and each module includes: a signal receiver 110, a signal decomposition / reconstructor 120, a coefficient buffer 130, and a coefficient processor 140 , a signal detector 150 and a signal outputter 160.

[0057] The signal receiver 110 controls the reception of the signal sequence to be detected by judging the working state of the signal decomposing / reconstructing device 120. When the working state of the signal decomposing / reconstructing device 120 is idle, the signal receiver 110 receives the signal sequence to be detected and transmit it to the signal decomposer / reconstructor 120;

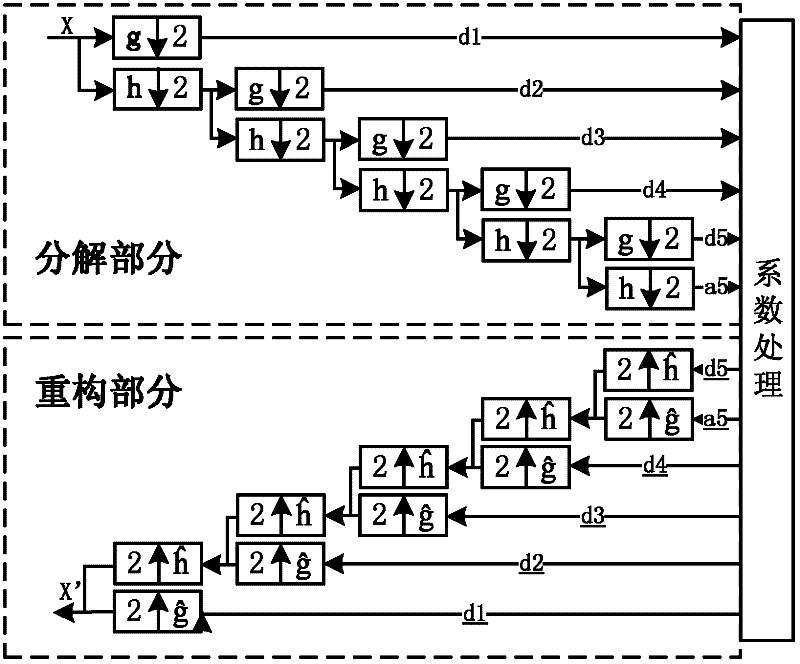

[0058] The signal decomposition / reconstruction unit 120, on the one hand, receives and decomposes the signal sequence to be detected transmitted by the signal receiver 110, sends the decomposed coefficient sequence to the coefficient buffer 130, and receives the signal sequenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More