Reset circuit of anti-fuse type FPGA (Field Programmable Gate Array) system

An anti-fuse and circuit technology, which is applied in the field of anti-fuse FPGA system reset circuit, can solve the problems of automatic configuration of internal registers, inapplicability, and inability to realize asynchronous reset of anti-fuse FPGA, so as to eliminate competition risks and realize Effect of asynchronous reset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] A kind of antifuse type FPGA system reset circuit of the present invention is introduced below in conjunction with accompanying drawing and embodiment:

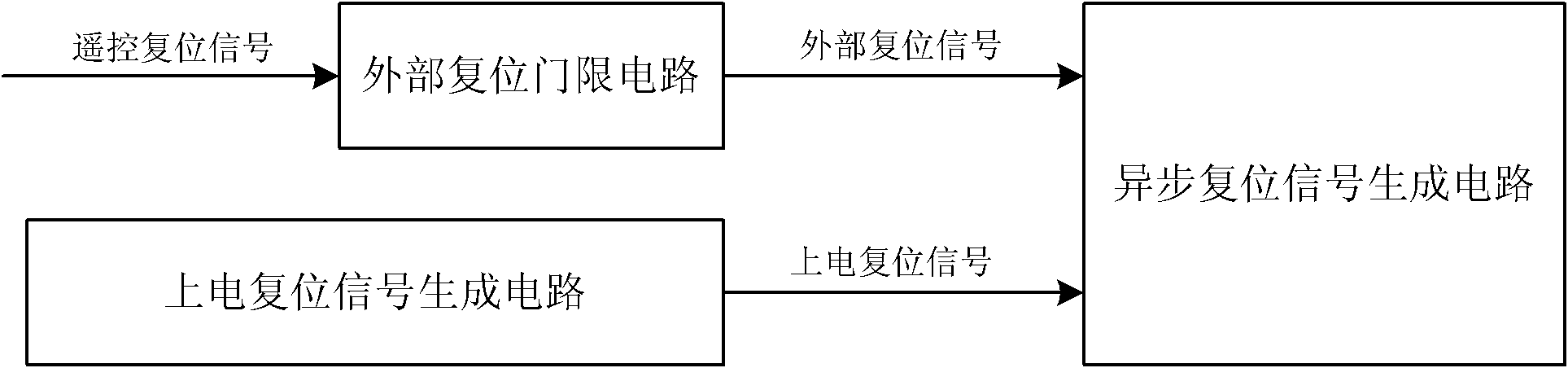

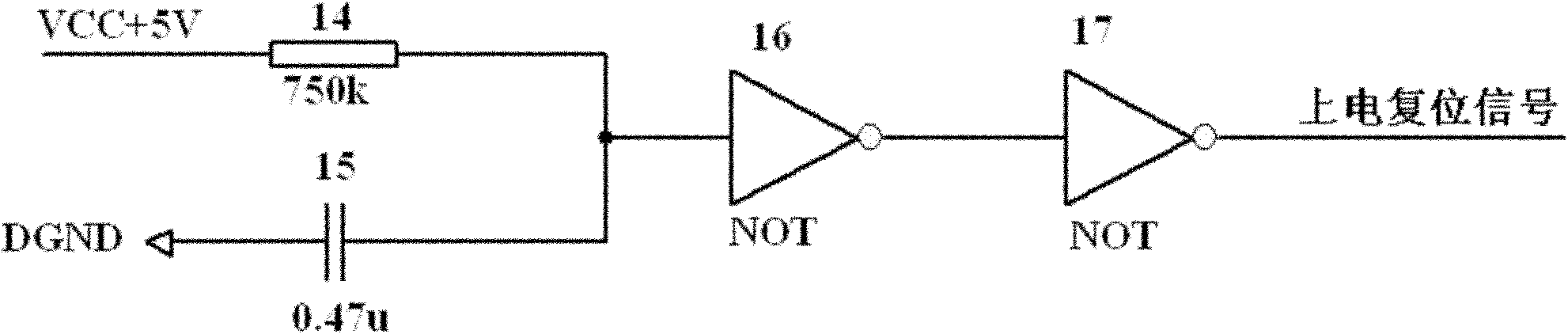

[0028] Such as figure 1 As shown, an anti-fuse type FPGA system reset circuit includes an external reset threshold circuit, a power-on reset signal generation circuit and an asynchronous reset signal generation circuit.

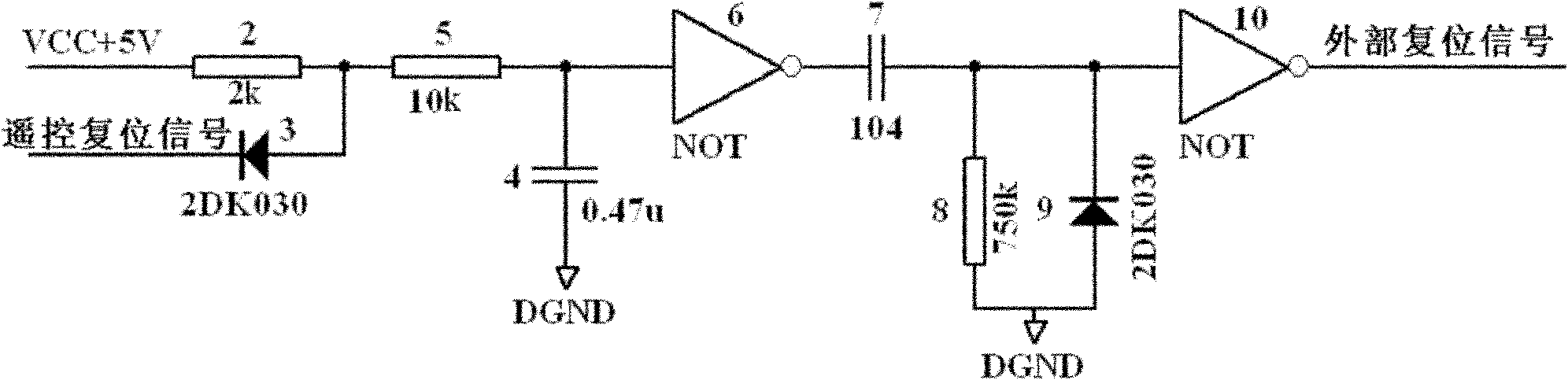

[0029] The external reset threshold circuit is connected with the asynchronous reset signal generating circuit, which receives the remote reset signal, removes the jitter in the remote reset signal, and provides an external reset signal for the asynchronous reset signal generating circuit. The external reset signal is an active-low pulse signal, the amplitude of the external reset signal is 3.3V or 5V, and the pulse width is greater than 10ms.

[0030] In this embodiment, for the anti-fuse FPGA A42MX36, the amplitude of the asynchronous reset signal is 5V, and the pulse width is 10ms. The external r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More