Processor and processing method for VLIW (very low instruction word)

A technology of super-long instruction word and processing method, which is applied in the direction of machine execution device, etc., can solve the problems of increasing the complexity of instruction fetching, increasing the complexity of instruction issuing, and increasing the length of writing instruction word, so as to facilitate instruction execution and reduce output. Select logic, reduce the effect of the output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

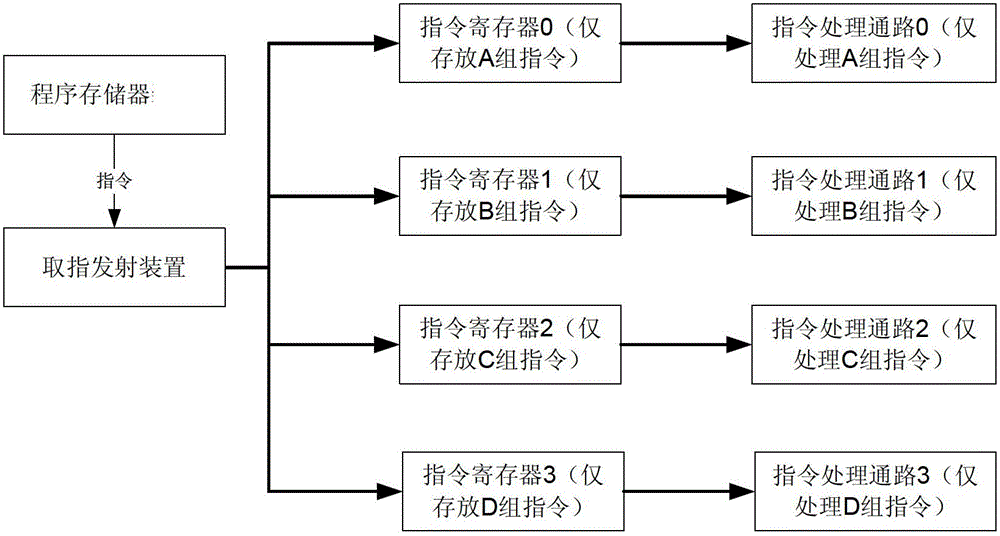

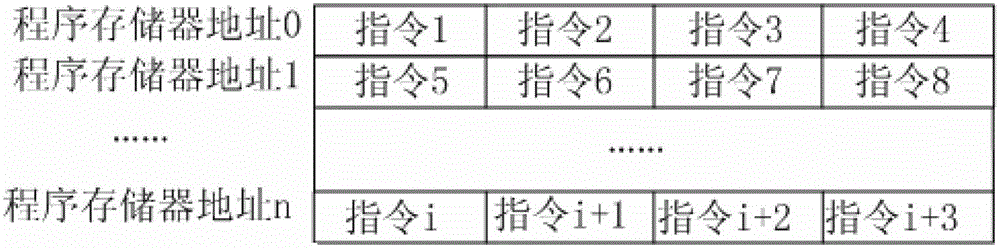

[0065] One, the specific introduction of the program memory of the processor of the very long instruction word VLIW of the present embodiment:

[0066] Such as image 3 As shown, each storage address of the program memory of the processor of the very long instruction word VLIW in this embodiment can store the structure of instructions equal to the number of instruction groups, and the instructions are divided into four different groups, then the program memory The number of instructions stored in each address unit is four, that is, instruction 1, instruction 2, instruction 3, and instruction 4 are combined and placed in address 0 of the program memory, instruction 5, instruction 6, instruction 7, instruction 8 These four instructions are combined and put into address 2 of the program memory, and so on, instruction i, instruction i+1, instruction i+2, instruction i+3, and 4 instructions are combined and put into address n of the program memory .

[0067] Two, the specific int...

Embodiment 2

[0078] Such as Figure 5 and Figure 6 As shown, the device structure of the very long instruction word VLIW processor in this embodiment is basically the same as the device structure in Embodiment 1, except that an instruction jump module is added to the instruction fetching and transmitting device, wherein the instruction The jump module is used to output an instruction instruction indicating the jump position of the instruction before the instruction sequence splicing module extracts the instruction, so that the instruction stored in the instruction cache module is invalid, and the instruction sequence splicing module extracts the instruction jump according to the instruction instruction Instructions after turning the position.

[0079] The above-mentioned embodiments make corresponding changes to the maximum storage capacity of each storage unit of the program memory according to the number of groups of instructions, so that each storage unit of the program memory is allo...

Embodiment 1

[0227] The number of parallel instructions this time is 1, and the number of instructions to run in the next cycle is 2:

[0228] Such as Figure 4 As shown, the instruction fetching and emitting device fetches four instructions including instruction 1, instruction 2, instruction 3 and instruction 4 from the instruction address 0, and judges the number of instructions to be executed this time according to the flag bit. The instructions to be executed in parallel this time are 1, that is, the instruction 1 is emitted in the first clock cycle, that is, Inst0-instruction 1; Inst1-NOP; Inst2-NOP; Inst3-NOP; In this embodiment, Inst0 belongs to group A instructions, and Inst0 is input into the instruction register In 0, empty instructions are input in instruction register 1, instruction register 2, and instruction register 3. Input the unlaunched instruction 2, instruction 3 and instruction 4 into the cache module for storage.

[0229] When the instruction is transmitted in the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More