Patents

Literature

53results about How to "Optimizing place and route" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

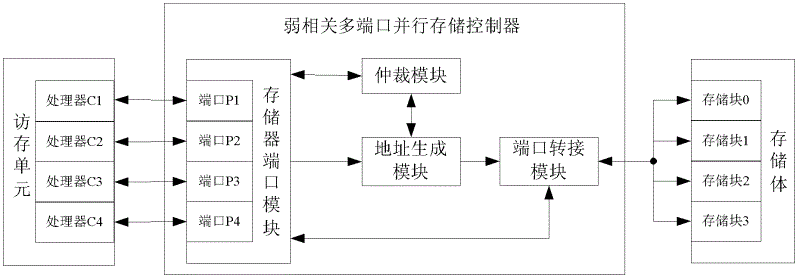

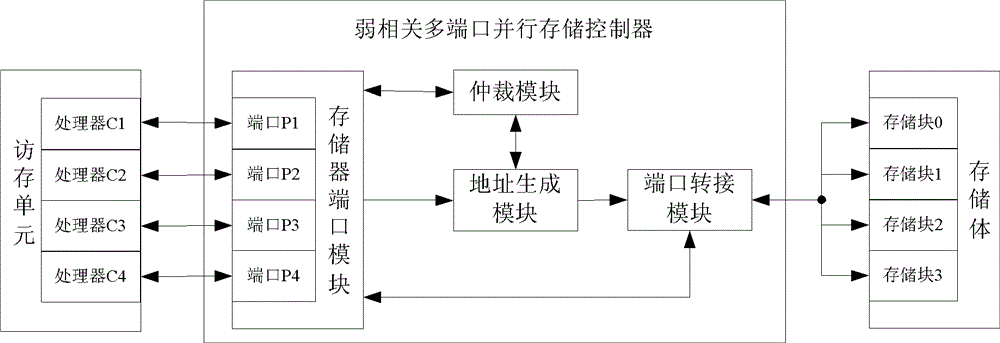

Weak correlation multiport parallel store controller

InactiveCN102622192AIncrease flexibilityReduce in quantityInput/output to record carriersComputer architectureControl store

The invention provides a weak correlation multiport parallel store controller, which is connected with a access memory unit in peripheral equipment and a storage stack including a plurality of storage body and can achieve multiport parallel storage between the visiting and storage unit in the peripheral equipment and the storage stack in the peripheral equipment. The weak correlation multiport parallel store controller comprises a storage port module, an arbitration module, an address generation module and a port switching module. The weak correlation multiport parallel store controller has the following advantages of (1) supporting block reading and writing in random lengths and being high in dexterity; (2) enabling transmission of address and data to multiplex in the same group of signal wires to complete, greatly reducing quantity of the transmission signal wires in a system, being favorable for application of distribution and wiring and reducing complexity and cost of the system; and (3) being simple in structure, less in used transmission signal wires and capable of supporting design and achievement of a large-scale multiport storage, and improving efficiency of parallel access memory of a plurality of processors.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

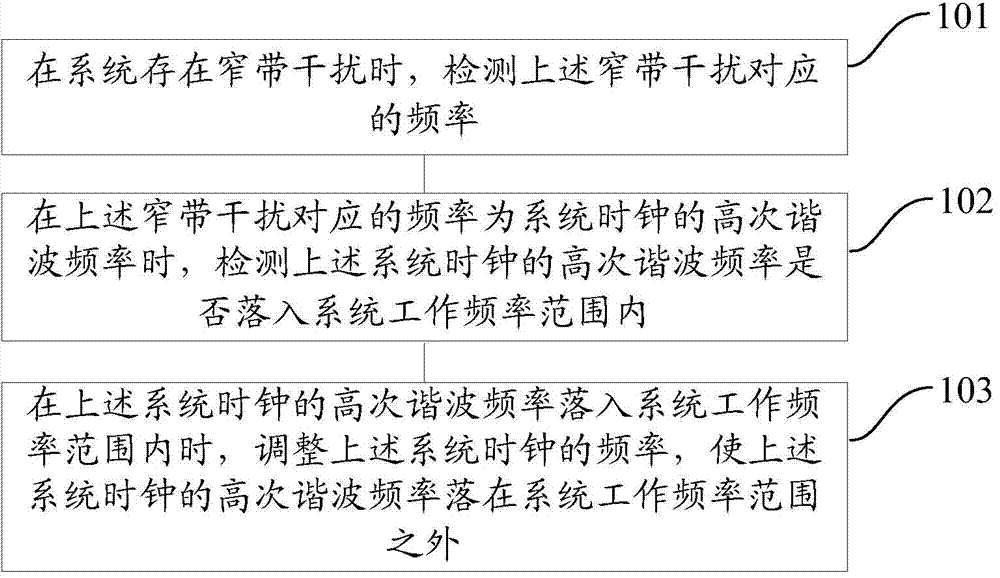

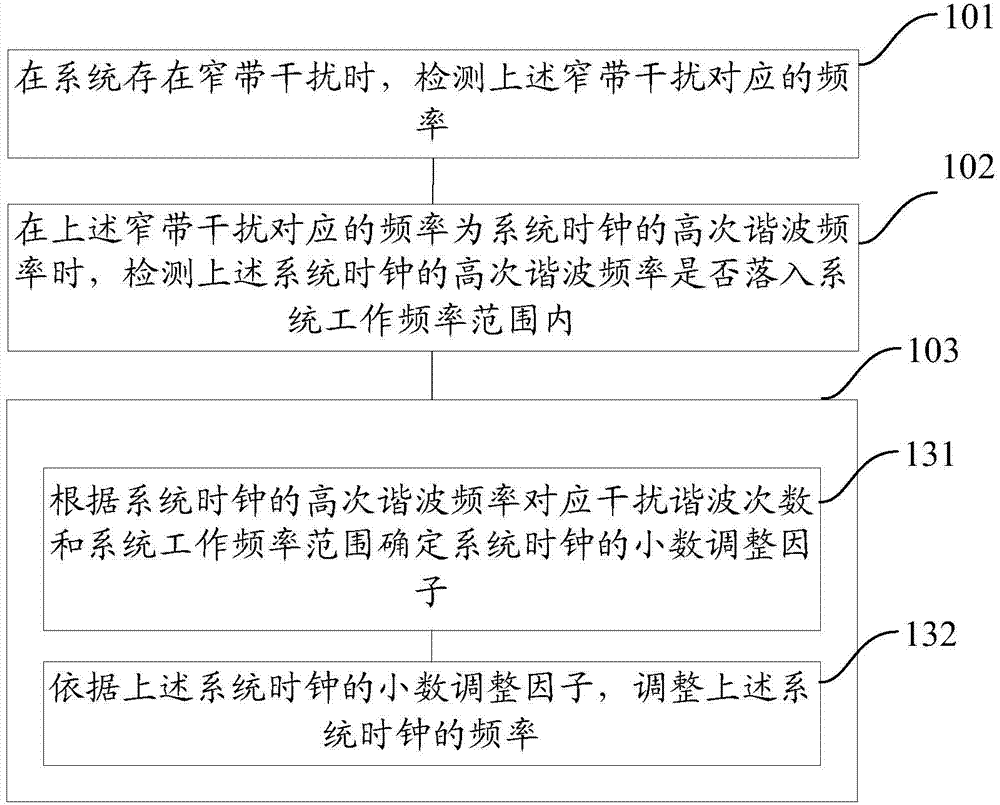

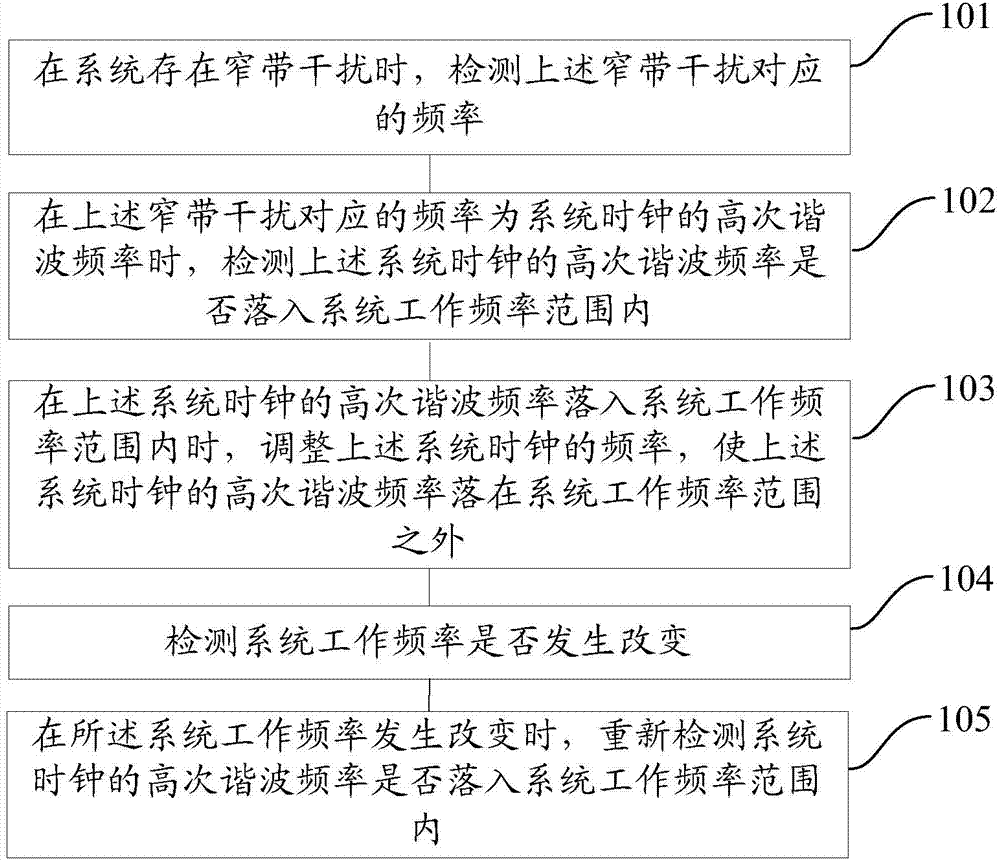

Method and device of restraining narrow-band interference

The invention provides a method and a device of restraining narrow-band interference. The method specifically comprises the following steps of detecting a frequency which corresponds to the narrow-band interference when a system has the narrow-band interference; detecting whether a higher harmonic frequency of a system clock falls into the operating frequency range of the system when the frequency which corresponds to the narrow-band interference is the higher harmonic frequency of the system clock; when the higher harmonic frequency of the system clock falls into the operating frequency range of the system, adjusting the frequency of the system clock so as to cause the higher harmonic frequency of the system clock to fall out of the operating frequency range of the system. According to the method and the system, the influence of the narrow-band interference of the system on the system performance is solved, and the equipment cost is reduced.

Owner:INNOFIDEI TECHNOLOGIES INC

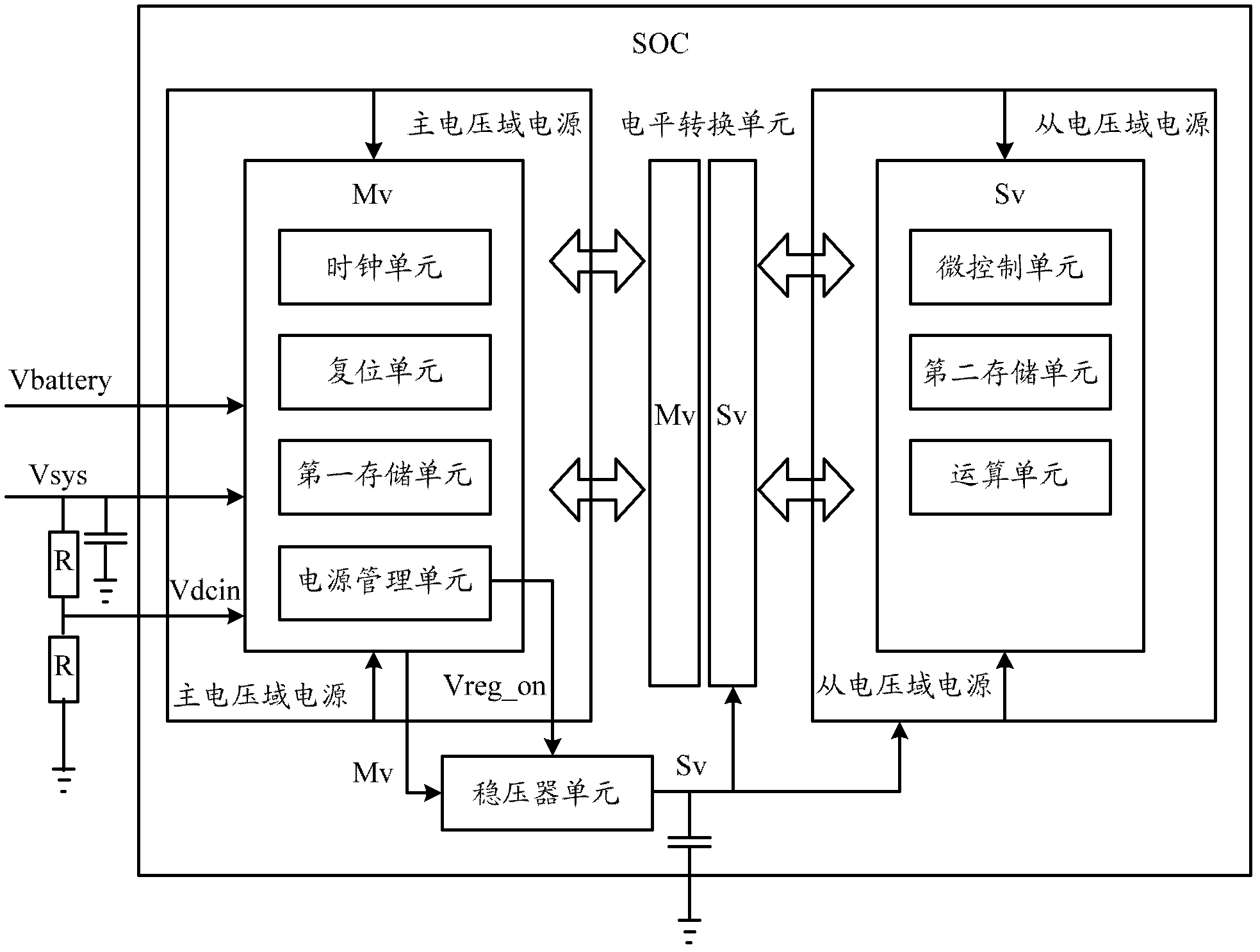

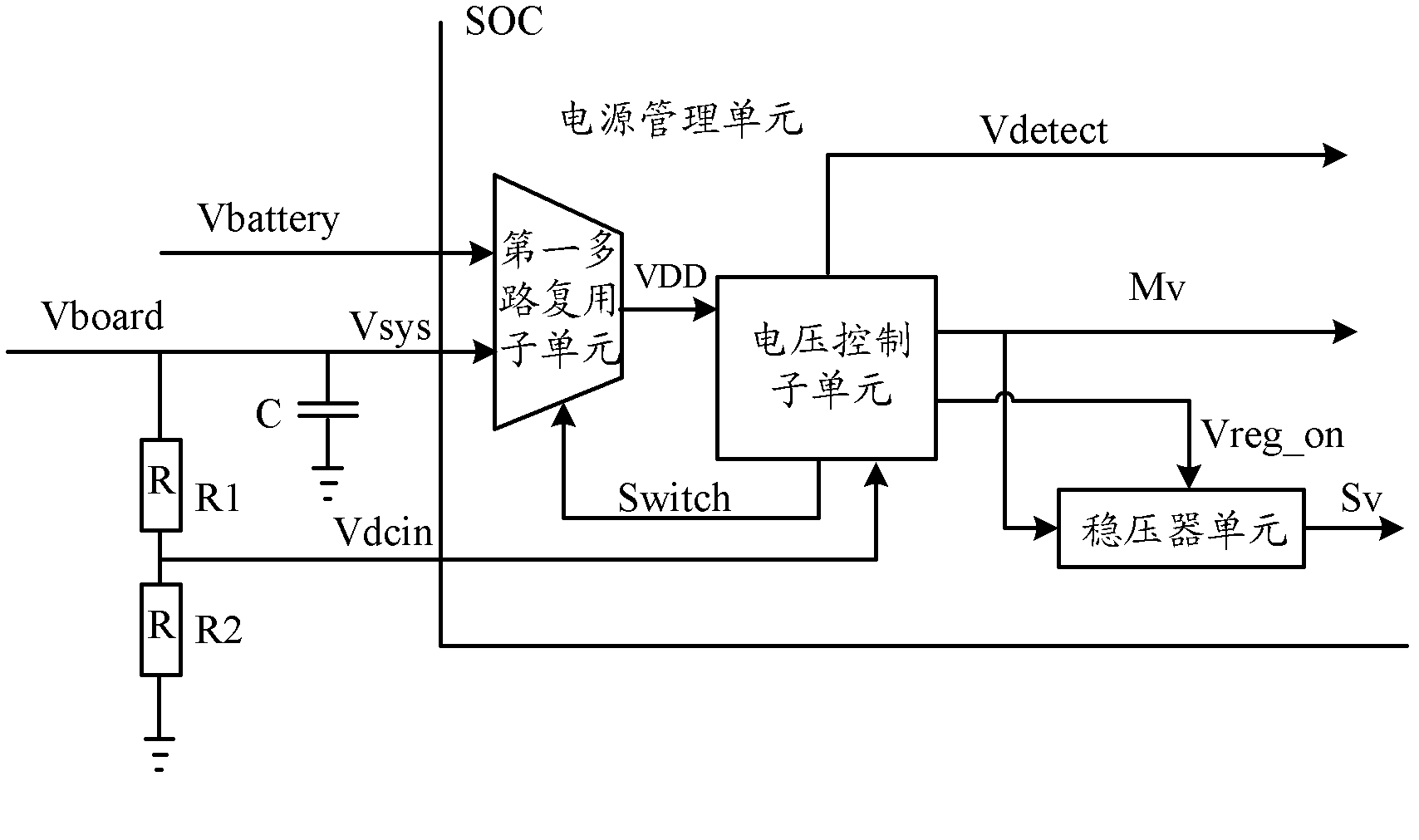

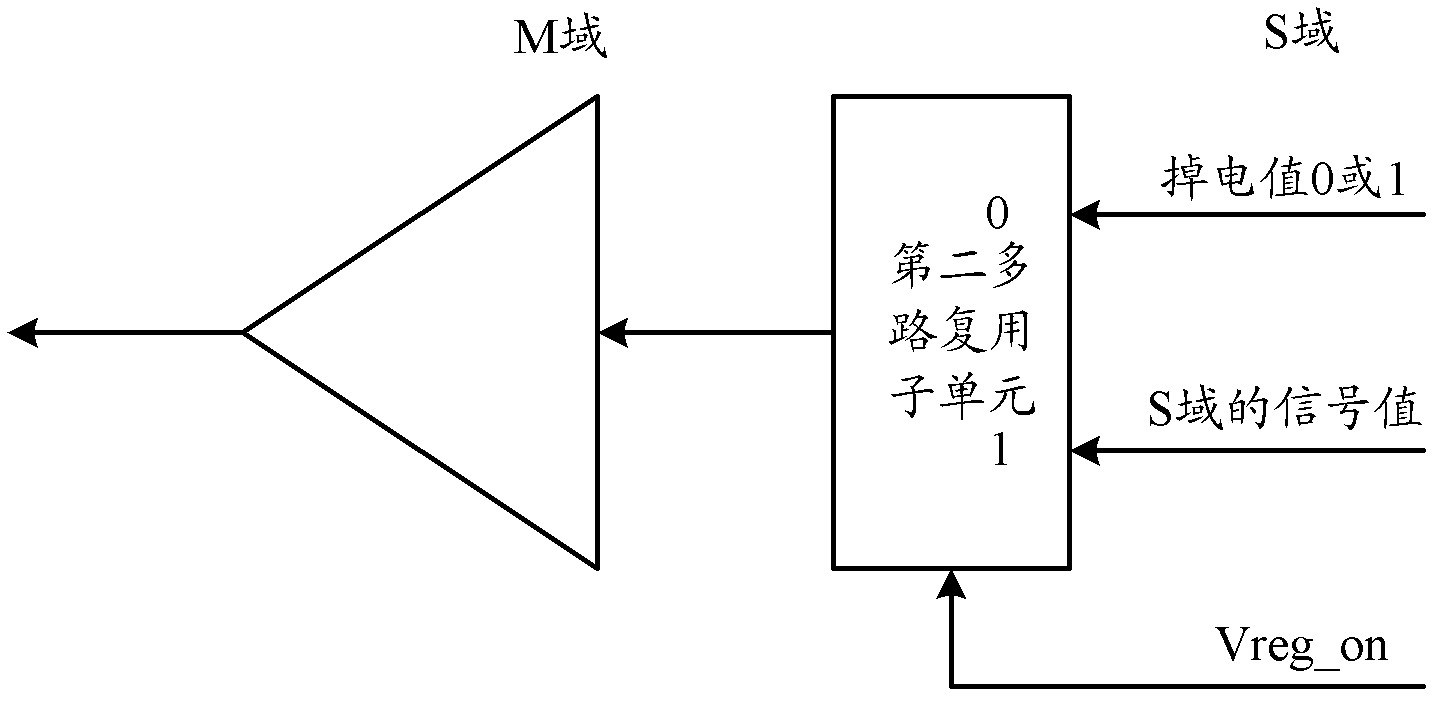

System on chip and resting and arousing method thereof

InactiveCN102541247ANot lostReduce dynamic power consumptionPower supply for data processingElectricityEngineering

The invention relates to the technical field of a system on a chip and discloses a system on a chip and a resting and arousing method thereof. In the system on the chip, a main voltage area and an auxiliary voltage area are designed, the auxiliary voltage area in which a micro-control unit is arranged can be closed or stepped down, information in the auxiliary voltage area is stored into a memory in the main voltage area by the micro-control unit before the auxiliary voltage area is powered down, the dynamic power consumption and the static power consumption of a digital circuit can be lowered, and the condition that the necessary information can not be lost can also be ensured; and moreover, the system on the chip does not need to depend on the support of a specific process or a specific component, which is very beneficial to arranging and wiring. After the system on the chip is aroused, the auxiliary voltage area is at a resetting state, and the occurrence of confusion of the working of a circuit is avoided; and until the voltage of the auxiliary voltage area is restored to a normal value, the auxiliary voltage area is released and reset, so that the entire circuit is in normal working anew.

Owner:HI TREND TECH SHANGHAI

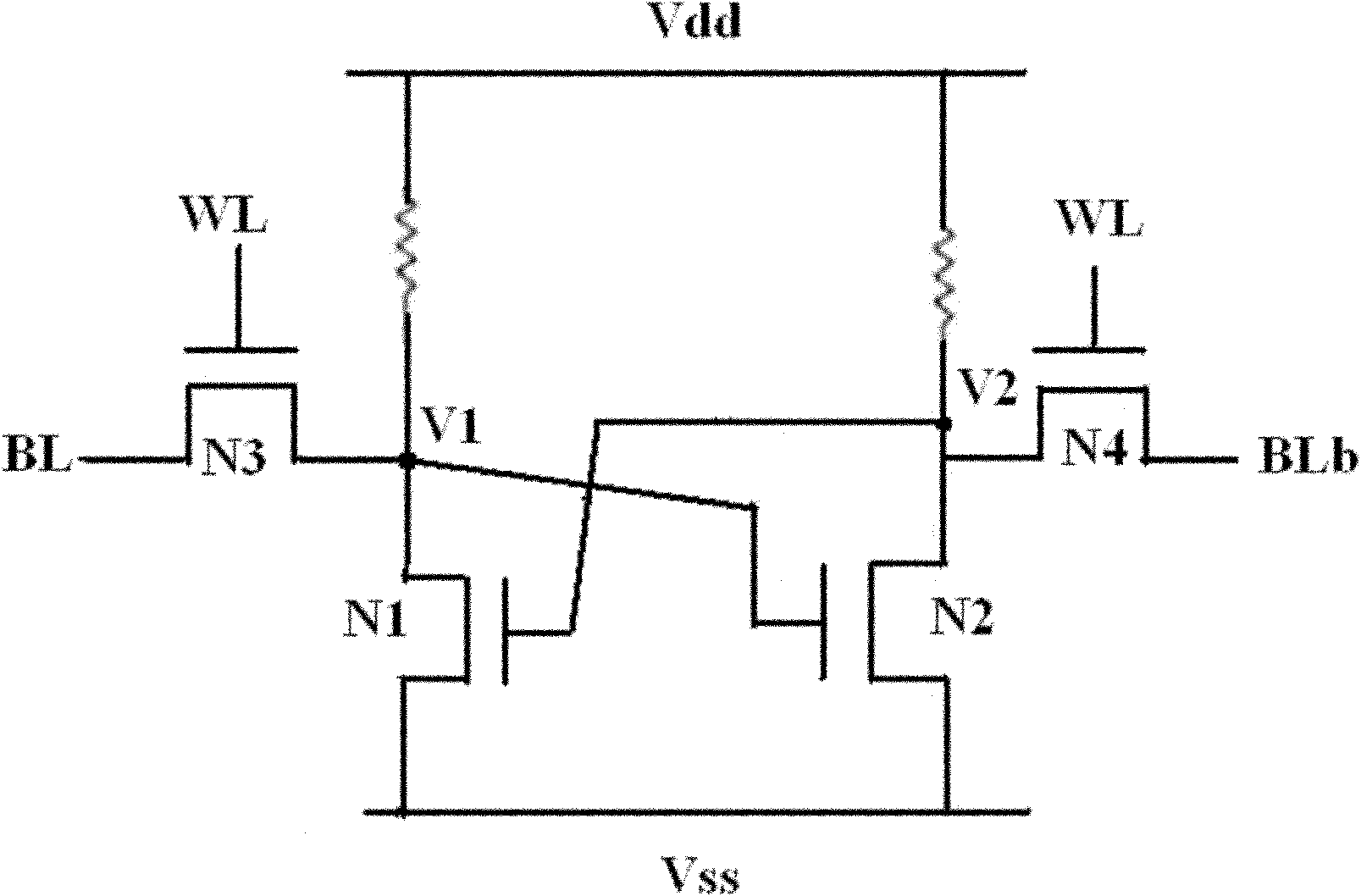

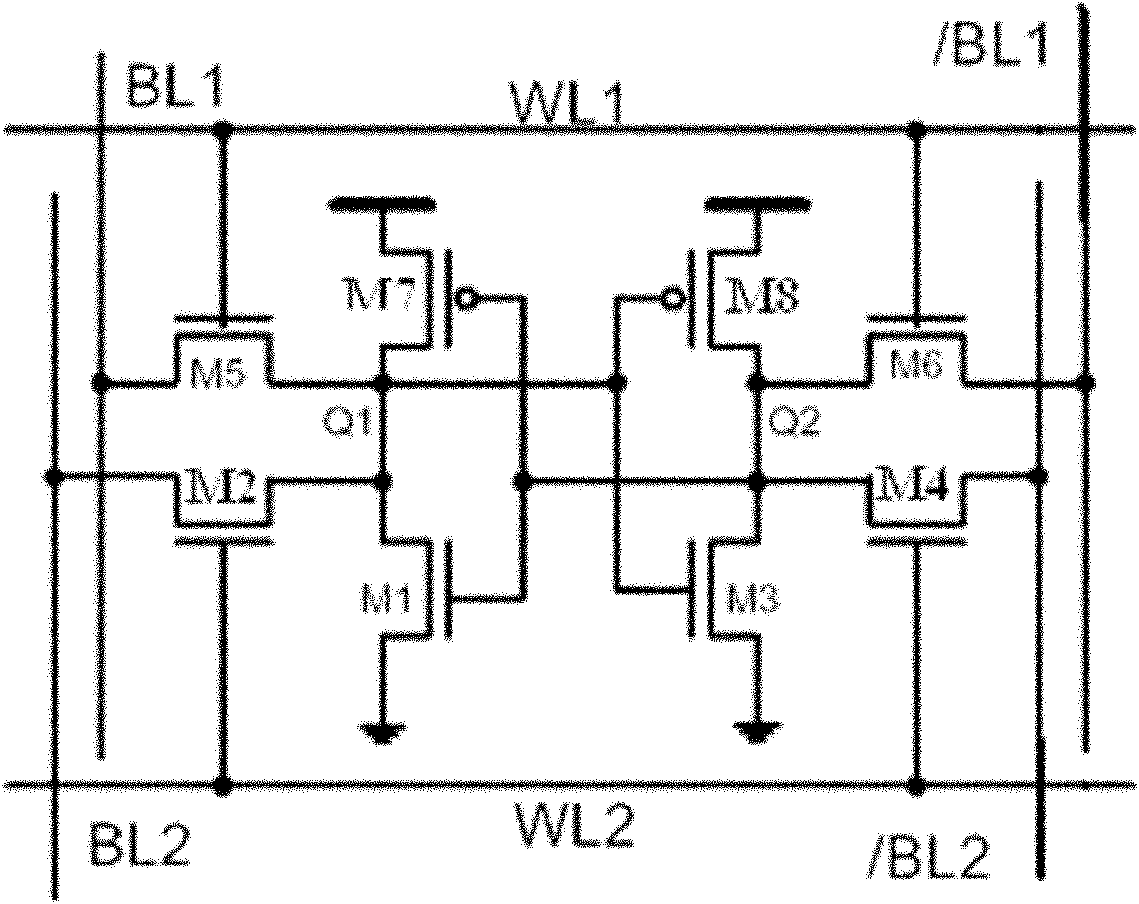

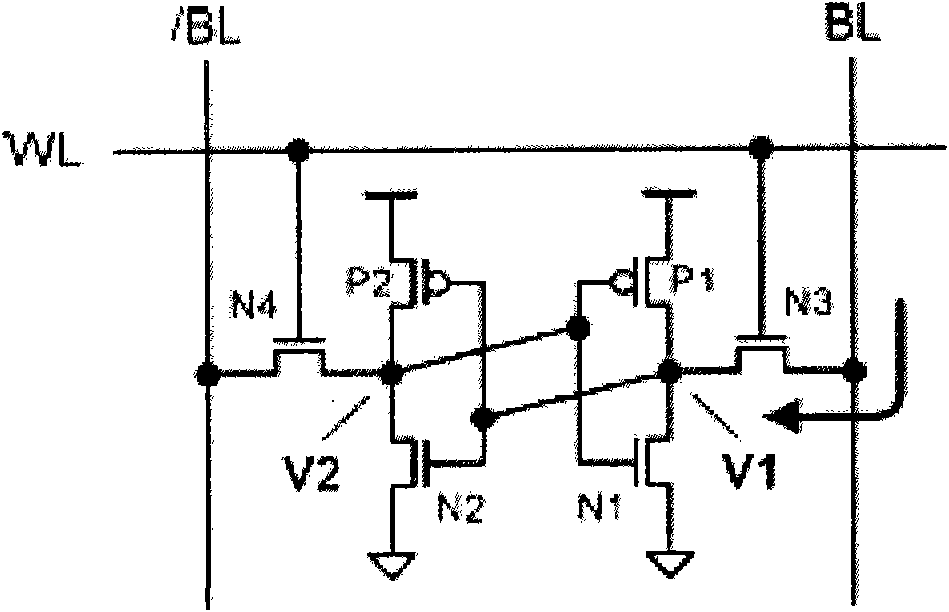

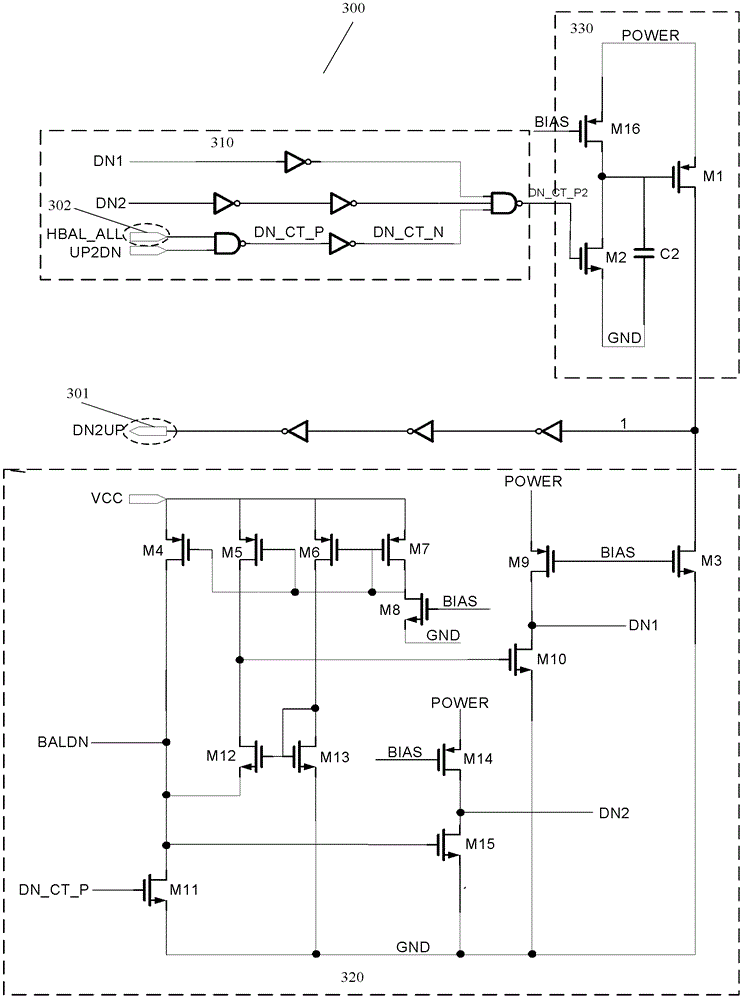

Static random-access memory

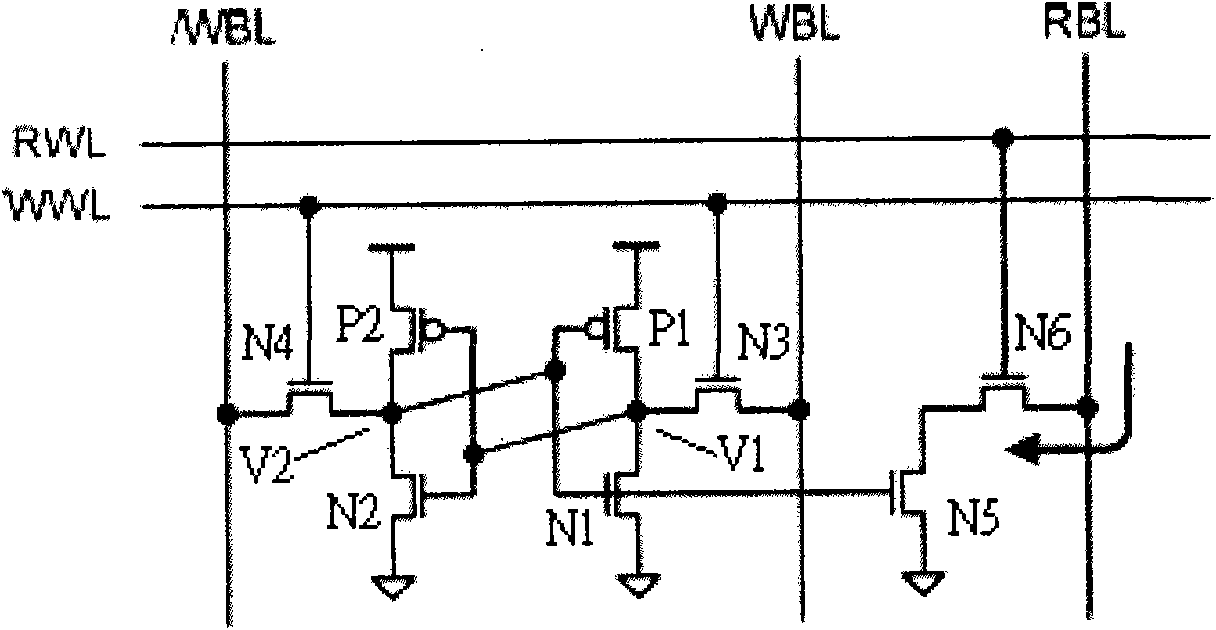

InactiveCN102117653AReduce areaTroubleshoot serial workDigital storageBit lineStatic random-access memory

The invention discloses a static random-access memory, which comprises a writing control circuit module, a first revert circuit, a second reverse circuit and a reading-out buffer circuit, wherein the writing control circuit module is used for controlling the static random access memory to write in information; the first reverse circuit comprises a PMOS (p-channel metal oxide semiconductor) transistor and a first resistor, is coupled to the writing control circuit module to form a first storage node; the second reverse circuit comprises a second NMOS (n-channel metal oxide semiconductor) transistor and a second resistor and is connected between a voltage source and a complementary voltage source; and the reading-out buffer circuit is coupled to a word-reading line and a bit-reading line and is commonly coupled to the first reverse circuit and the second reverse circuit to form a second storage node. According to the invention, the dual-port SRAM (static random access memory) is realized by using four transistors and two resistors, so that the improvement on the reading and writing speed is facilitated, and the benefits of simple circuit, less occupied space and convenience in capacity extension and layout wiring are realized.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

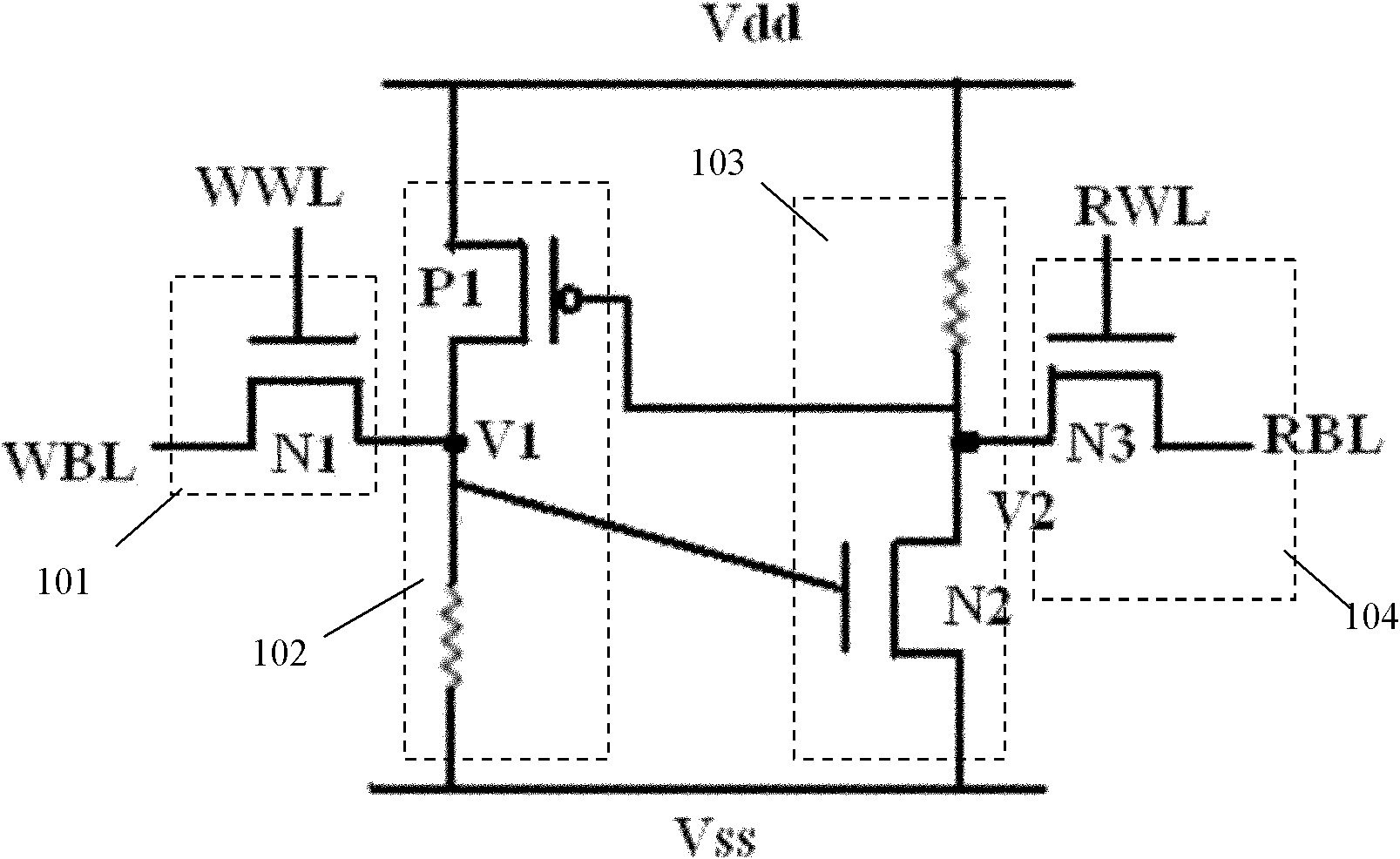

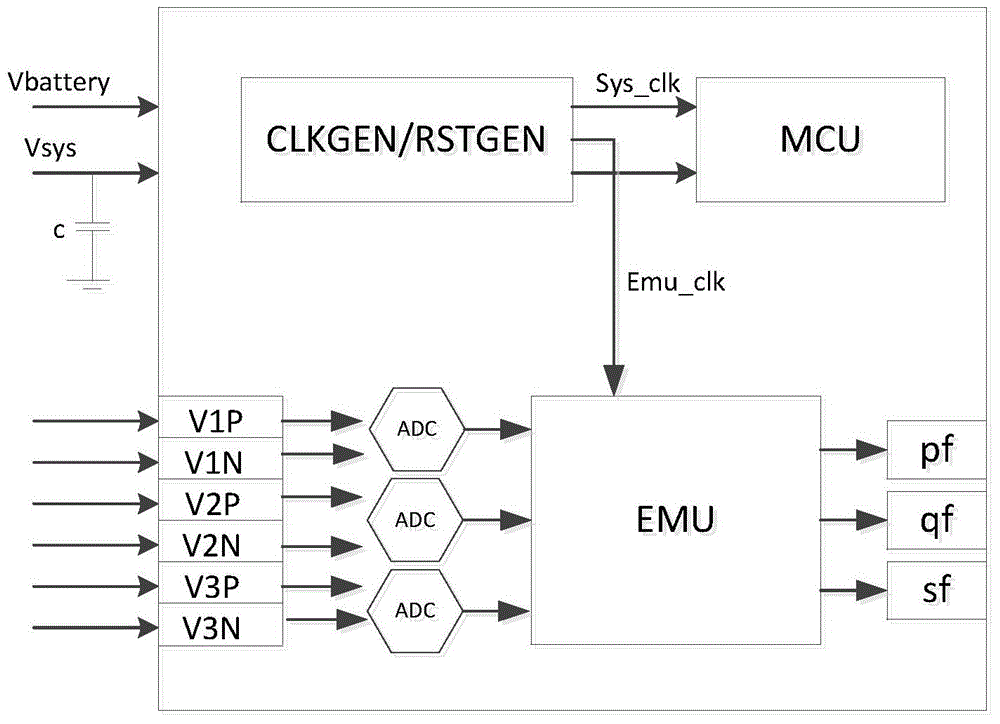

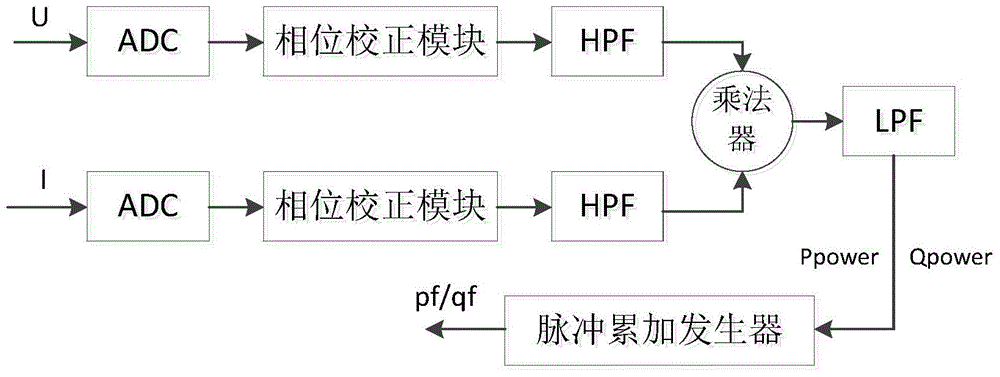

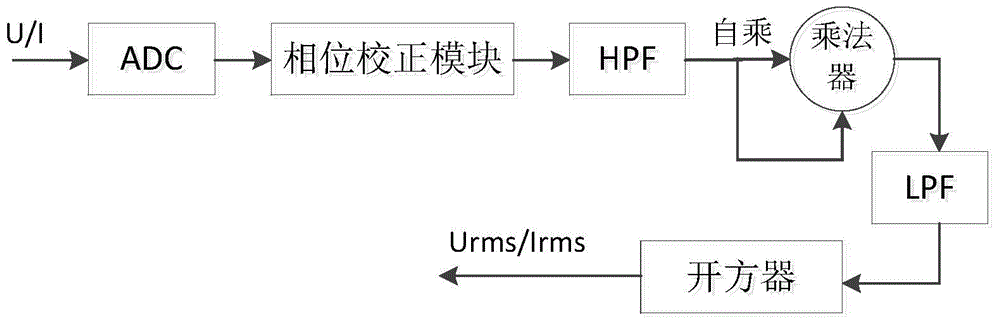

Electric energy metering method

InactiveCN104914303AReduce power consumptionOptimizing place and routeElectrical measurementsElectric energyElectricity

The invention discloses an electric energy metering method which comprises the following steps: detecting whether an electric energy metering chip for electric energy metering loses power; during power failure, switching system power supply of the electric energy metering chip to a backup electricity-taking mode; switching an electric energy metering clock of the electric energy metering chip to a low-frequency clock; and metering the electric energy in a preset time period. According to the low-frequency metering scheme provided in the invention, even if under the mode of circuit phase failure or electricity stealing, calculation of the effective value of the current can still be carried out, and meanwhile, power consumption is reduced; and the method provides apparent power and apparent power pulse output without depending on the support of specific process or devices, facilitates locating and wiring very well, and can guarantee that necessary information on the electric energy metering chip is not lost.

Owner:HI TREND TECH SHANGHAI

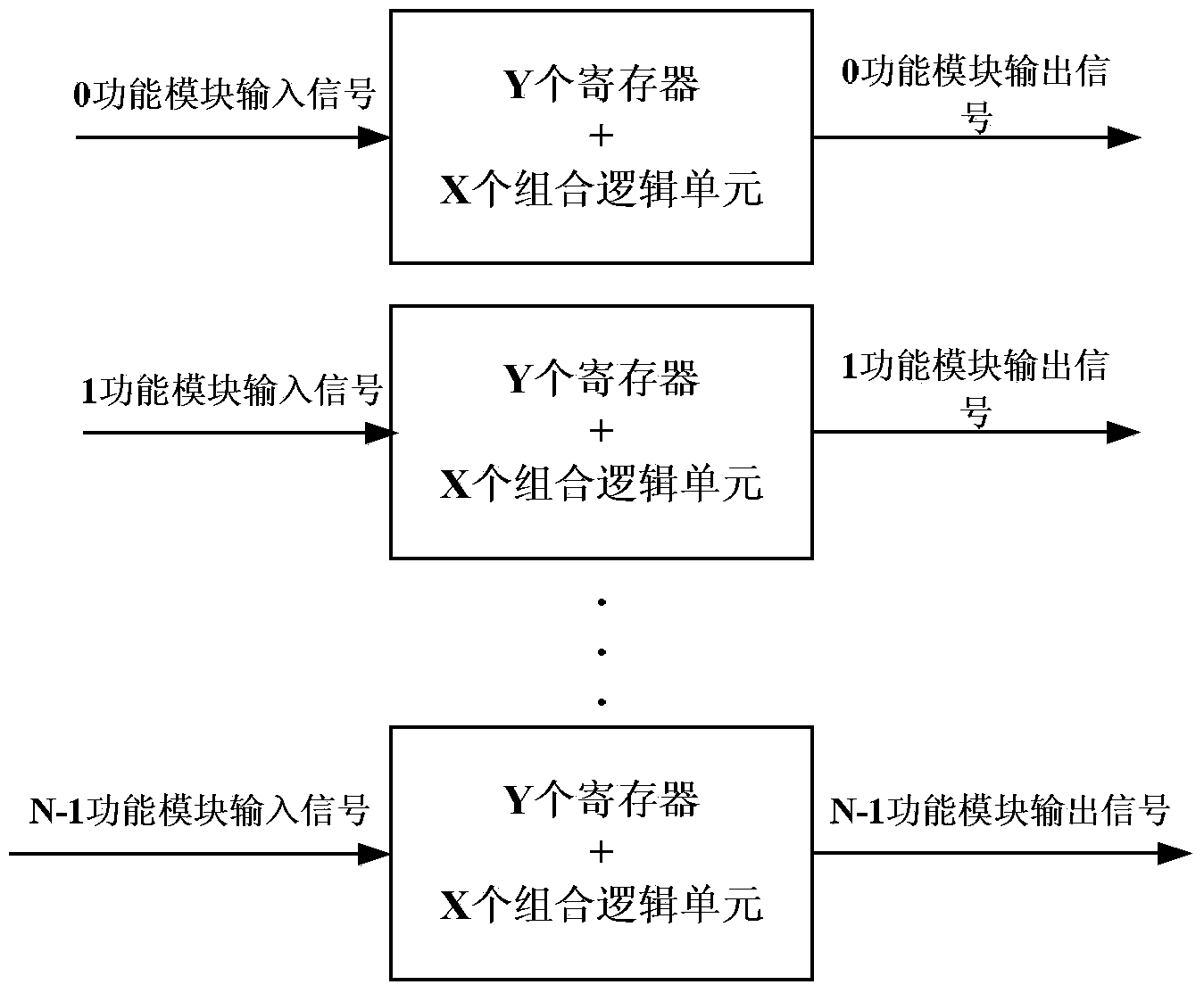

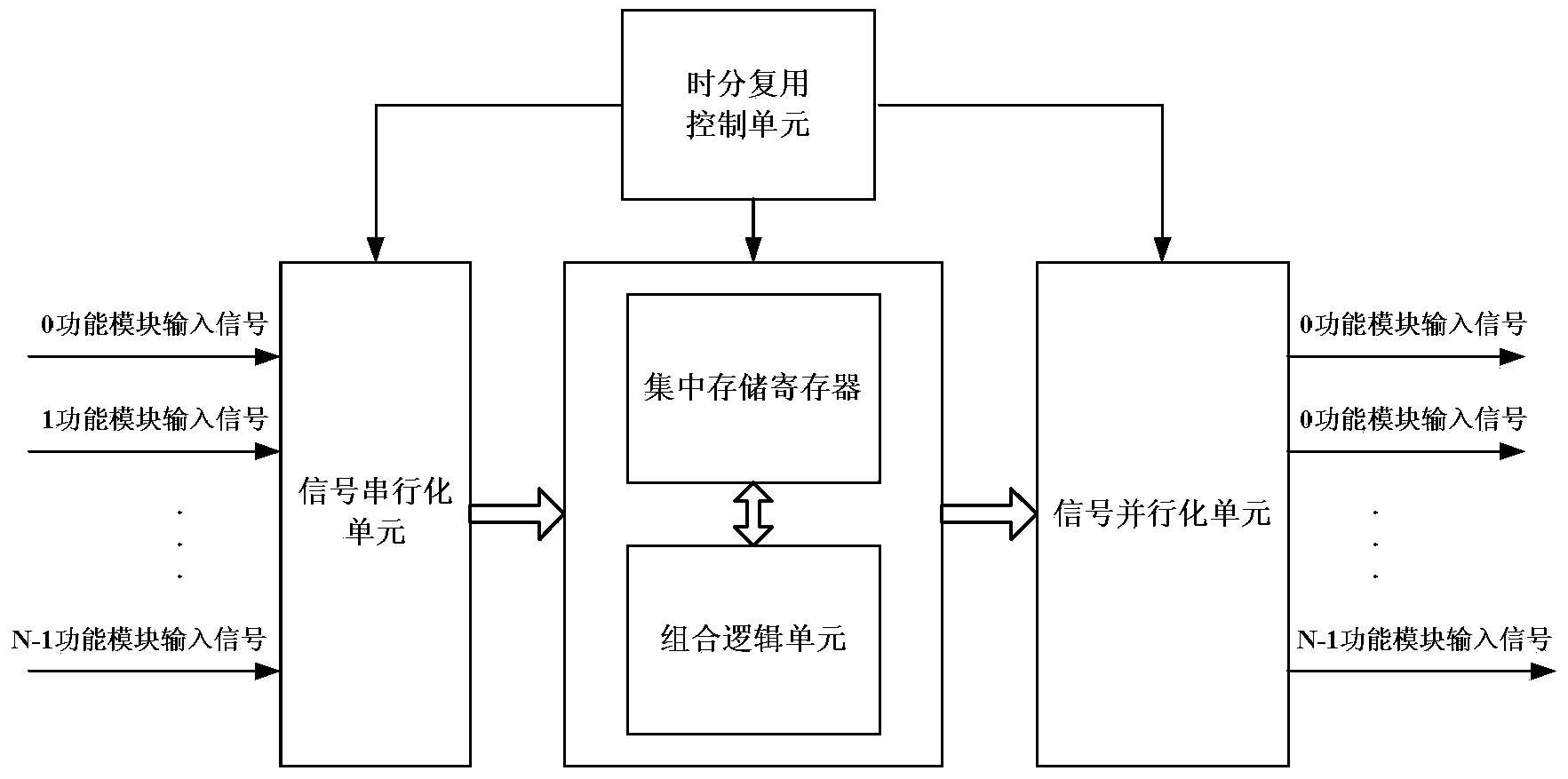

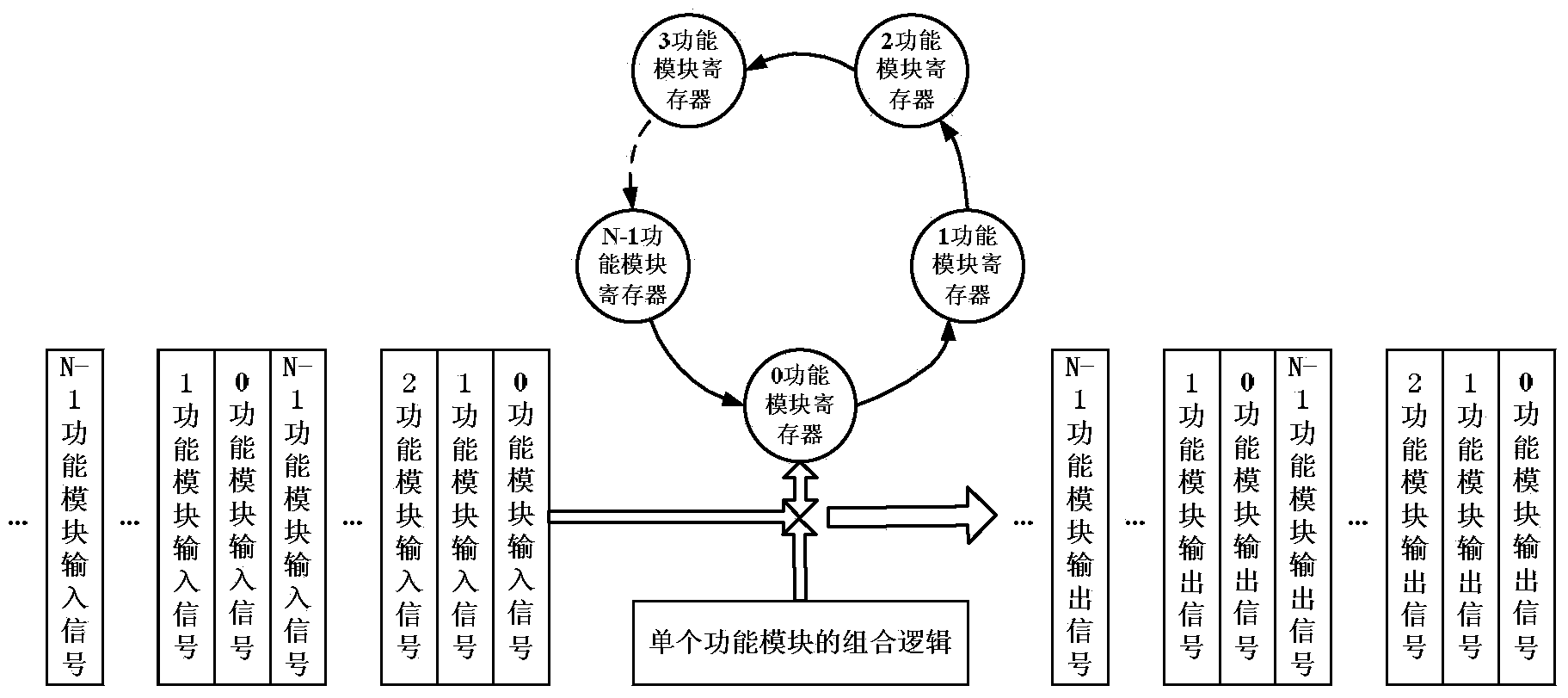

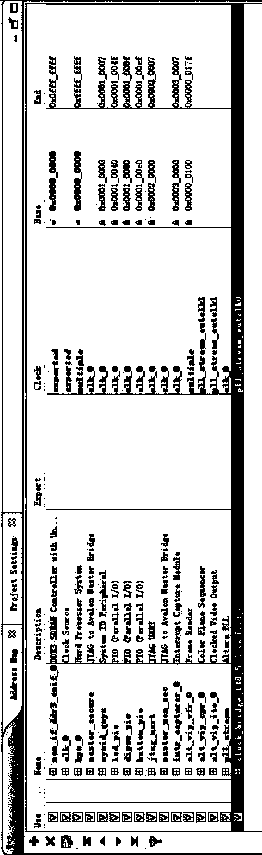

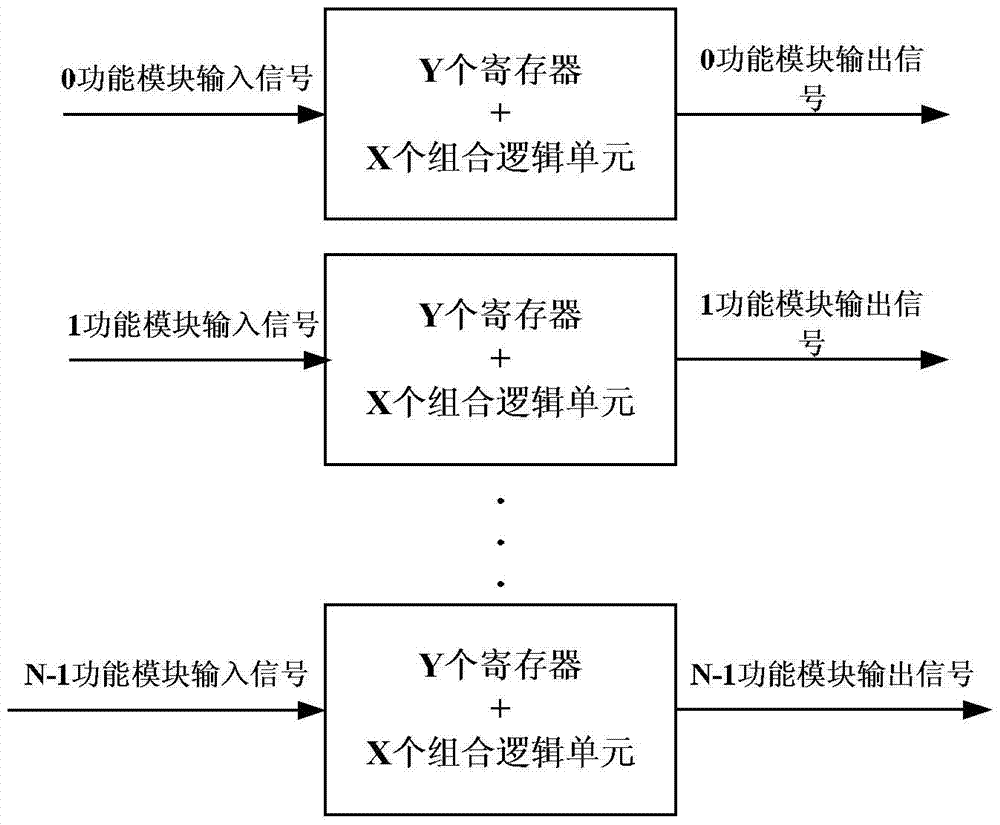

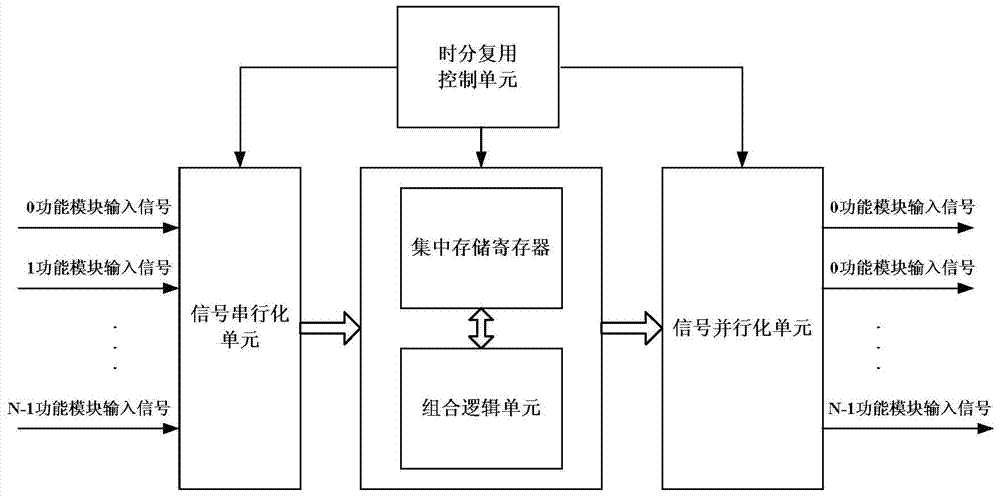

Centralized-cache device and design method based on field-programmable gate arrays

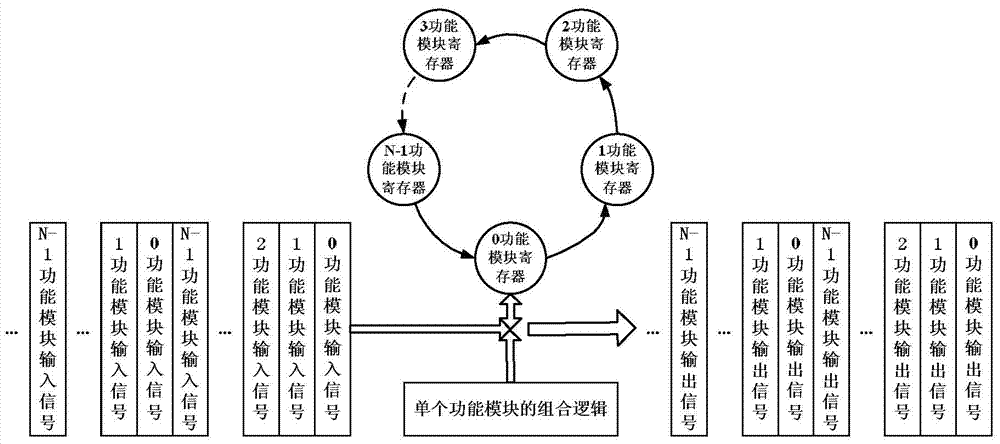

ActiveCN104252560AReduce occupancyIncrease the number ofSpecial data processing applicationsProcessor registerComputer module

The invention relates to a centralized-cache device and design method based on field-programmable gate arrays and relates to the field of field-programmable gate array design, and the centralized-cache device and design method is adaptive to at least two same functional modules. The device comprises a time division multiplexing control unit, a signal serialization unit, a centralizing storage register, a combinational logic unit and a signal parallelization unit. The time division multiplexing control unit is used for dividing the period into two time slots with the same length of time, each time slot corresponds to one functional module sequentially, and each functional module performs input signal processing in the corresponded time slot. The signal serialization unit is used for converting the parallel input signals of each functional module into serial input signals. The centralizing storage register is used for storing the register of each functional module and reading and writing the register of the functional module in the time slot corresponding to the functional module. The combinational logic unit is used for combinational logic of input signal processing of single functional module. The signal parallelization unit is used for restoring serial output signals as parallel output signals after the input signals of each functional module are processed.

Owner:FENGHUO COMM SCI & TECH CO LTD

PCIe board card resource allocation method and device

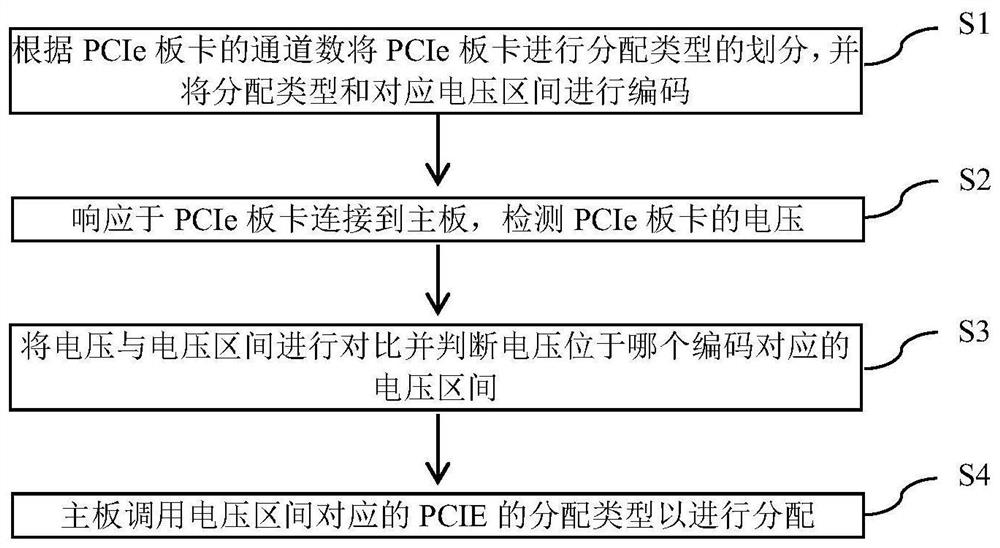

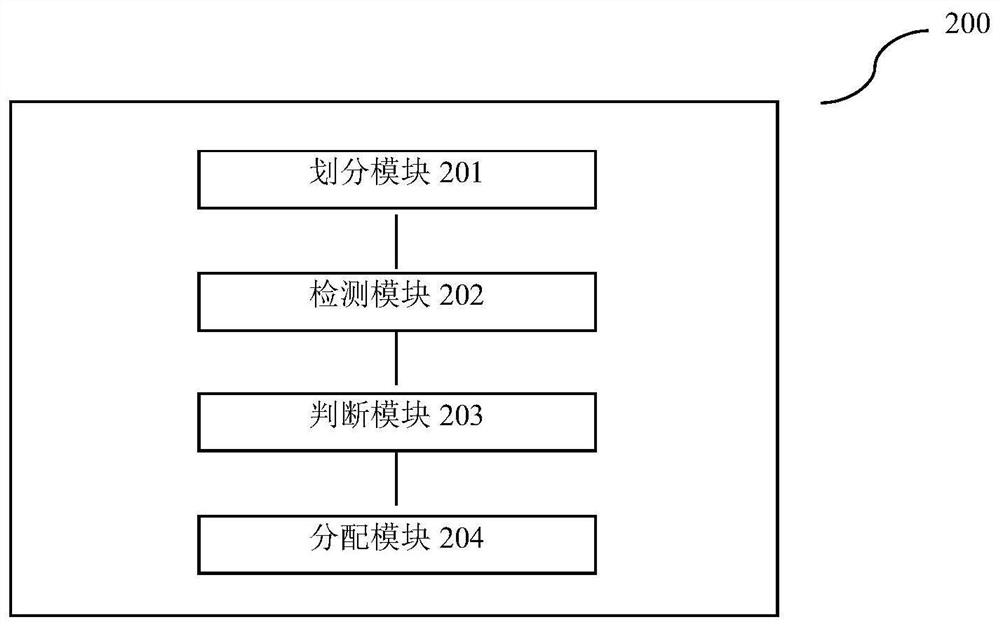

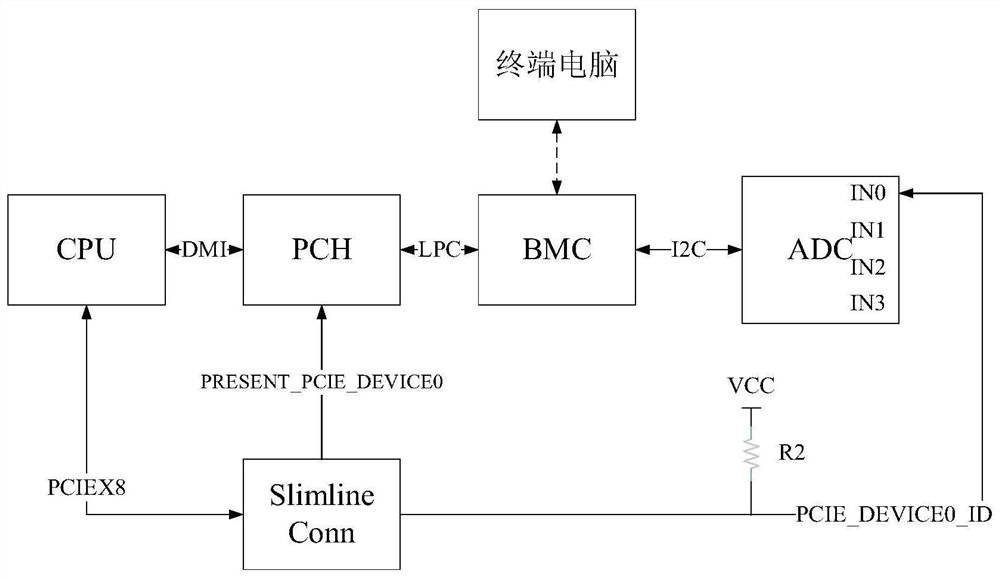

ActiveCN111708724AOptimizing place and routeReduce usageHardware monitoringProgram controlResource assignmentEmbedded system

The invention provides a PCIe board card resource allocation method and device, and the method comprises the following steps: dividing the allocation types of PCIe board cards according to the numberof channels of the PCIe board cards, and coding the allocation types and corresponding voltage intervals; detecting the voltage of the PCIe board card in response to the connection of the PCIe board card to the mainboard; comparing the voltage with the voltage interval and judging which code the voltage is located in the corresponding voltage interval; enabling the mainboard to call the distribution type of the PCIe corresponding to the voltage interval to perform distribution. By using the scheme of the invention, the use of IO ports of the mainboard can be greatly reduced, PCB layout and wiring are facilitated, and the method is simple to implement, low in software cost and beneficial for users to realize remote monitoring.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Static random access memory

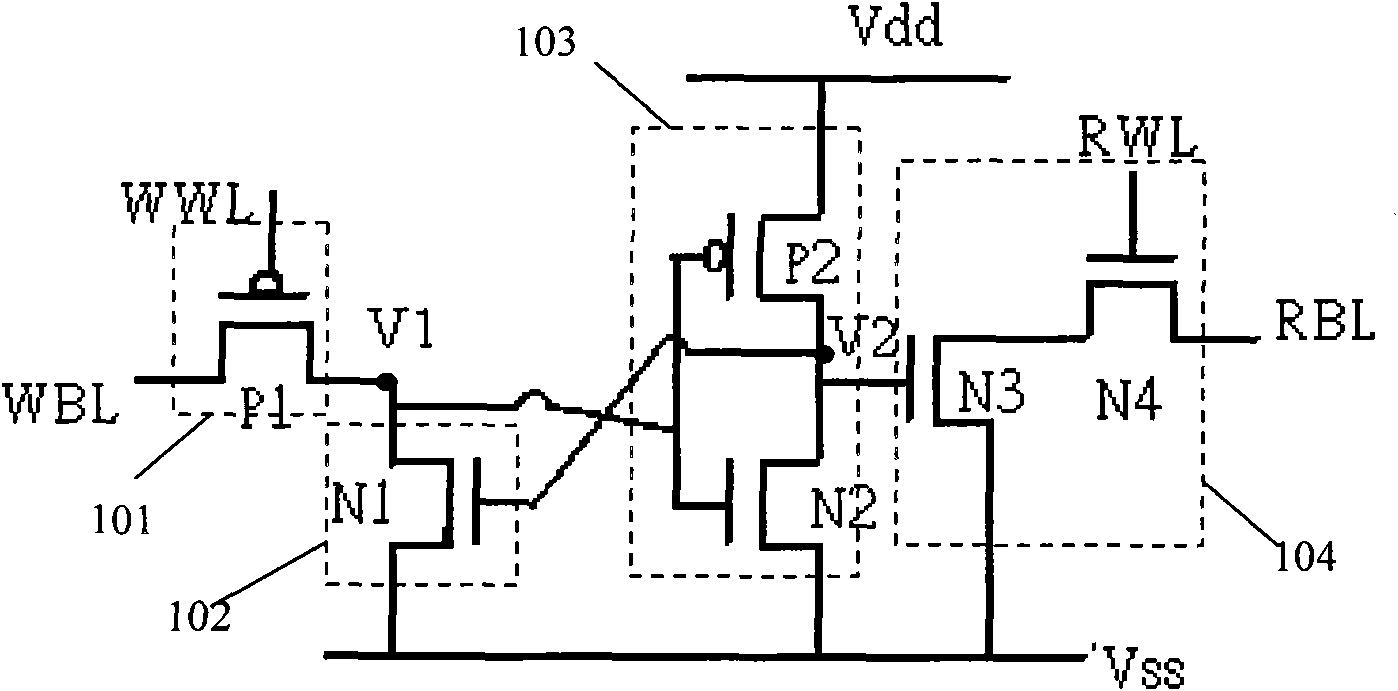

ActiveCN101877243AWill not affect the original voltageAvoid read disturbDigital storageStatic random-access memoryRandom access memory

The invention discloses a static random access memory comprising a writing control circuit module, a first inverter circuit, a second inverter circuit and a reading buffer circuit, wherein the writing control circuit module is used for controlling the static random access memory; the first inverter circuit is coupled with the writing control circuit module to form a first storage node; the second inverter circuit is connected between a voltage source and a complementary voltage source; and the reading buffer circuit is coupled to a reading word line and a reading bit line and is coupled together with the first inverter circuit and the second inverter circuit to form a second storage node. The invention isolates the reading bit line from the second storage node by utilizing the reading buffer circuit and controls the state of information written by the static random access memory, thereby solving the problem of reading interference existing in the prior art.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

DC micro-grid system and charging loop circuit and control method thereof

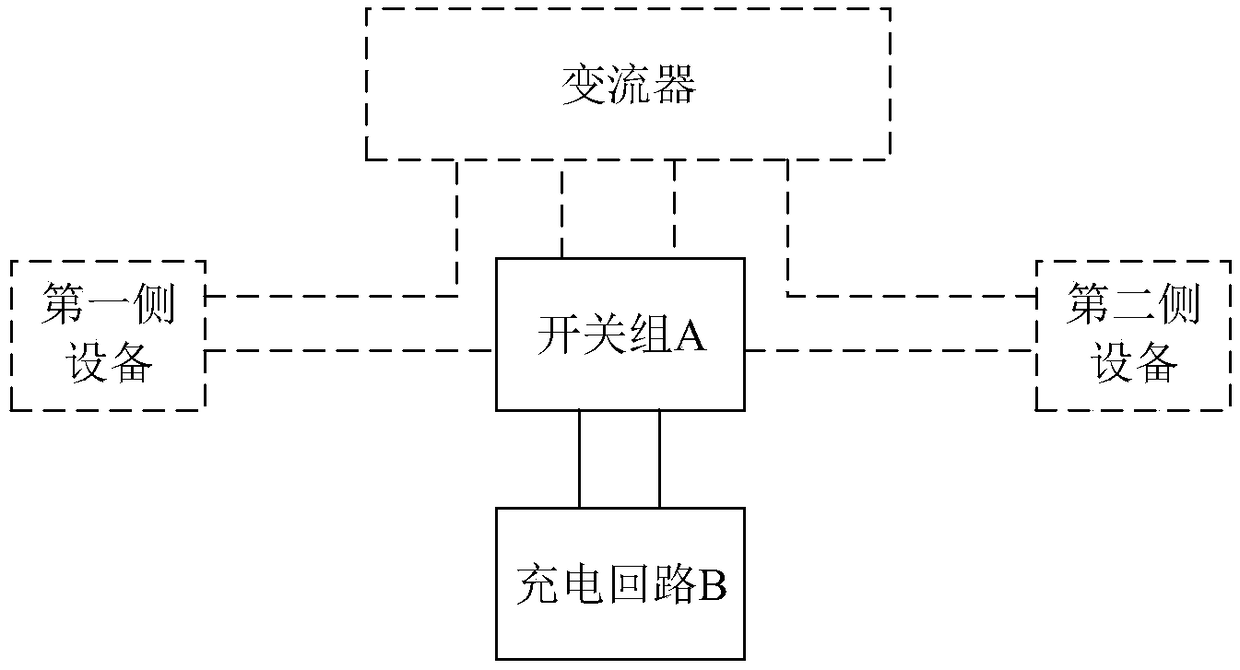

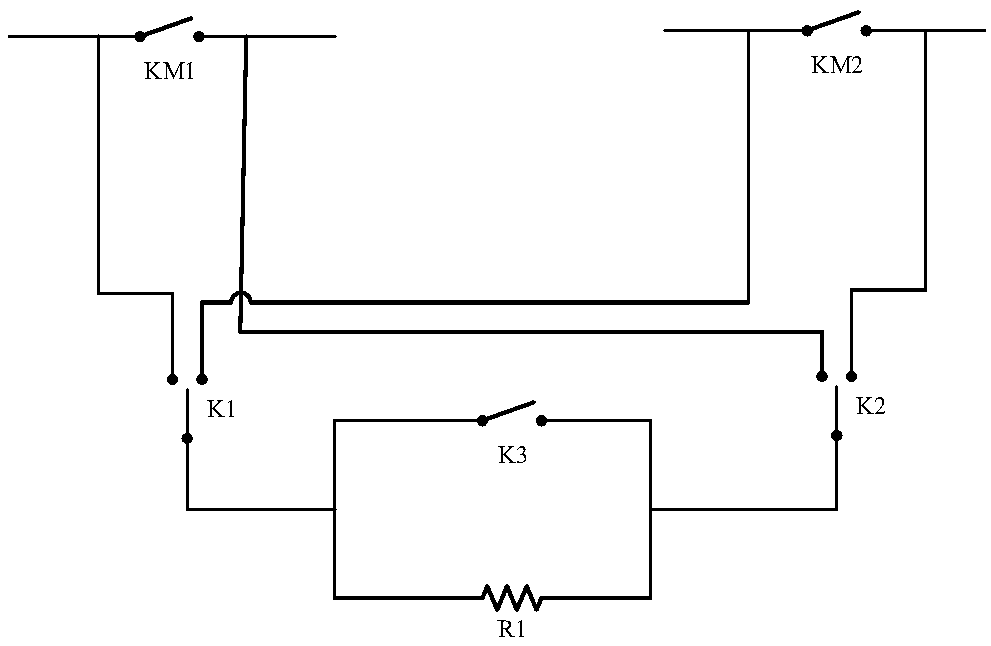

ActiveCN108832695ASolve wasteReduce in quantityApparatus without intermediate ac conversionElectric powerEngineeringMicro grid

The invention provides a DC micro-grid system and a charging loop circuit and a control method thereof. The charging loop circuit enables a charging loop to be selectively connected to a first side loop or a second side loop through a switch group. The DC micro-grid system and the charging loop circuit and the control method thereof solve the problem of resource waste caused since the charging loops need to be designed on both sides of a converter, thereby reducing the device number of the charging loop, saving cost, saving space and helping to optimize PCB locating and wiring.

Owner:GREE ELECTRIC APPLIANCES INC

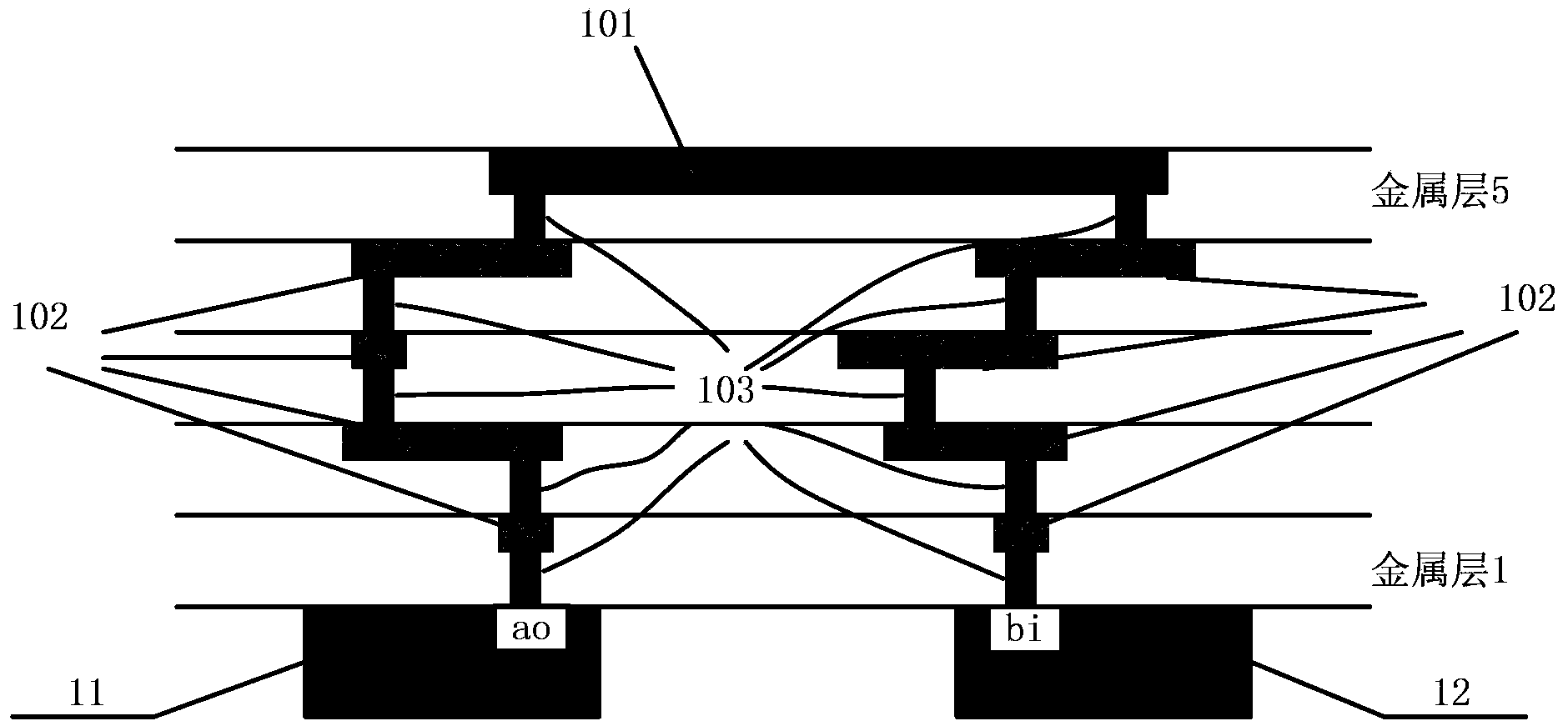

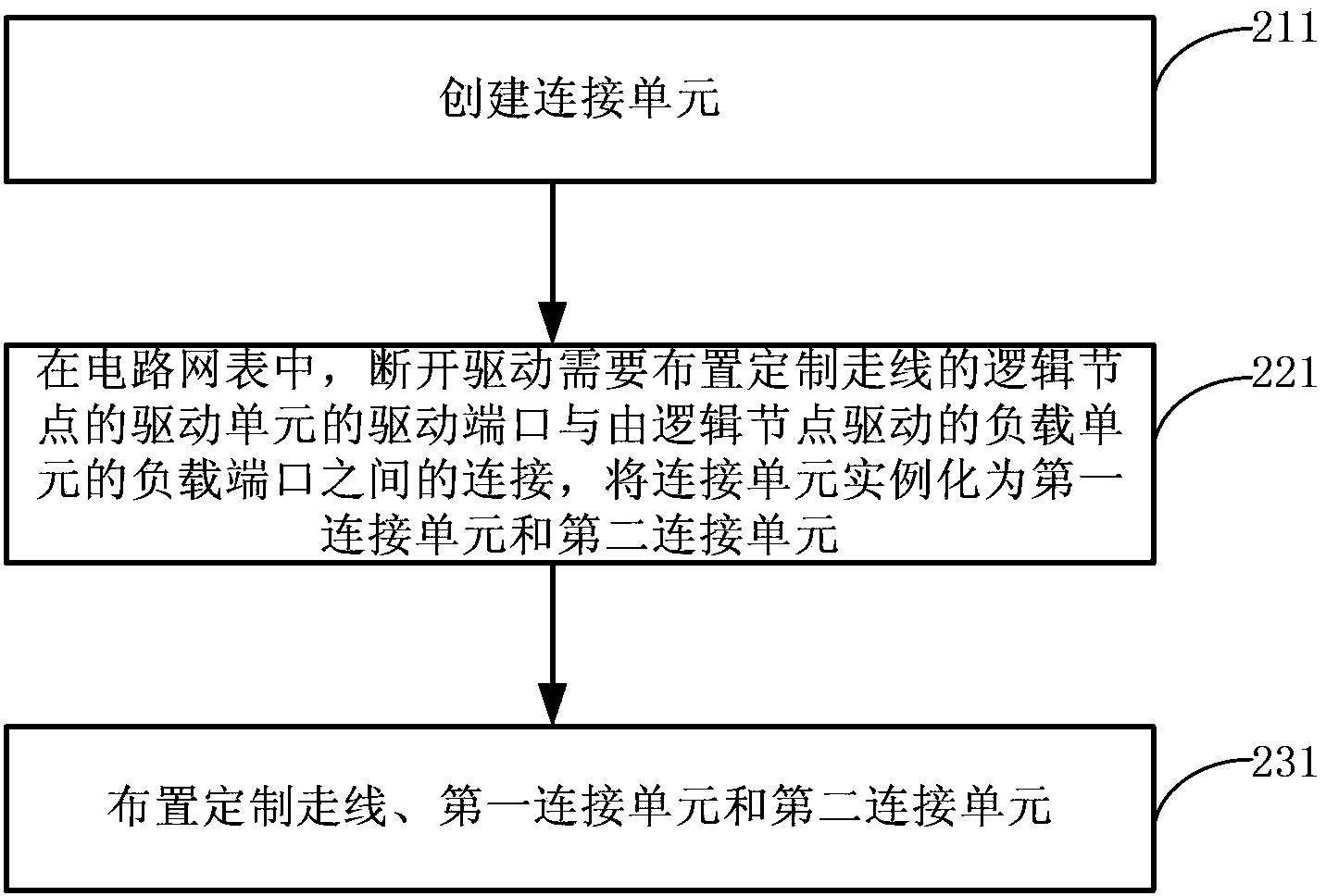

Method for customizing wiring in integrated circuit

ActiveCN103366046AReduce workloadLess interferenceSolid-state devicesSpecial data processing applicationsWorkloadIntegrated circuit design

The invention relates to a method for customizing wiring in an integrated circuit. The method comprises the following steps: creating a connection unit; disconnecting the connection between a drive port of a drive unit for driving a logic node requiring distribution of a customized wire and a load port of a load unit driven by the logic node, instantiating the connection unit into a first connection unit and a second connection unit; distributing the customized wire, the first connection unit and the second connection unit, wherein one end of the customized wire is in contact with an output port of the first connection unit, and the other end of the customized wire is in contact with an input port of the second connection unit. The method achieves customized wiring, meanwhile, the workload of manual operation of design staff is greatly reduced, and the optimization of locating and wiring by an automated tool is not affected.

Owner:KTMICRO ELECTRONICS

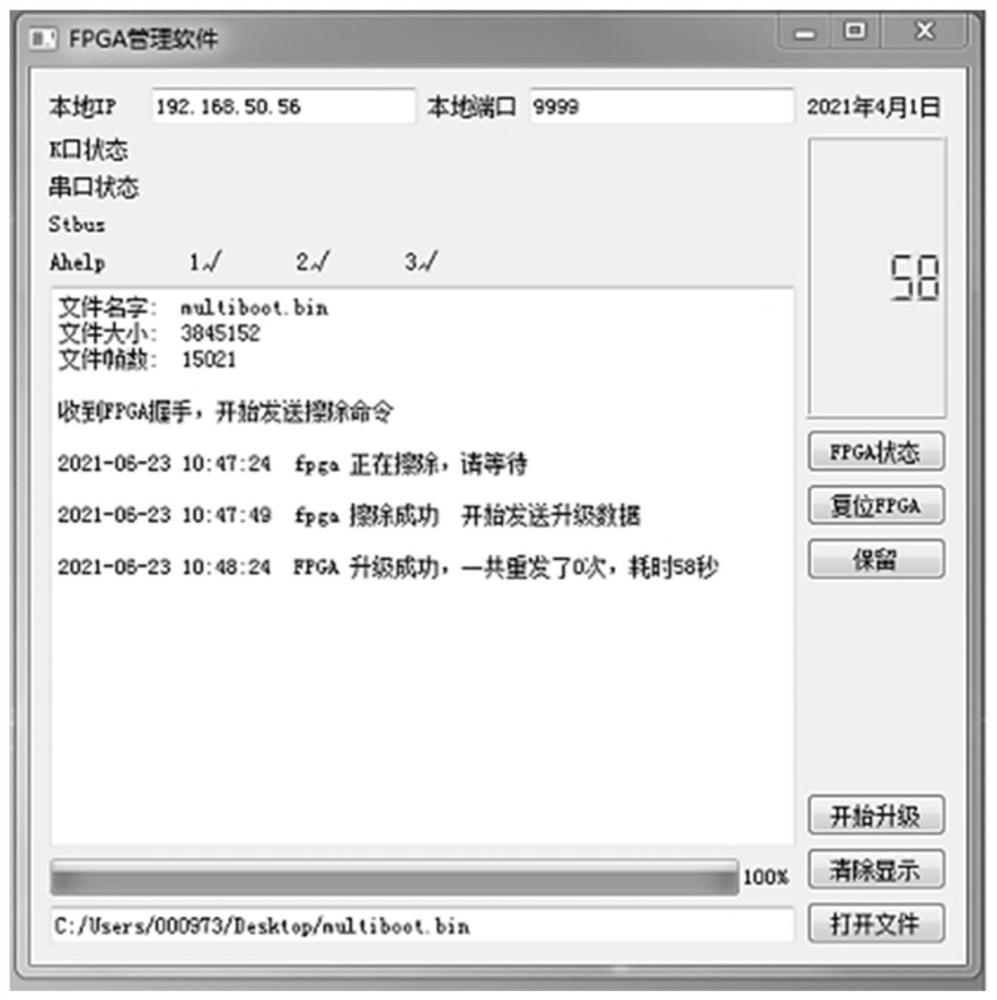

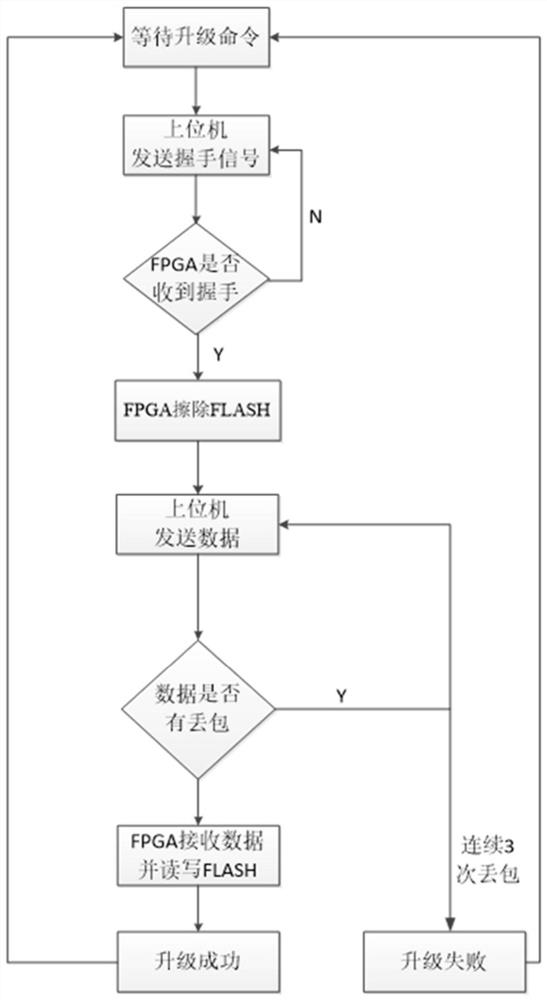

Remote upgrading system and method based on FPGA and medium

PendingCN113703803AAvoid repeated disassemblyPerformance is not affectedTransmissionArchitecture with single central processing unitComputer hardwareComputer architecture

The invention provides a remote upgrading system and method based on an FPGA and a medium. The system comprises an upper computer, the FPGA and a FLASH chip. The method comprises the steps that an upper computer selects a BIN file to be upgraded, issues a handshake frame and waits for an FPGA to reply an acknowledgement frame; after receiving the FPGA handshake acknowledgement frame, the upper computer sends an erasure frame; when the FPGA executes the command to successfully erase the FLASH, an erasing success confirmation frame is replied to the upper computer, and the upper computer starts to issue a data frame to be upgraded; the FPGA writes the data into the FLASH; and after all data to be upgraded are written into the FLASH, the FPGA reports an acknowledgement frame to the upper computer, and the upgrade is finished. According to the invention, the FPGA program is updated more simply and conveniently, the PCB circuit design is more optimized, the updating rate of the FPGA is improved, and the remote updating of the FPGA becomes safe and reliable.

Owner:上海微波技术研究所(中国电子科技集团公司第五十研究所)

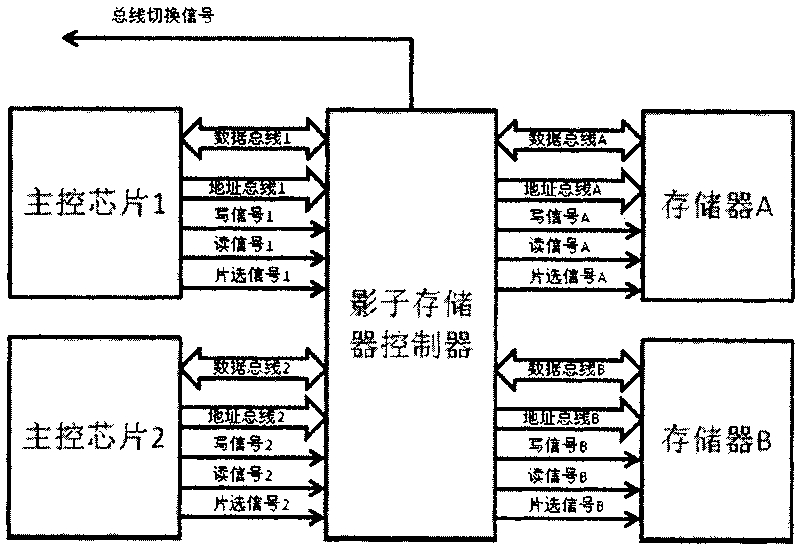

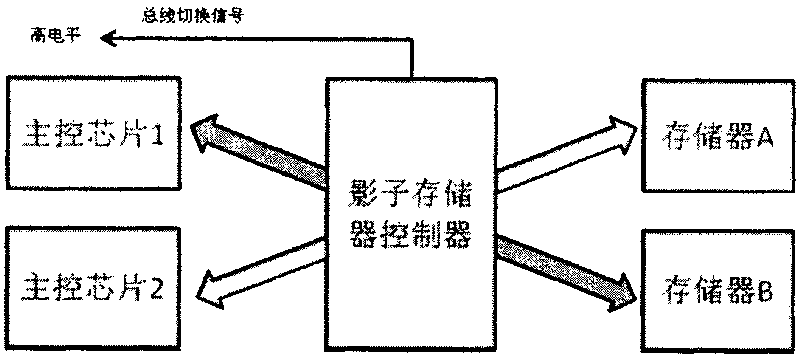

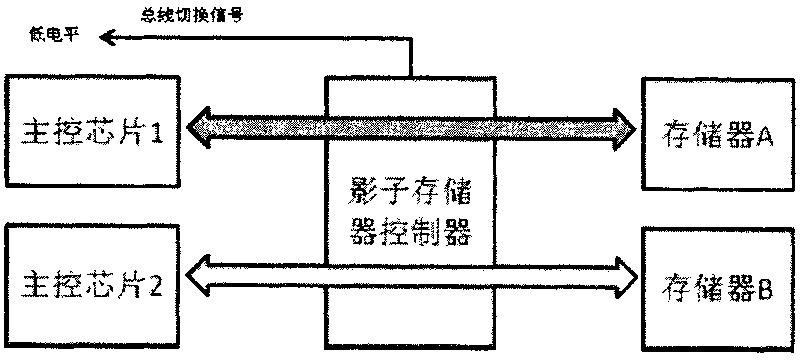

High-speed shadow memory control structure

InactiveCN101719109ARealize independent control functionImprove performanceElectric digital data processingTime rangeControl signal

The invention relates to a high-speed shadow memory control structure, which comprises two memories which are mutual shadows. The high-speed shadow memory control structure has the main technical characteristics that the two memories are connected with a shadow memory controller through two groups of data buses, address buses and control signals respectively; the shadow memory controller is also connected with two main control chips through the other two groups of address data buses, address buses and control signals respectively; and a bus switching signal port of the shadow memory controller is connected with any one of the main control chips or other logic switching chip. The independent control functions of the main control chips to the shadow memories are achieved by adopting a fully parallel processing structure, the two main control chips have full read-write rights for the current accessed memory in an entire time range so as to improve the data access speed and read accuracy, and the high-speed shadow memory control structure has the characteristics of flexible control, convenient use and the like.

Owner:天津物联传感科技有限公司

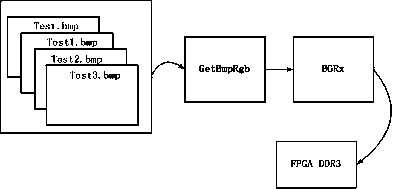

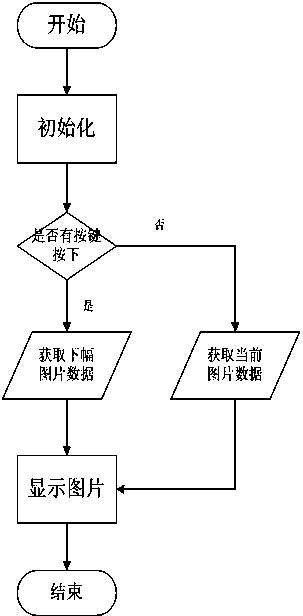

HPS-based OSD interface switching scheme of FPGA

InactiveCN103995598AReduce power consumptionReduce chip countInput/output for user-computer interactionSpecific program execution arrangementsEmbedded systemComputer hardware

The invention provides an HPS-based OSD interface switching scheme of an FPGA and belongs to the field of computers. According to the scheme, the FPGA with a hardcore (HPS) is used as a control unit, a peripheral module of the hardcore is set up through the FPGA, RGA signals are output, so that pictures are displayed on a display screen through a DA conversion chip, and switching between the pictures is controlled through a keyboard. Through the scheme, power consumption is reduced, the number of chips is reduced, and locating and wiring of a PCB of a management panel can be performed conveniently.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

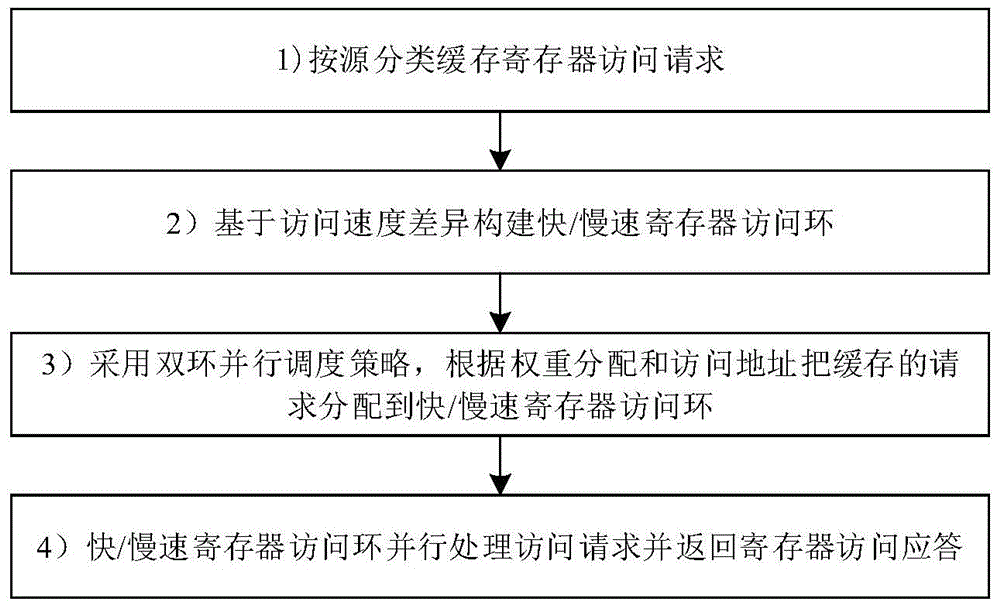

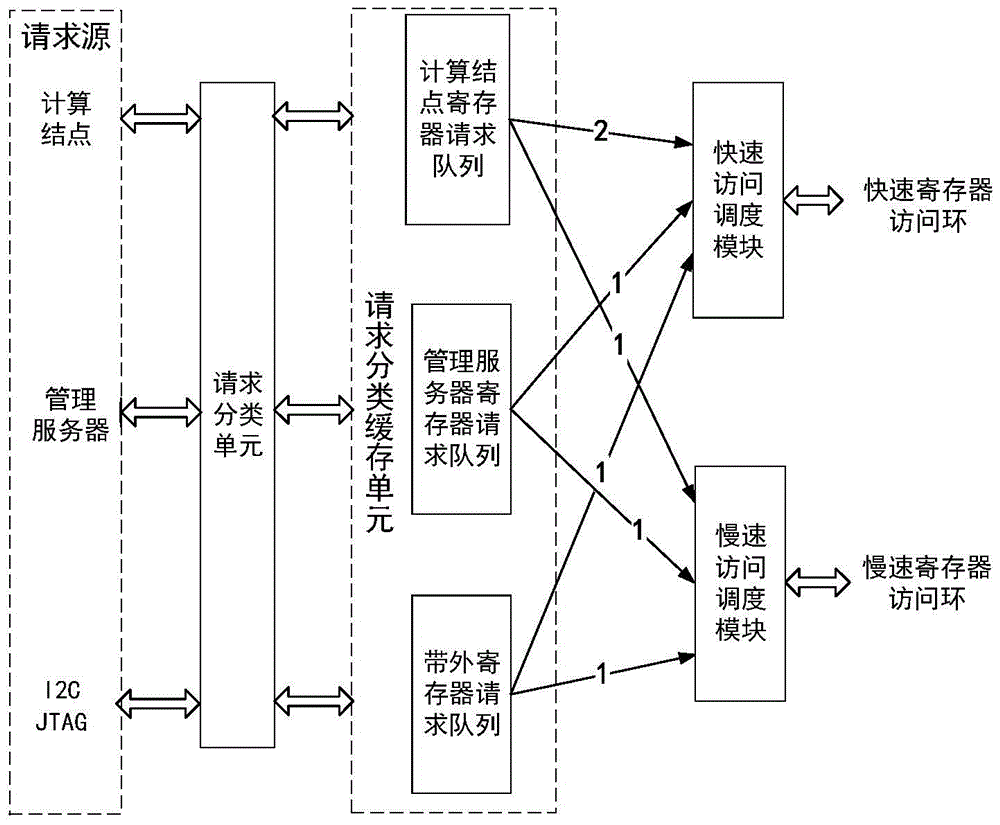

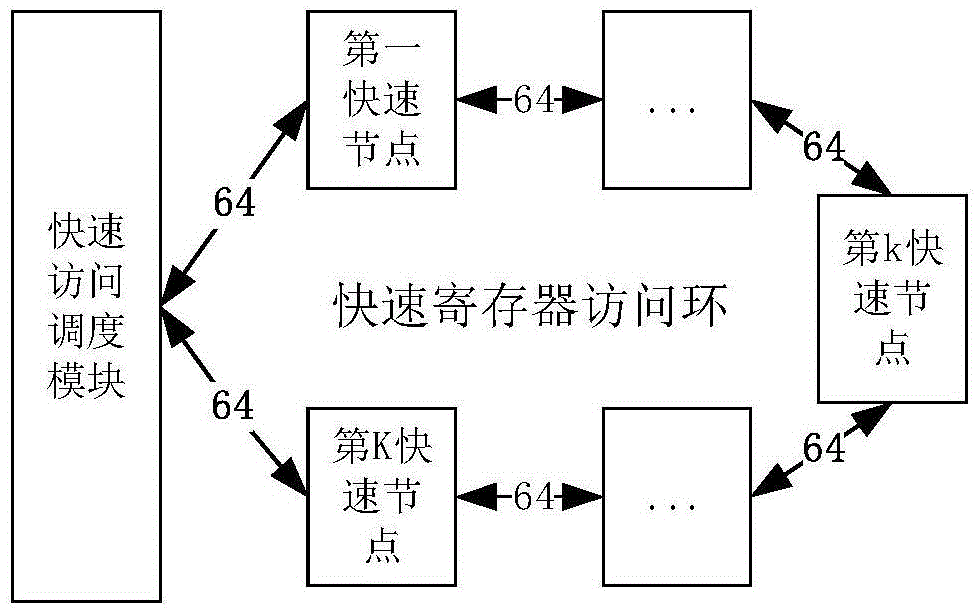

Multi-source access scheduling method and device for registers of network interface chip

InactiveCN105718393AReduce access latencyRealize reasonable schedulingElectric digital data processingExtensibilityProcessor register

The invention discloses a multi-source access scheduling method and device for registers of a network interface chip.The method comprises the following steps that register access requests are cached in a classified mode according to sources; quick / slow register access rings are structured based on access speed differences; a double-ring parallel scheduling strategy is adopted, and the cached requests are allocated to the quick / slow register access rings according to weight allocation and access addresses; the quick / slow register access rings handle the access requests in parallel and return register access responses.The device comprises a request classifying unit, a request classified caching unit, a quick access scheduling module, a slow access scheduling module, the quick resister access ring and the slow register access ring.According to the multi-source access scheduling method and device for the registers of the network interface chip, the double-ring parallel scheduling strategy is adopted, different request sources are reasonably scheduled, the differentiated demand for access speeds of different request sources is met, an in-band and out-band combined multi-way configuring and monitoring function is provided, layout and wiring at the back end can be easier, and good expandability is achieved.

Owner:NAT UNIV OF DEFENSE TECH

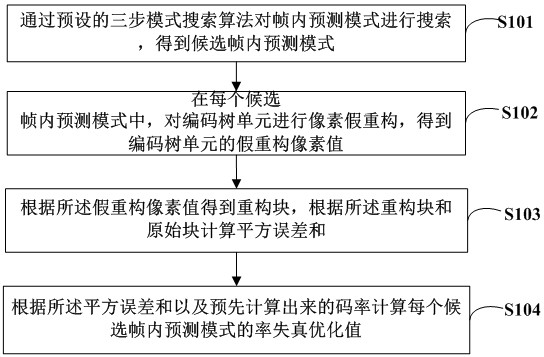

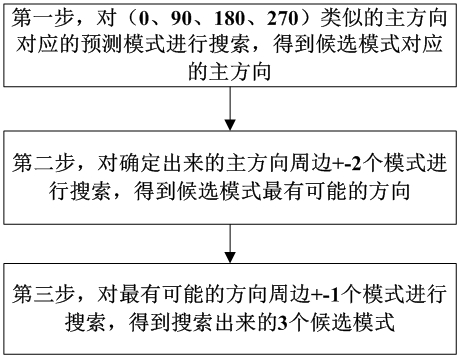

Method and device for improving rate distortion optimization calculation efficiency, equipment and storage medium

ActiveCN113347417AResolve dependenciesReduce complexityDigital video signal modificationComputation complexityRound complexity

The invention discloses a method, device and equipment for improving rate distortion optimization calculation efficiency and a storage medium, and the method comprises the steps: searching an intra-frame prediction mode through a preset three-step mode search algorithm, and obtaining a candidate intra-frame prediction mode; in each candidate intra-frame prediction mode, carrying out pixel false reconstruction on the coding tree unit to obtain a false reconstruction pixel value of the coding tree unit; obtaining a reconstruction block according to the false reconstruction pixel value, and calculating a square error sum according to the reconstruction block and the original block; and calculating a rate distortion optimization value of each candidate intra-frame prediction mode according to the square error sum and a pre-calculated code rate. According to the method for optimizing the calculation efficiency through rate distortion provided by the embodiment of the invention, the calculation complexity is lower, the data dependence between the blocks is completely removed, and better hardware time sequence and better layout and wiring can be achieved.

Owner:杭州博雅鸿图视频技术有限公司

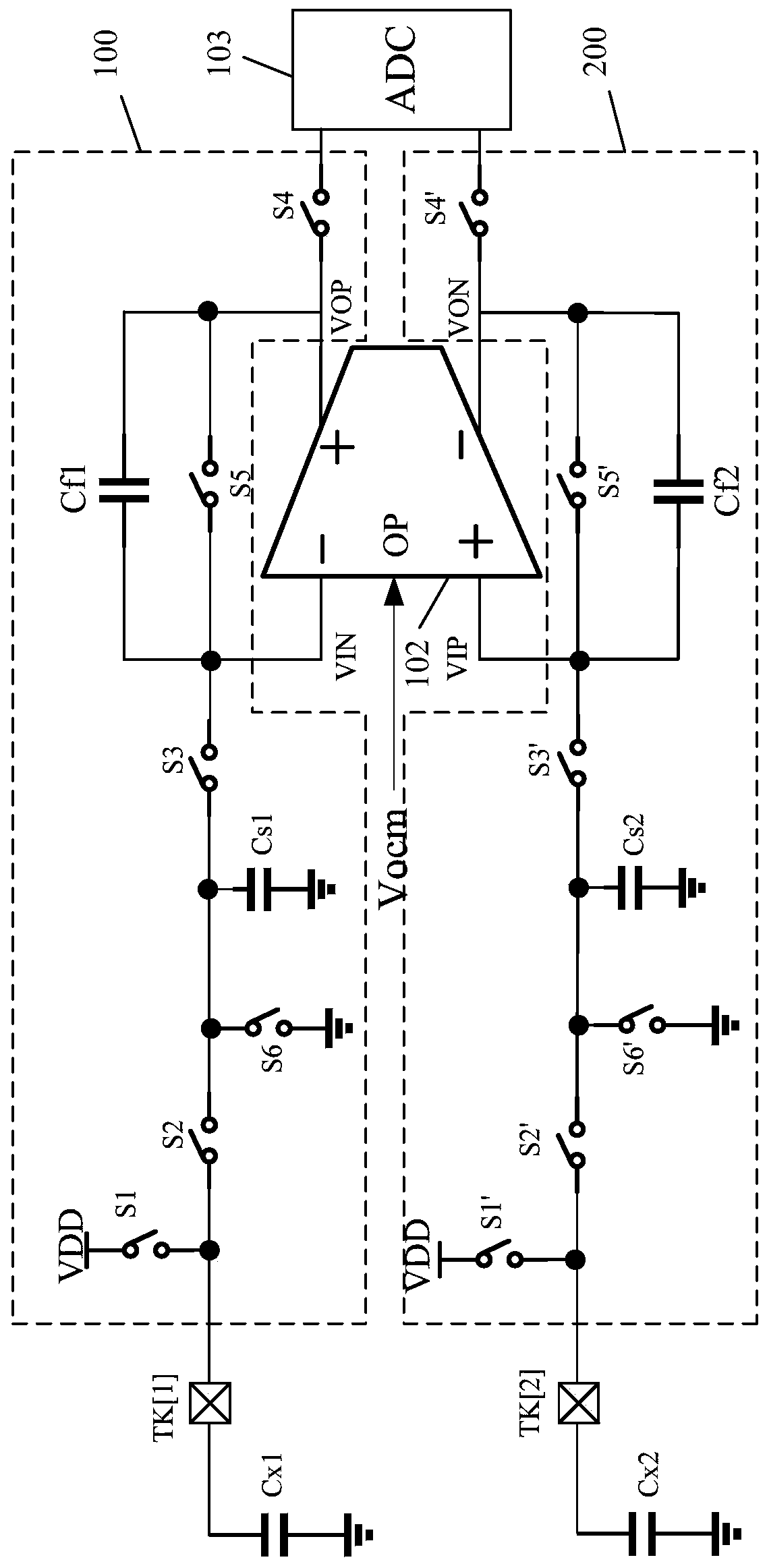

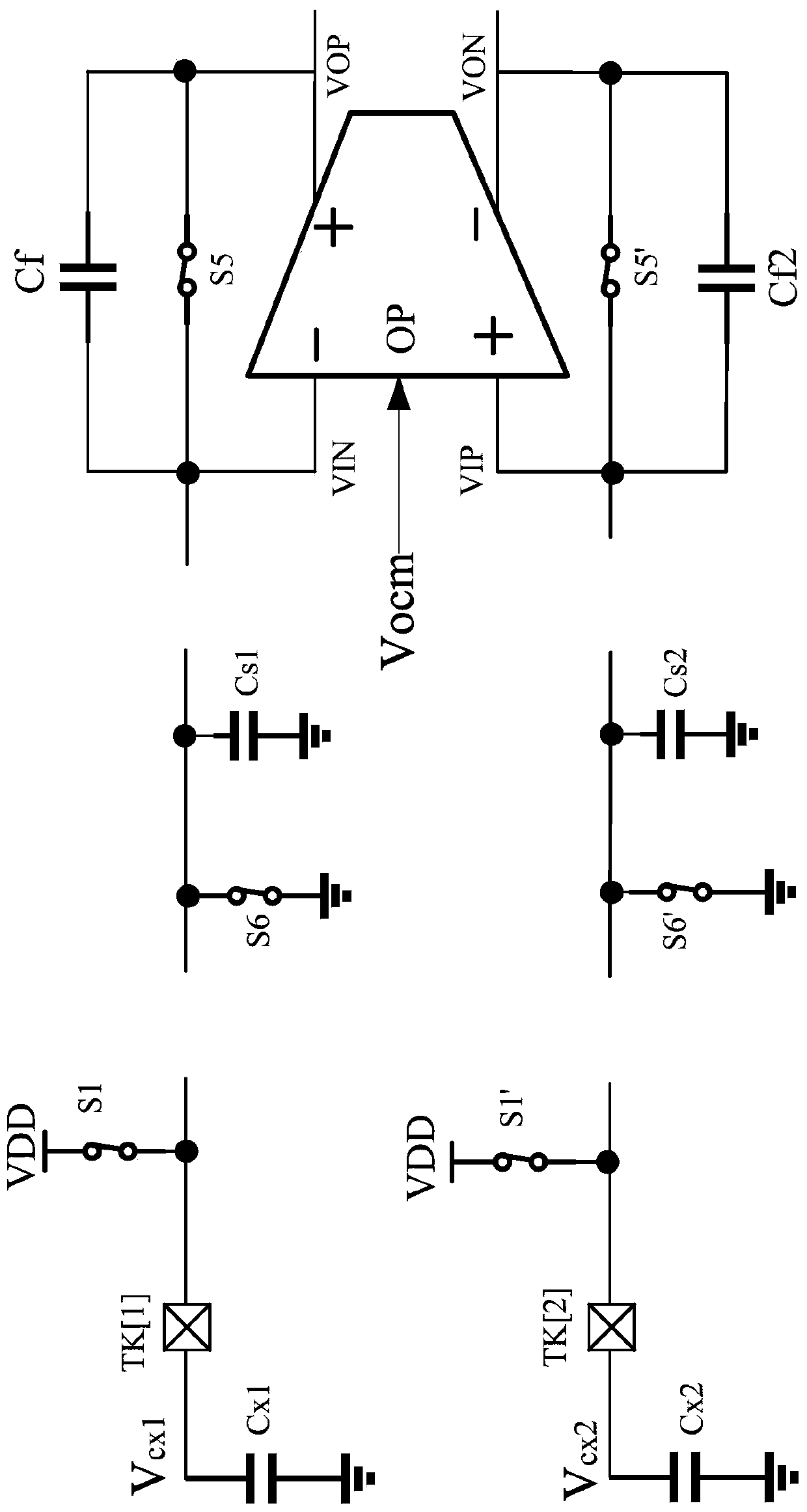

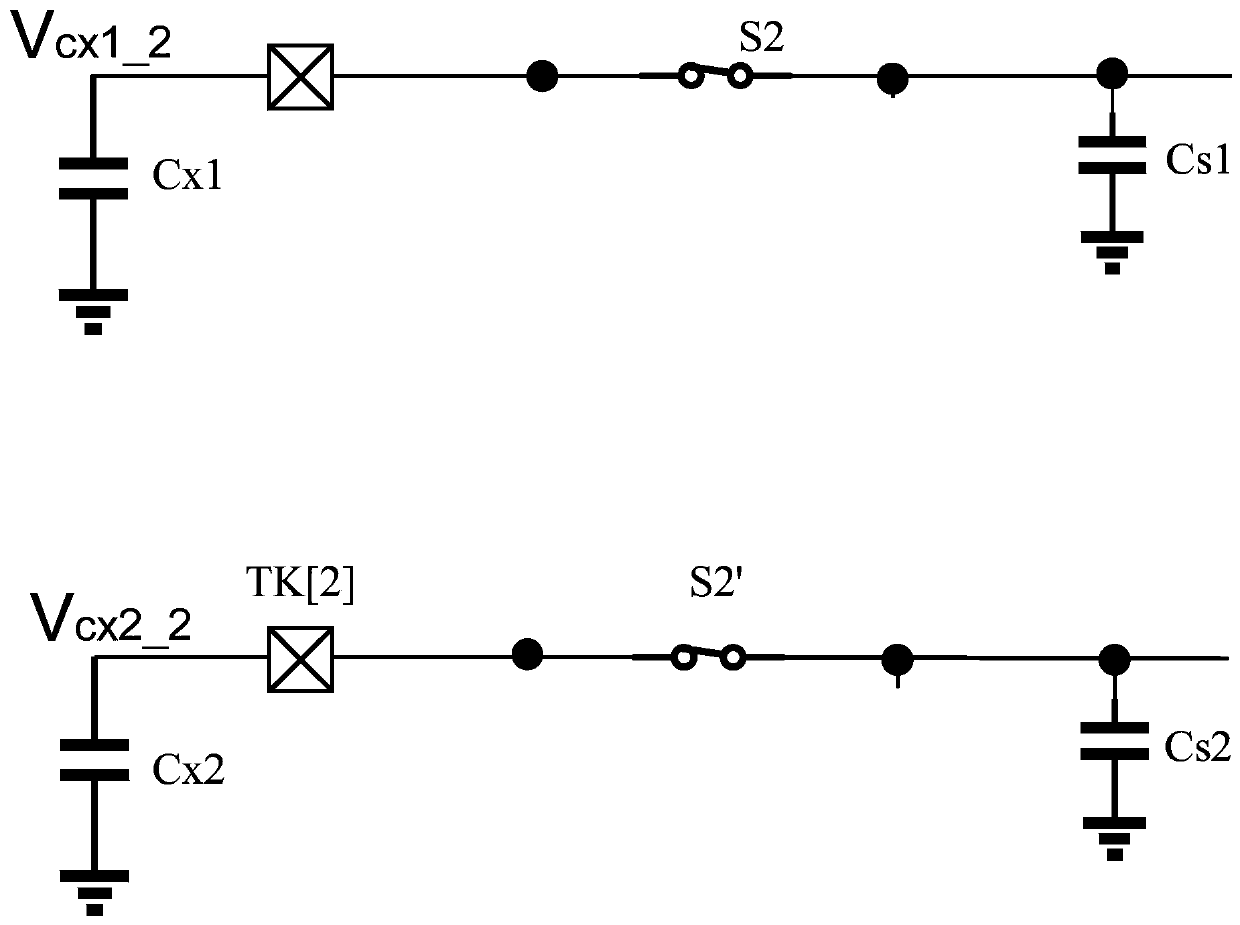

Differential touch detection circuit and touch judgment method adopting the differential touch detection circuit

ActiveCN110798195AEliminate the effects ofOptimizing place and routeElectronic switchingParasitic capacitorTerminal voltage

The invention provides a differential touch detection circuit and a touch judgment method adopting the differential touch detection circuit. The differential touch detection circuit comprises a firstchannel circuit, a second channel circuit, a differential operational amplifier and an analog-to-digital converter, and the first channel circuit and the second channel circuit have the same connection structure. Wherein the first channel circuit corresponds to a first channel, and the first parasitic capacitor Cx1 is coupled with the first channel circuit through the first touch sensor TK1; the first channel circuit is coupled to a negative input end voltage VIN and a positive output end voltage VOP of the differential operational amplifier. The second channel circuit corresponds to a secondchannel, and a second parasitic capacitor Cx2 is coupled with the second channel circuit through a second touch sensor TK2; the second channel circuit is coupled to the positive electrode input end voltage VIP and the positive electrode output end voltage VON of the differential operational amplifier. Wherein two input ends of the analog-to-digital converter are respectively coupled with the VOP and the VON, and the output Vout of the analog-to-digital converter is the difference between the VOP and the VON.

Owner:西安中颖电子有限公司

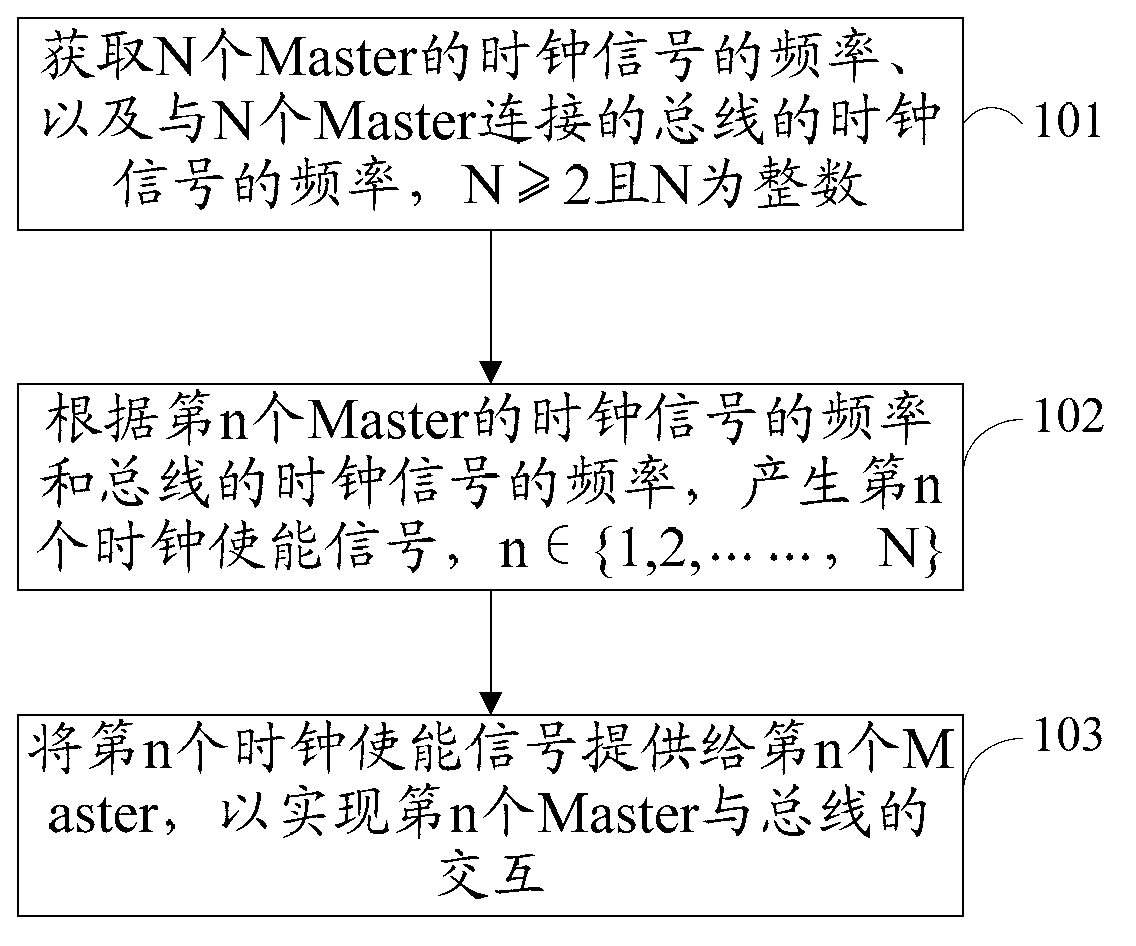

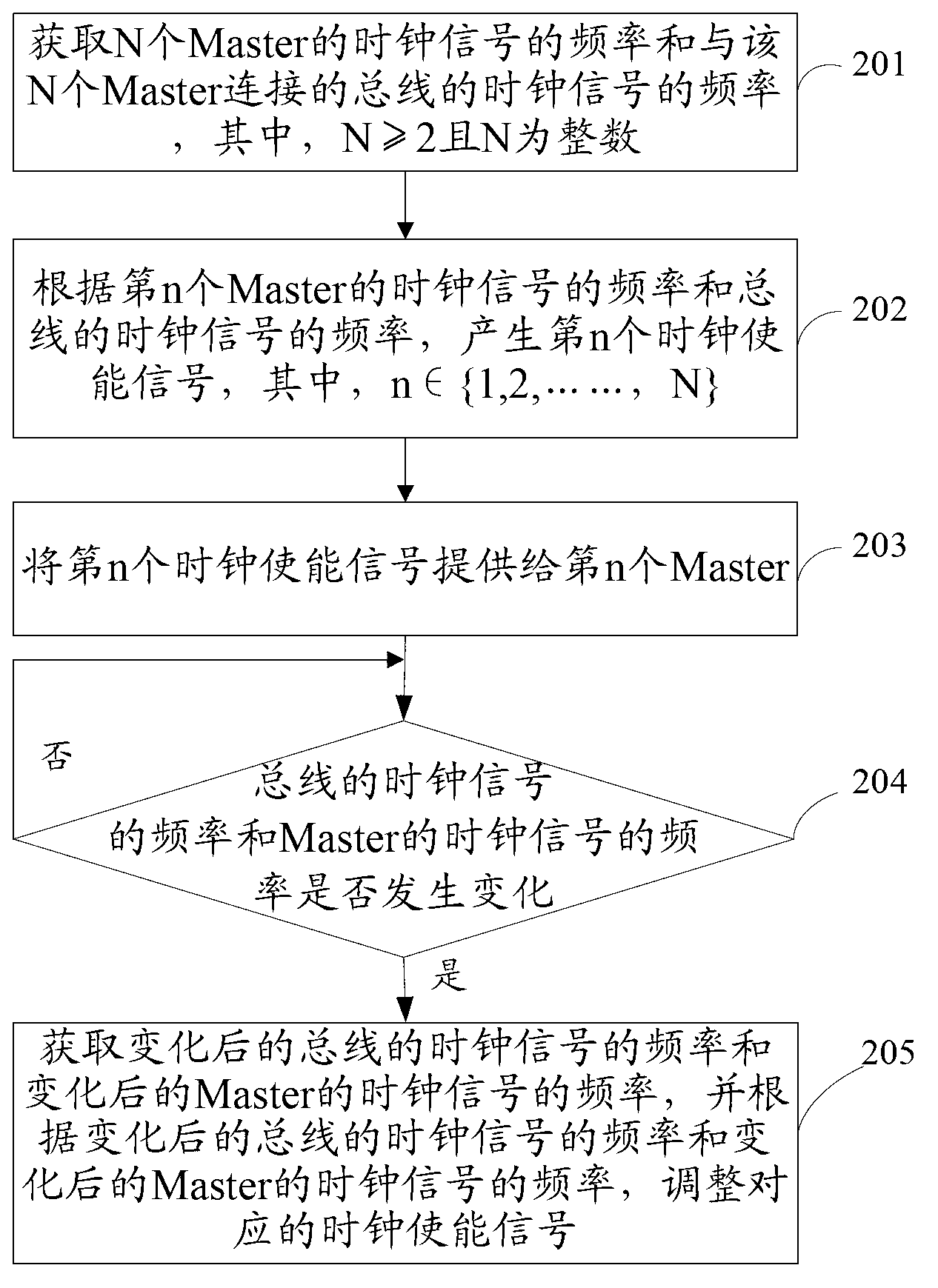

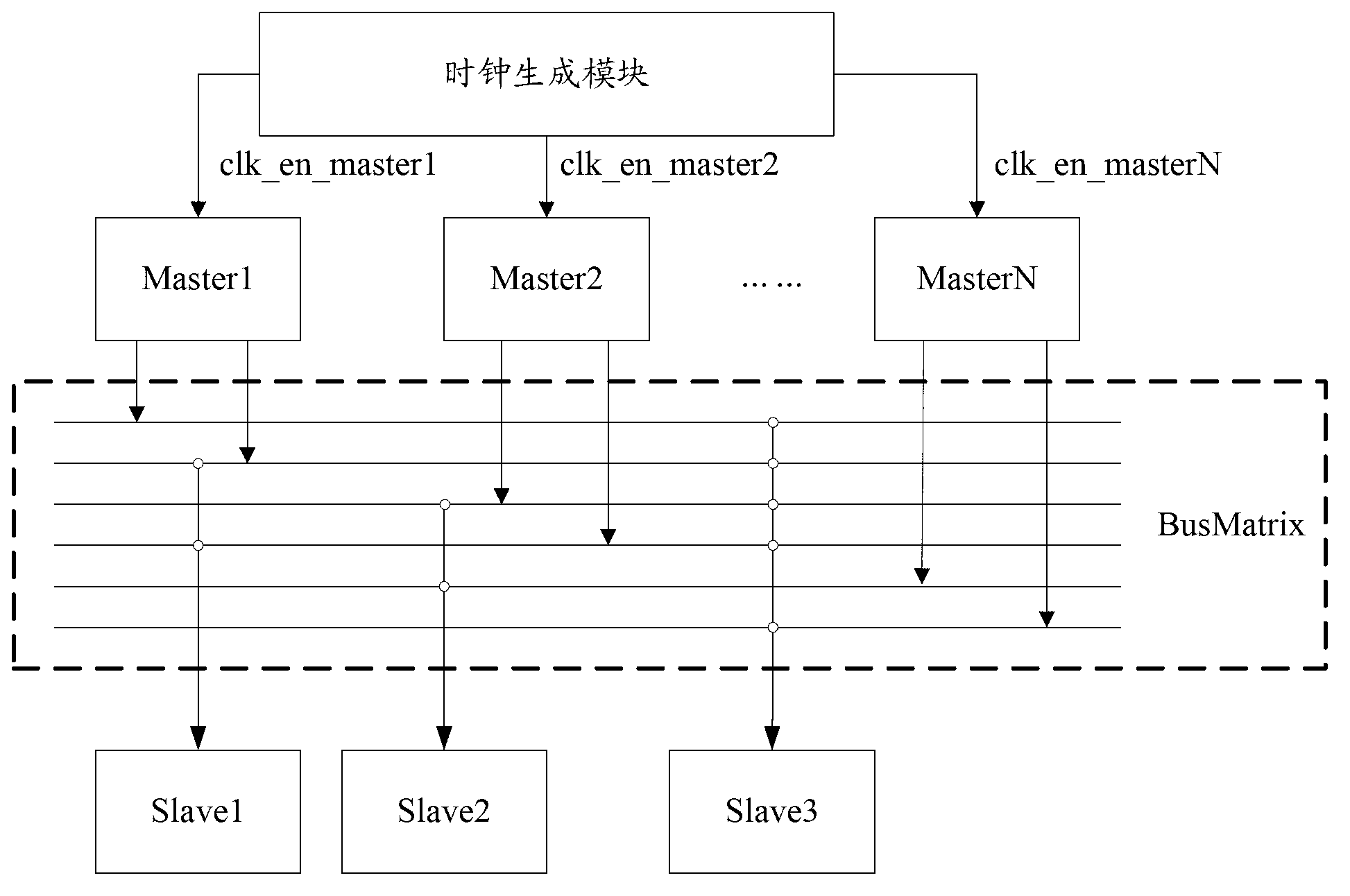

Generation method and device of CKE signal

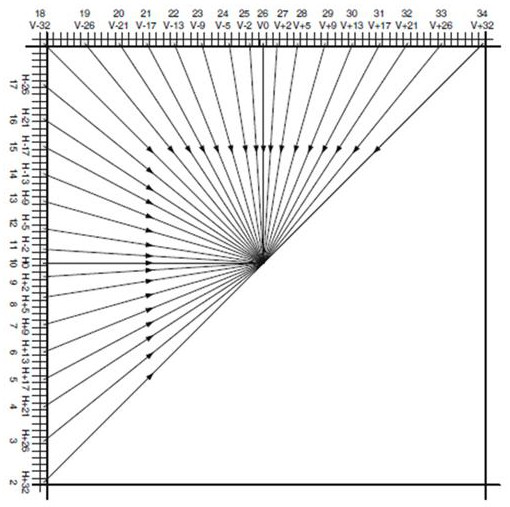

ActiveCN103064461AAvoid large quantitiesOptimizing place and routeGenerating/distributing signalsEngineeringVIT signals

The utility model discloses a generation method and a device of CKE signals and belongs to the field of communication. The generation method includes: obtaining frequencies of the clock signals of N Masters and frequencies of the clock signals of buses which are connected with the N Masters, the clock signals of the N Masters and the clock signals of the buses are generated based on the same source clock, N is not less than 2 and N is an integer, the nth CKE signal is produced according to the frequency of the nth clock signal of the Master and the frequency of the clock signal of the buses, n belongs to the range of 1, 2, ...N; The nth CKE signal is provided to the nth Master. The generation device of CKE signals comprises obtaining modules, generation modules and providing modules. Because every Master can individually provide a CKE signal, the generation method and the device of CKE signals has the advantages of greatly reducing the numbers of driving circuits of the CKE and being easy for operators to make placement and routing.

Owner:HUAWEI TECH CO LTD

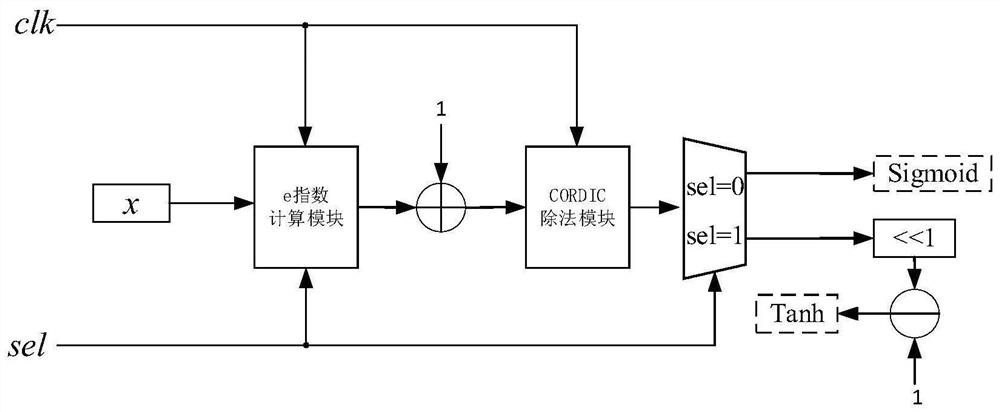

Hardware implementation device and method for activation function

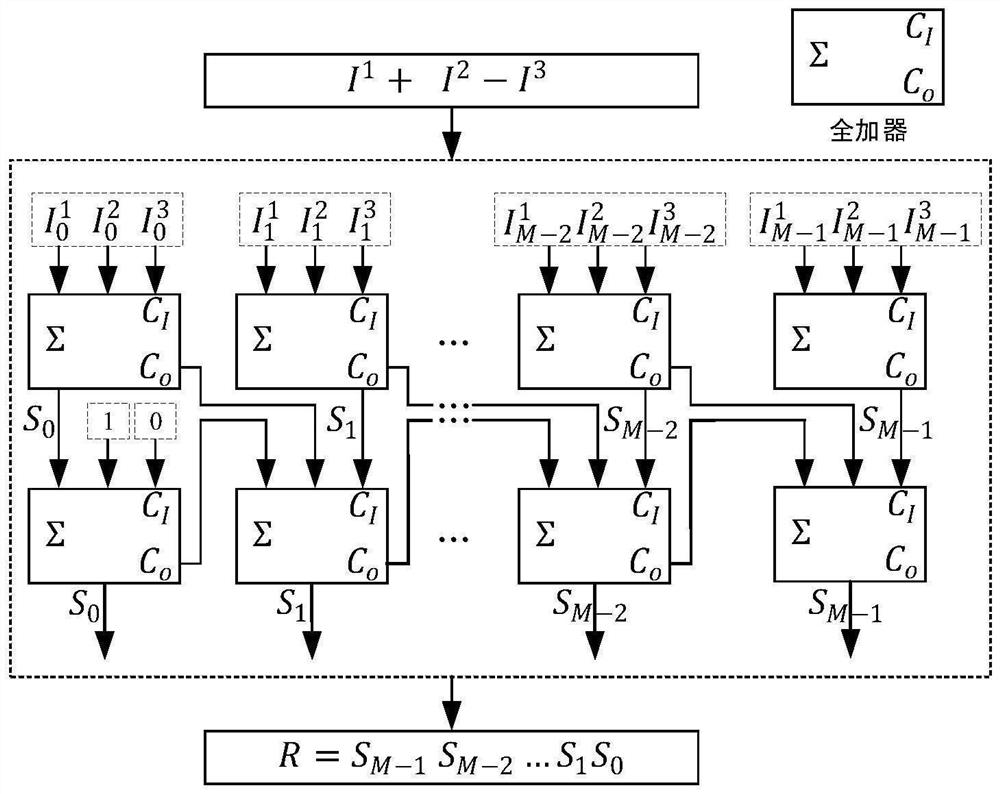

PendingCN111860792ALower latencySimple structureComputation using non-contact making devicesNeural architecturesActivation functionParallel computing

The invention discloses a hardware implementation device and method of an activation function, and belongs to the technical field of hardware implementation of function calculation. Aiming at the problem that in the prior art, high performance and hardware resources are difficult to balance when the hardware of a conventional method achieves an activation function, the device comprises an e-exponential calculation module and a CORDIC division module; an input signal calculates an e-exponential e-x or an e-exponential e2x in the e-exponential calculation module through a small index lookup table with 2 as the base and shifting and additive operation. Based on carry-save addition, an adder achieves the calculation function like I1 + I2-I3; based on a CORDIC algorithm, a CORDIC division module calculates a division function result shown in the specification through multiple times of iteration. The circuit structure is simple, no complex control logic exists, circuit layout and wiring areconvenient, the calculation precision is high, sigmoid and tanh activation function calculation in any input range is supported during calculation, and the problem that a traditional hardware implementation method cannot balance performance and hardware resources is solved.

Owner:南京宁麒智能计算芯片研究院有限公司

A noise processing method and a circuit after a noise processing process

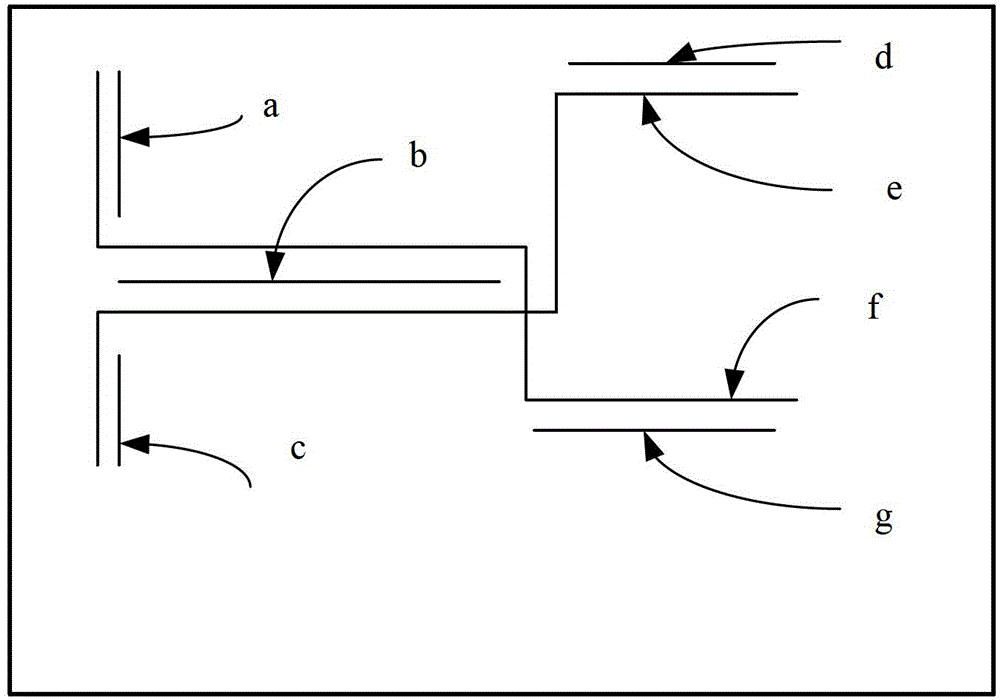

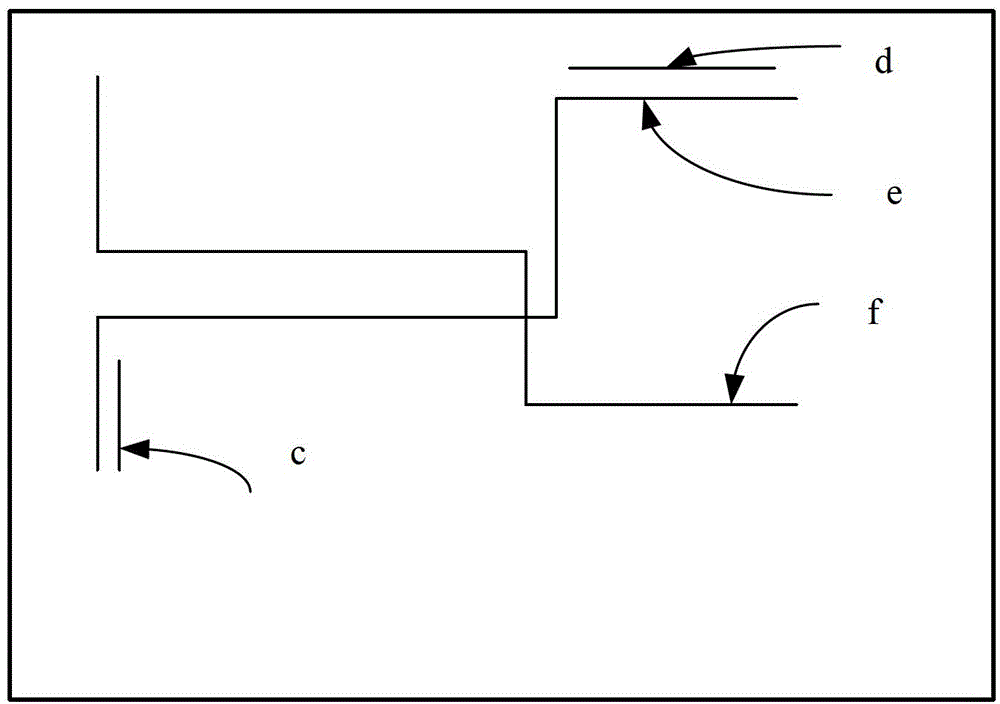

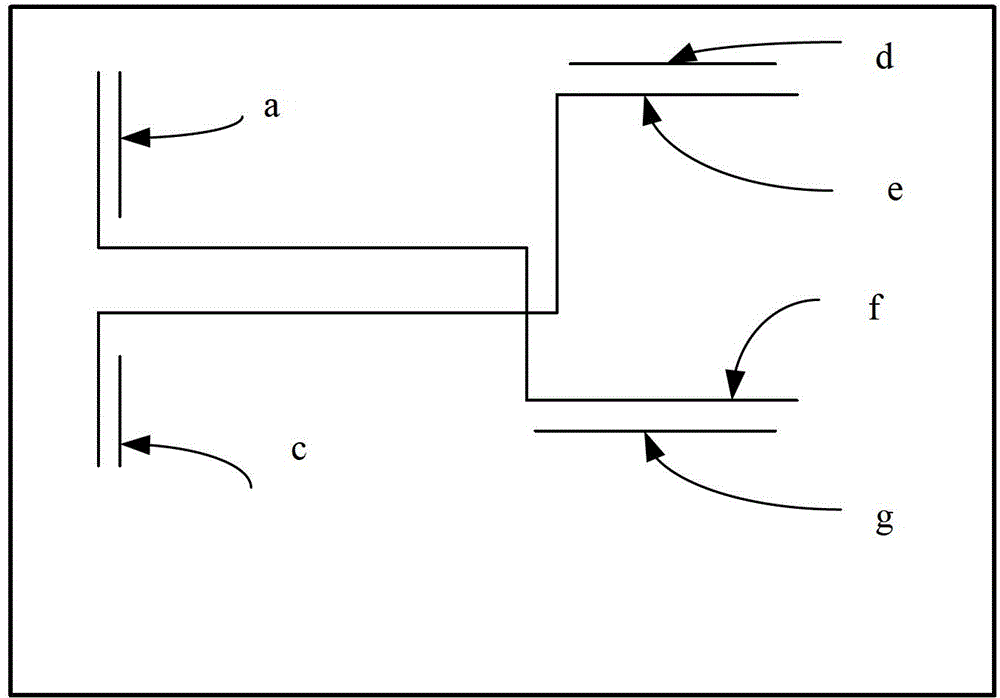

ActiveCN103338007AImprove optimization efficiencyMeet trace noise voltage threshold requirementsNoise generationComputer science

The invention provides a noise processing method and a circuit after a noise processing process. The circuit after the noise processing process comprises at least two disturbed lines and at least one disturbing line. The number of parallel lines among the at least three line does not exceed two. Parallel portions exist between the disturbed lines and the disturbing line. Common parallel portions exist between the disturbed lines. The width of a gap between the common parallel portions is wider than or equal with a sum value of two times the width of a minimum line gap and the width of the line.

Owner:华力智芯(成都)集成电路有限公司

Optimized BCH (Bose-Chaudhuri-Hocquenghem) decoder

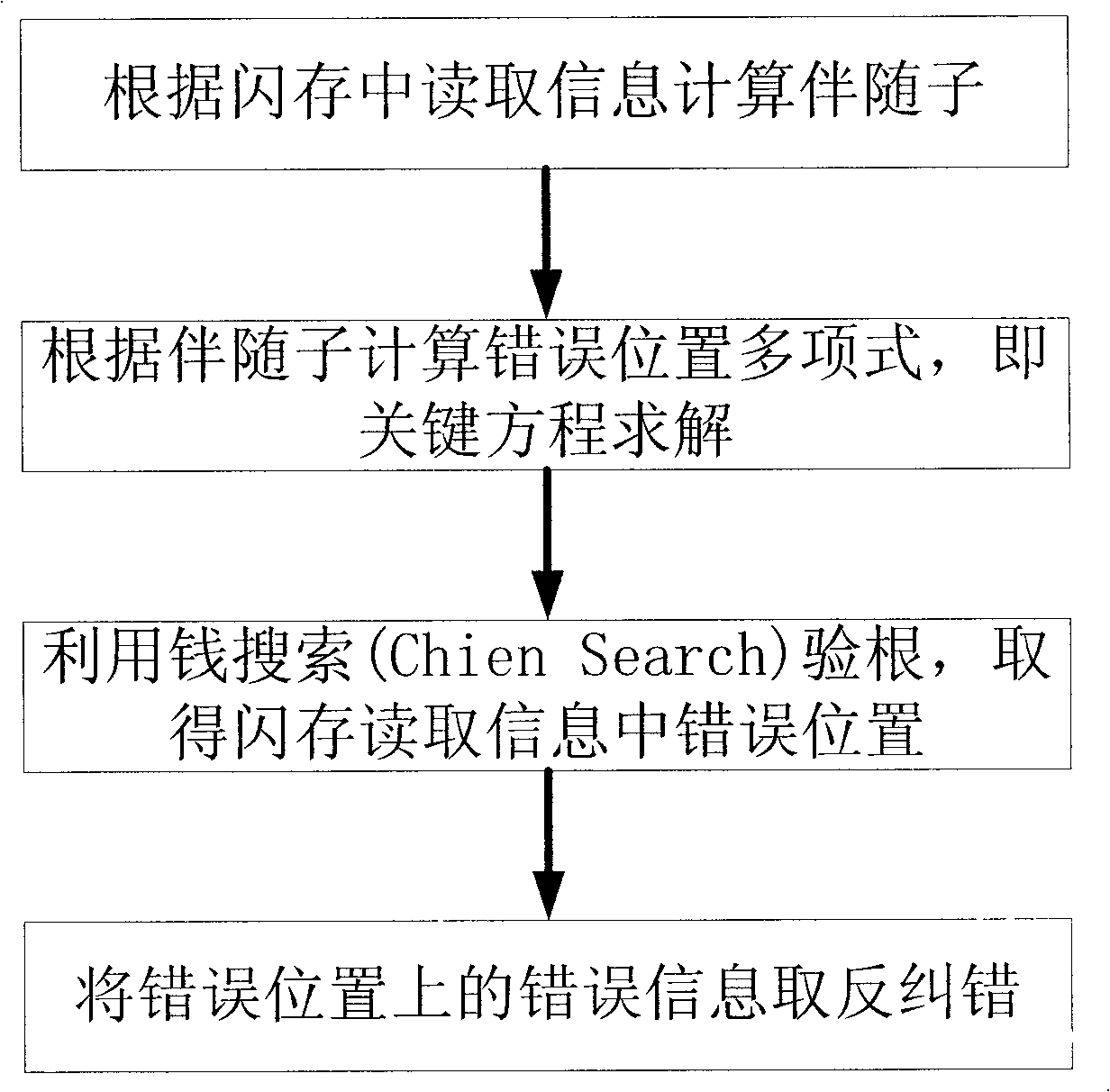

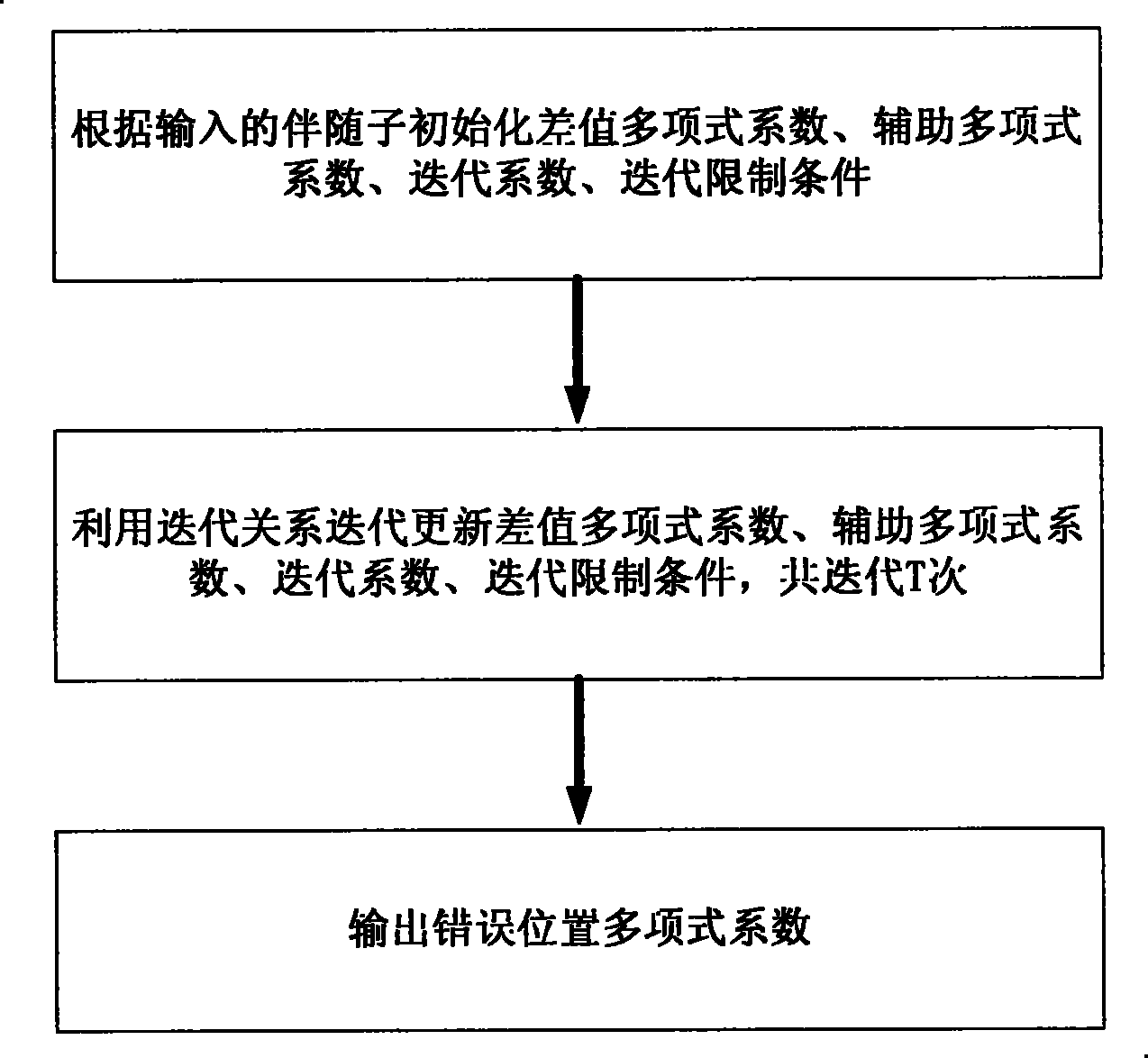

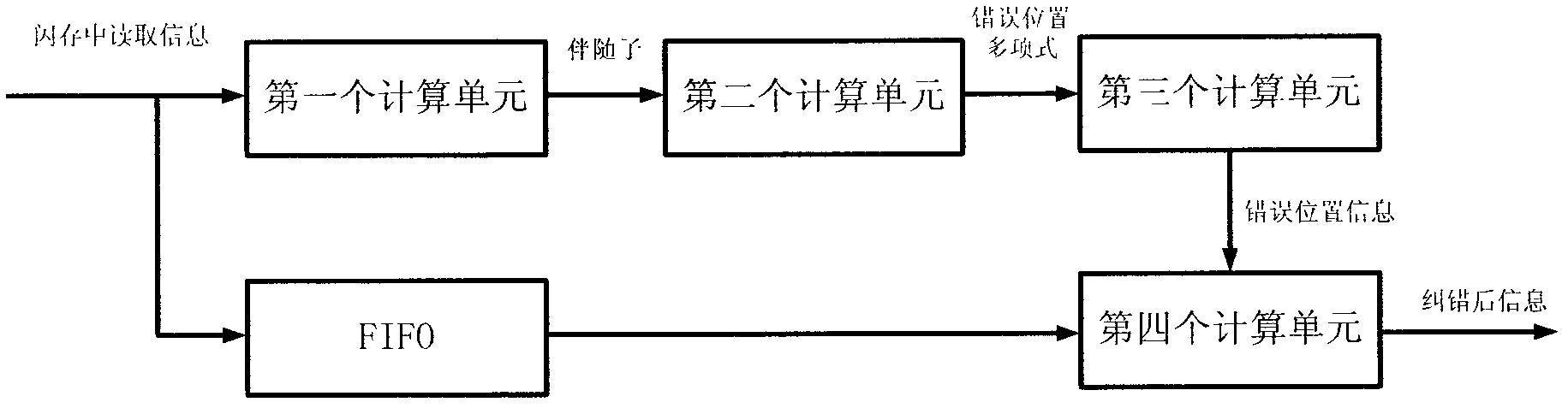

InactiveCN102568607AOptimizing place and routeSolve technical difficultiesStatic storageLogic complexityVery large scale integrated circuits

The invention provides an optimized BCH (Bose-Chaudhuri-Hocquenghem) decoding method and device in a flash controller. The optimized BCH decoding method comprises the following steps of: reading flash memory information, storing the flash memory information in an FIFO (First Input First Output), and computing an adjoint functor according to the read information; solving a key equation, namely computing an error location polynomial based on an iterative algorithm according to the adjoint functor; verifying a root through Chien Search according to the error location polynomial to determine an error location; and performing anti-error correction on error information of the error location so as to obtain error correction information in a flash memory. In the step of solving the key equation, the conventional riBM algorithm by using characteristics of a binary BCH code is optimized, so that logic is almost reduced to half; and iterative delay is only 1 / 2 of original algorithm, so that the technical difficulty in ECC (Error Correction Code) logic complexity in a flash memory controller is overcome. According to the optimized BCH decoding method and device, due to high-level symmetry and structuralization of circuits, balancing on logic complexity and decoding delay by adopting a laminated means is facilitated on one hand, wiring layout at the rear end of a VLSI (Very Large Scale Integrated Circuit) is facilitated on the other hand. The optimized riBM algorithm can also be applied to digital television broadcasting, space communication and other application fields.

Owner:殷民

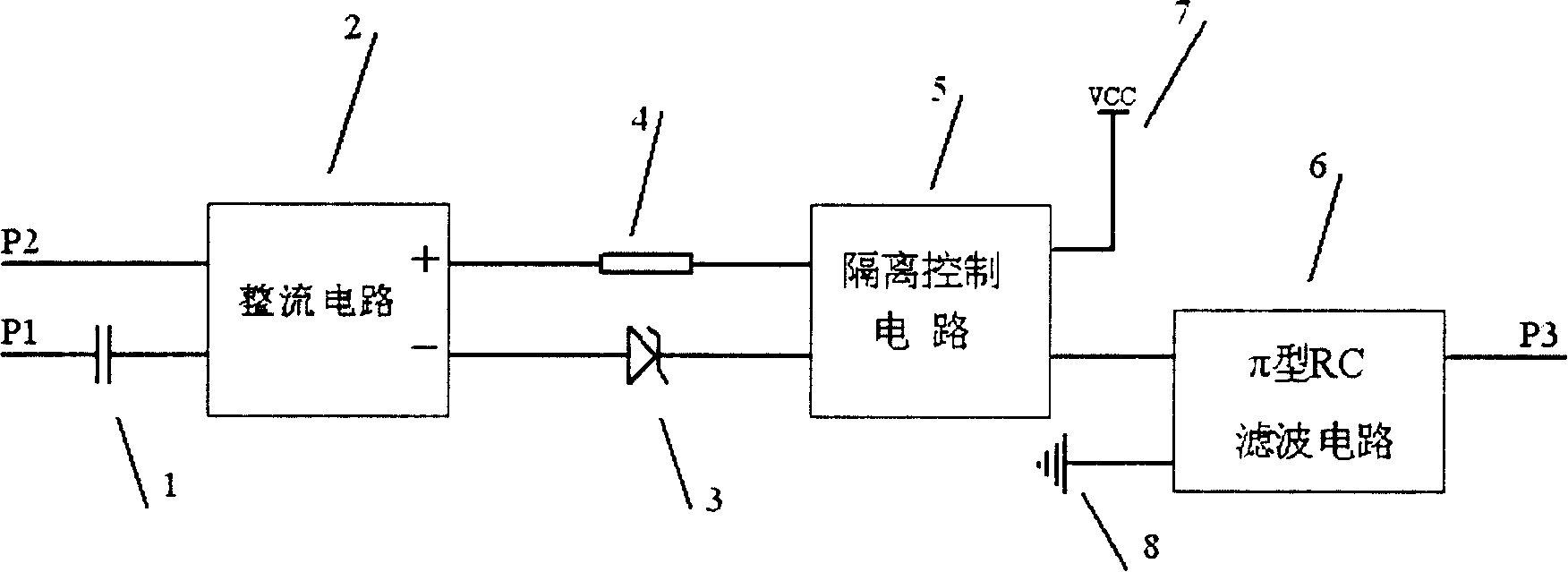

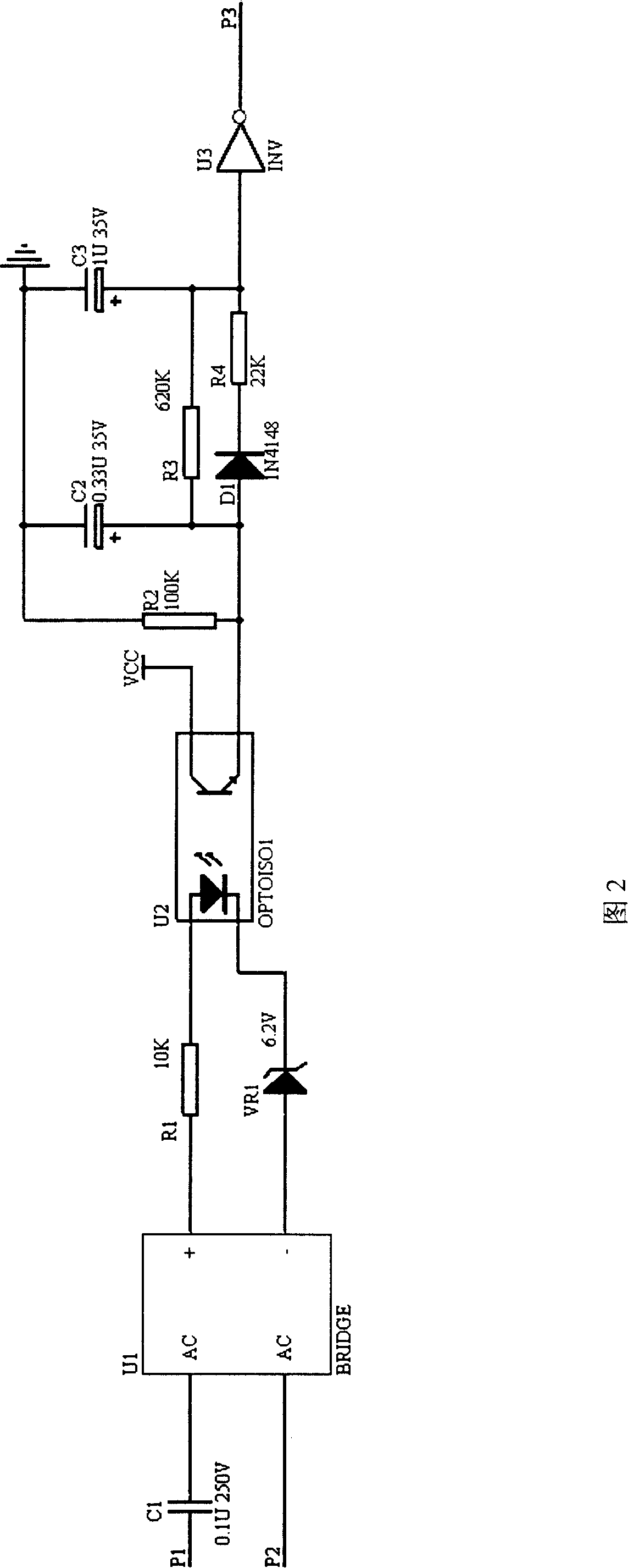

A plug access ringtone detection device

InactiveCN101166207ARealize the function of ringing detection (that is, the user picks up and hangs up the phone)Realize the ringing detection functionCurrent supply arrangementsSupervisory/monitoring/testing arrangementsDigital inputMagnet

Plug in and pull out type connection ringing detection device includes the input end and output end, and a plug-in board. The input end, output end, and detection circuit are fixed on the plug-in board. The plug-in board possesses input and output jacks in use for plugging in user circuit of switchboard magnet or circuit in telephone set. First input end, second input end, digital input end in high level, input end of ground wire, and output end of signal are installed on the jacks. Features are: good filtering effect, high sensitivity, convenient to maintain and replace, simple operation, and shortcut.

Owner:CENT FOR SPACE SCI & APPLIED RES

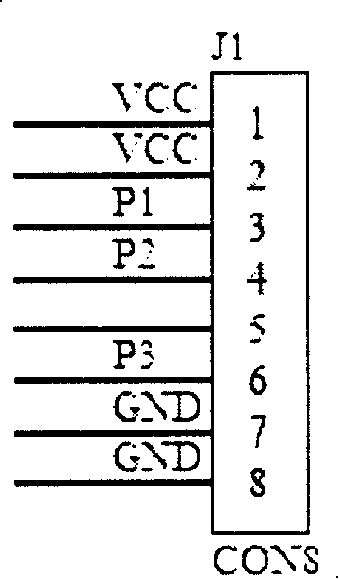

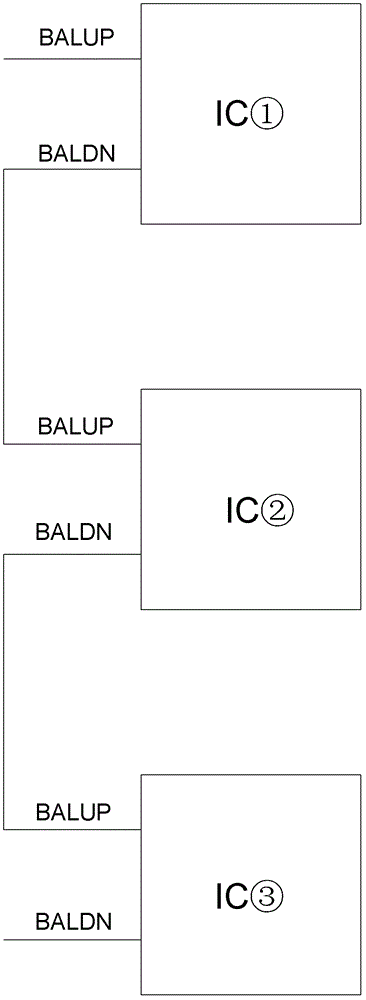

Battery protective chip cascade balance control device and battery protective chip

ActiveCN103187743BEasy to packReduce packaging costsCharge equalisation circuitCells structural combinationEngineeringBattery pack

A battery protection chip may comprise: a first end, configured to output a strong pull up signal when a voltage of at least one battery in a battery pack protected does not reach a balance threshold, and to output a weak pull down signal when voltages of all batteries in the battery pack protected reach the balance threshold; and a second end, configured to output a strong pull down signal when a voltage of at least one battery in a battery pack protected does not reach a balance threshold, and to output a weak pull up signal when voltages of all batteries in the battery pack protected reach the balance threshold.

Owner:BYD SEMICON CO LTD

Weak correlation multiport parallel store controller

InactiveCN102622192BIncrease flexibilityReduce in quantityInput/output to record carriersComputer architectureControl store

The invention provides a weak correlation multiport parallel store controller, which is connected with a access memory unit in peripheral equipment and a storage stack including a plurality of storage body and can achieve multiport parallel storage between the visiting and storage unit in the peripheral equipment and the storage stack in the peripheral equipment. The weak correlation multiport parallel store controller comprises a storage port module, an arbitration module, an address generation module and a port switching module. The weak correlation multiport parallel store controller has the following advantages of (1) supporting block reading and writing in random lengths and being high in dexterity; (2) enabling transmission of address and data to multiplex in the same group of signal wires to complete, greatly reducing quantity of the transmission signal wires in a system, being favorable for application of distribution and wiring and reducing complexity and cost of the system; and (3) being simple in structure, less in used transmission signal wires and capable of supporting design and achievement of a large-scale multiport storage, and improving efficiency of parallel access memory of a plurality of processors.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Centralized cache device and design method based on field programmable gate array

ActiveCN104252560BReduce occupancyIncrease the number ofSpecial data processing applicationsComputer architectureProcessor register

The invention relates to a centralized-cache device and design method based on field-programmable gate arrays and relates to the field of field-programmable gate array design, and the centralized-cache device and design method is adaptive to at least two same functional modules. The device comprises a time division multiplexing control unit, a signal serialization unit, a centralizing storage register, a combinational logic unit and a signal parallelization unit. The time division multiplexing control unit is used for dividing the period into two time slots with the same length of time, each time slot corresponds to one functional module sequentially, and each functional module performs input signal processing in the corresponded time slot. The signal serialization unit is used for converting the parallel input signals of each functional module into serial input signals. The centralizing storage register is used for storing the register of each functional module and reading and writing the register of the functional module in the time slot corresponding to the functional module. The combinational logic unit is used for combinational logic of input signal processing of single functional module. The signal parallelization unit is used for restoring serial output signals as parallel output signals after the input signals of each functional module are processed.

Owner:FENGHUO COMM SCI & TECH CO LTD

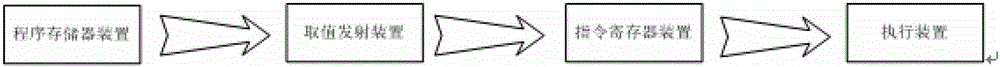

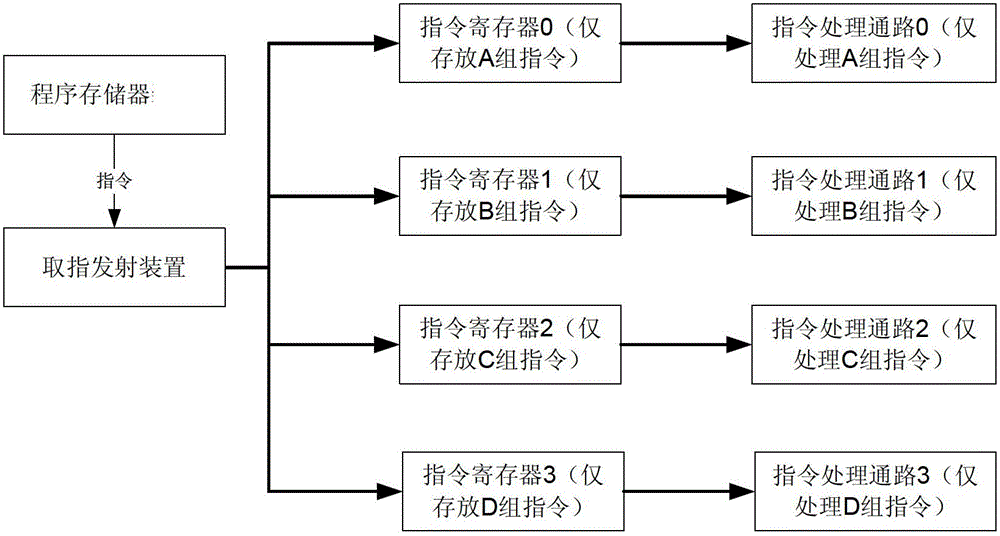

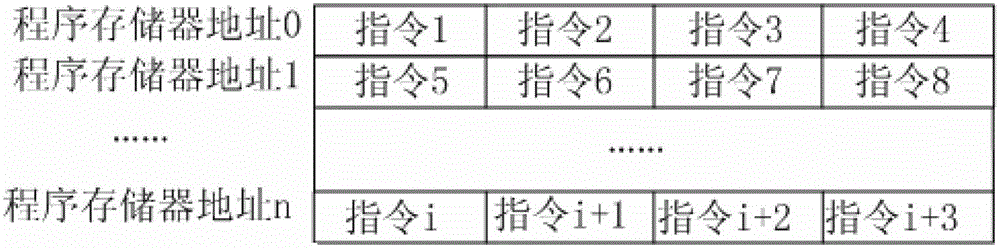

Processor and processing method for VLIW (very low instruction word)

ActiveCN102855120BThe command execution process is complicatedLong logic operation timeMachine execution arrangementsHardware structureProcessor register

The invention discloses a processor and a processing method for a VLIW (very long instruction word) and mainly aims to provide a processor for a VLIW, which is simple in instruction-fetching and short in operation cycle, and a processing method for the VLIW. The processor for the VLIW includes: instruction selection modules which group and judge instructions entering different instrument processing channel hardware structures are set before instruction registers, and logic circuits before execution devices are reduced; the processing method includes: judging group information of the instructions before entering the instruction registers, storing the instructions into the corresponding instruction registers, and executing the instructions in each instruction register respectively; and accordingly operation cycle of the instructions is shortened. The parallel instructions are stored in the different instruction registers, and accordingly complexity in post instruction execution process is simplified, and frequency of the processor is increased.

Owner:北京中科晶上科技股份有限公司

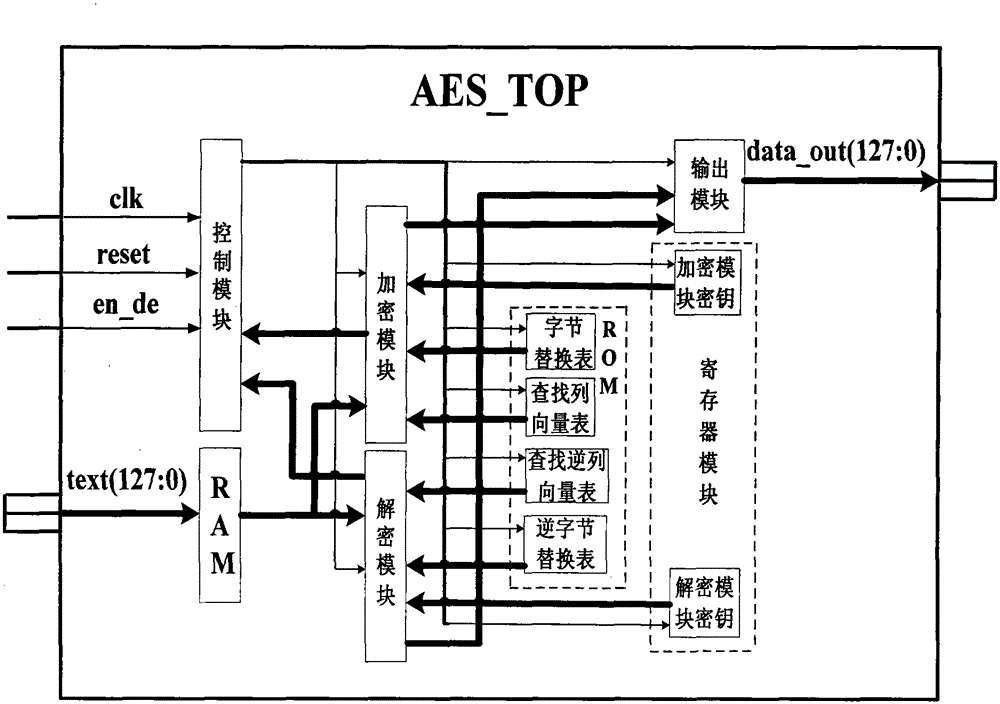

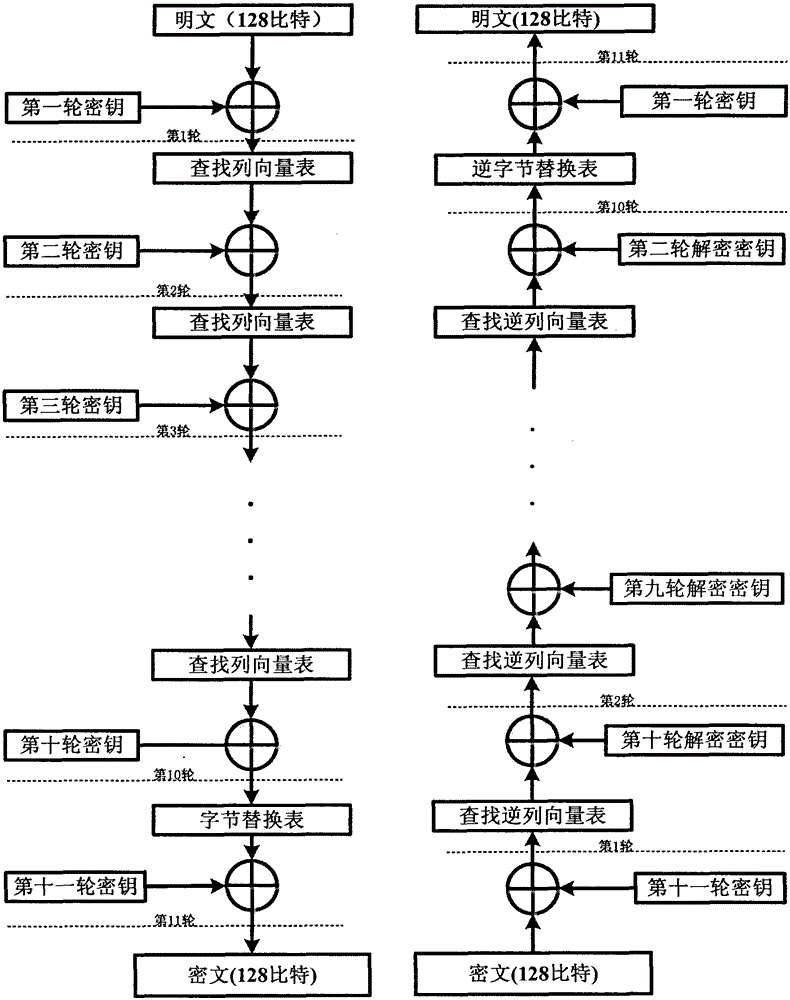

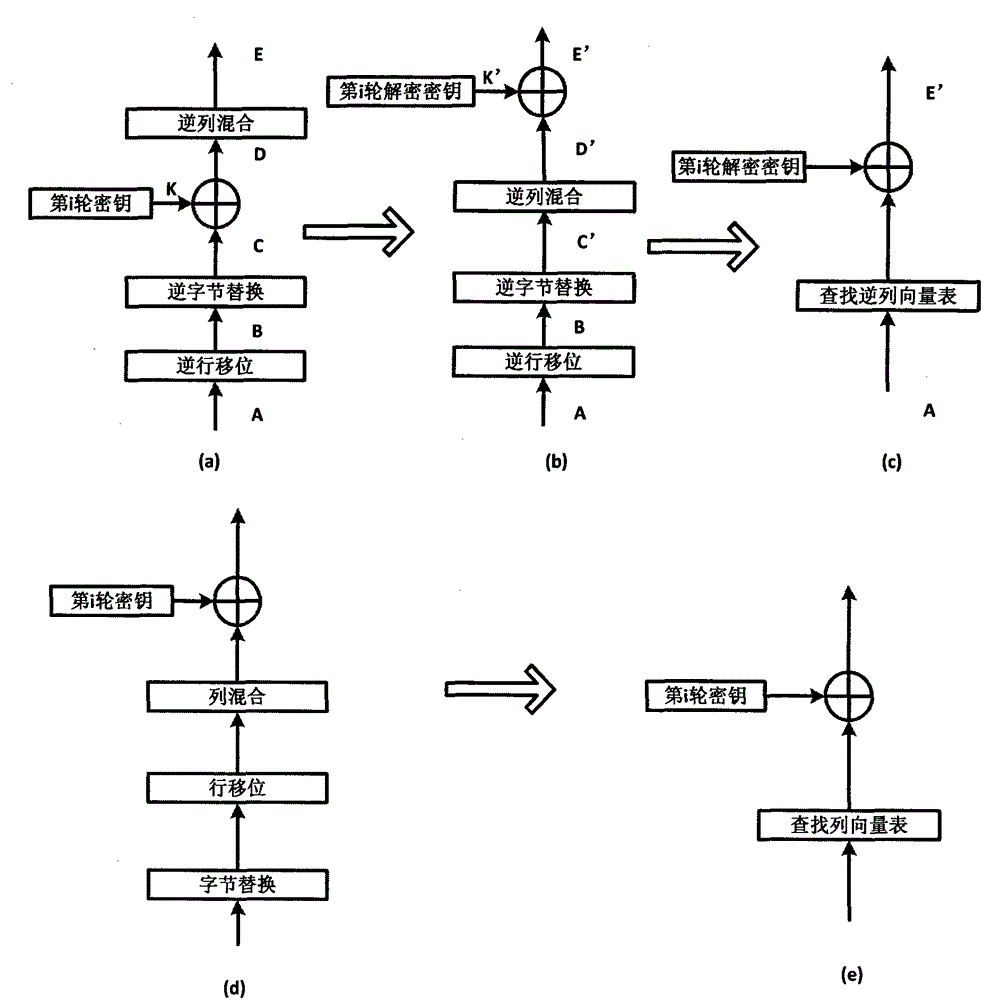

Ultra-high-speed aes processor based on fpga and its realization method

InactiveCN103152165BImprove portabilitySimple storage control logicEncryption apparatus with shift registers/memoriesComputer architectureStructure of Management Information

The invention discloses a field programmable gate array (FPGA)-based superfast auxiliary encoder system (AES) processor and an implementing method thereof. The AES processor comprises an interface storage area buffer module, a control module, an AES encryption and decryption module, a read-only memory lookup table module, a register module and an output module. The implementing method for the processor comprises the following steps: 1, initializing a data table; 2, performing initial setting; 3, receiving data; 4, reading the data; 5, selecting a data processing mode; 6, judging whether the encryption and decryption are finished; and 7, outputting a result. The invention mainly solves the problems that an AES processor is controlled complicatedly and modules have low portability, reliability, safety and processing speed in the prior art; and an improved algorithm and a lookup table-based method are used. The AES processor has all levels of structures which are fixed, is simple in control logic, comprises the modules with high portability, is suitable to be implemented in a singlechip FPGA, and has the characteristics of high speed and high accuracy.

Owner:XIDIAN UNIV

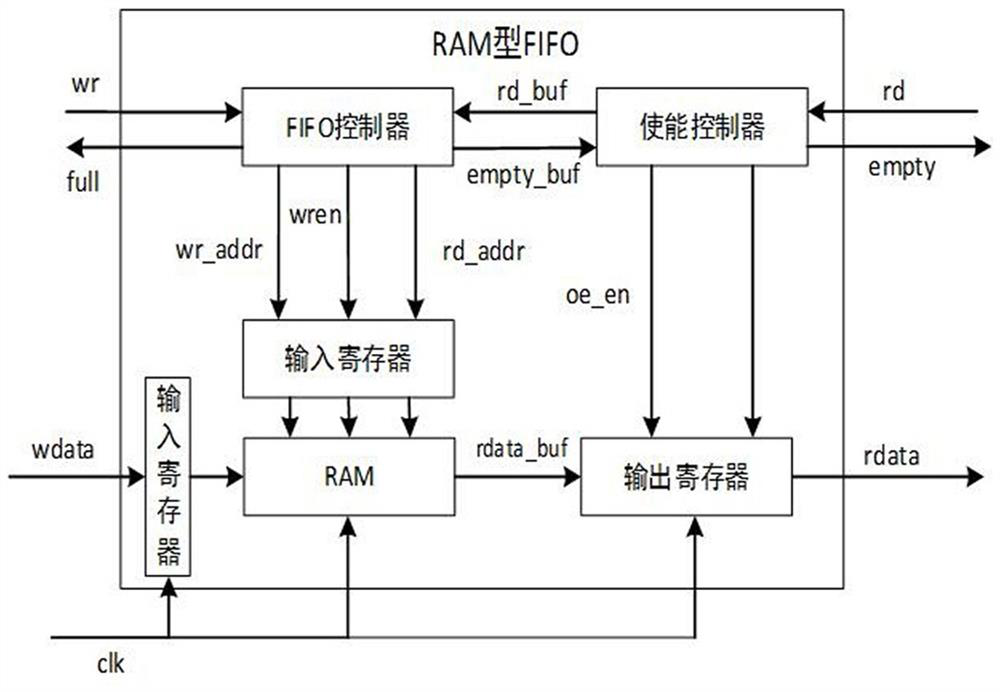

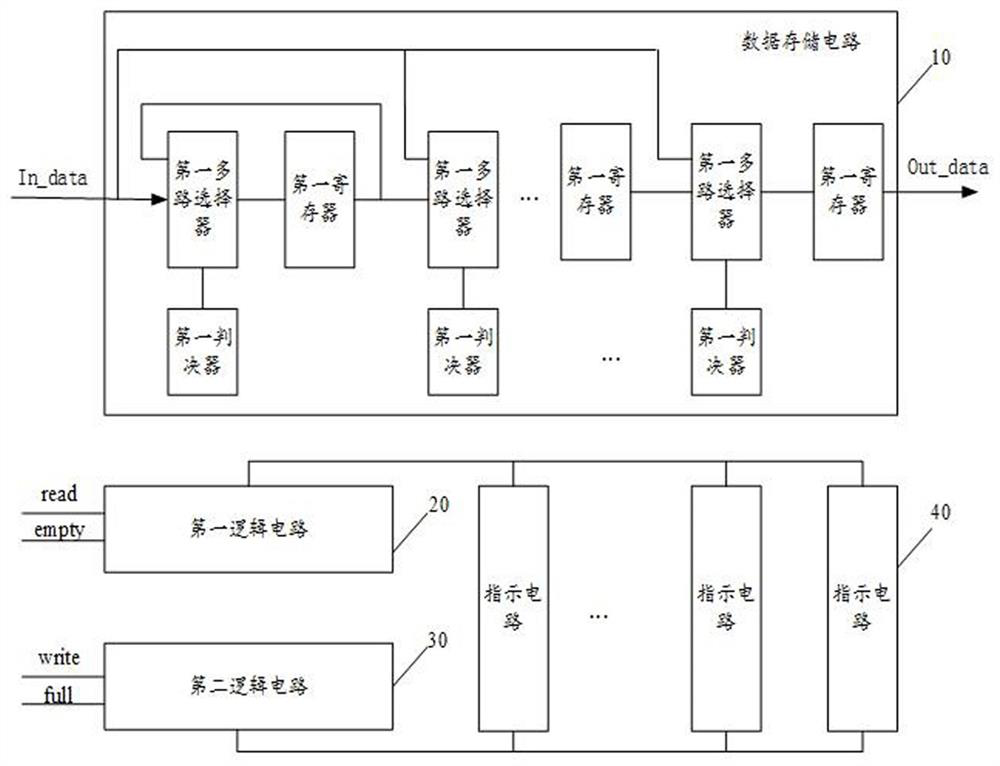

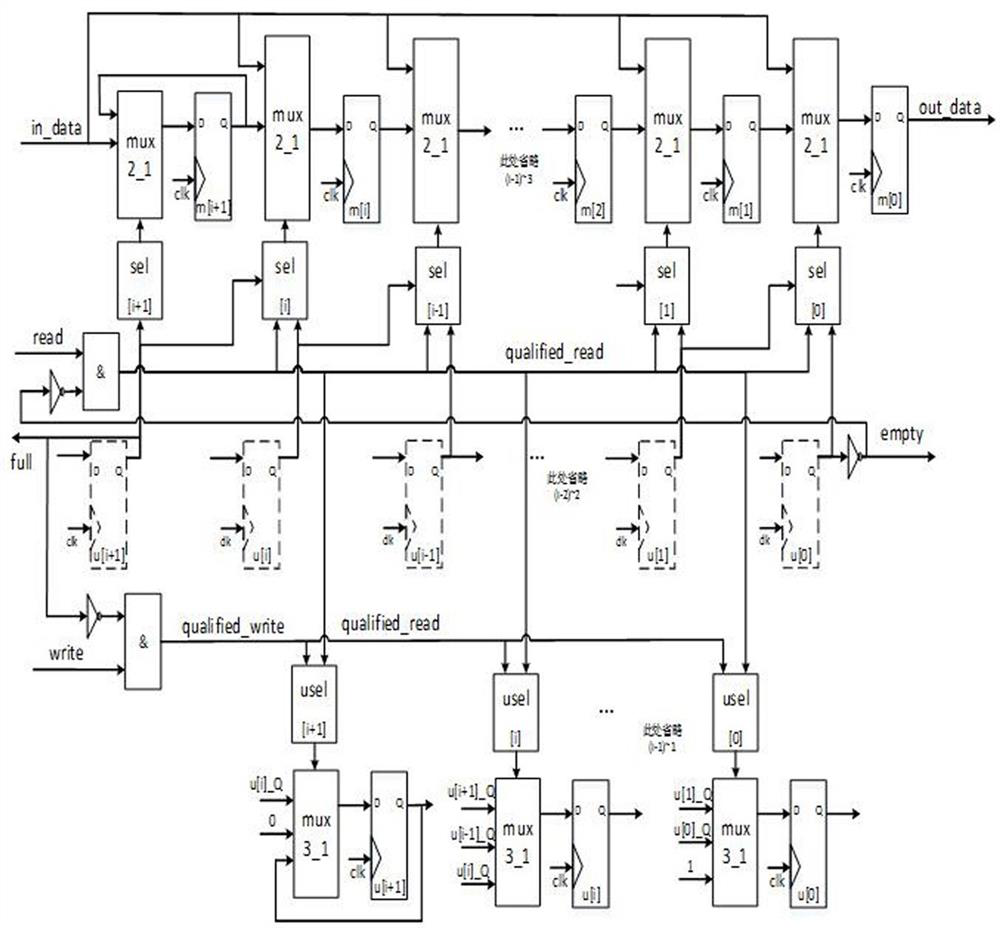

a synchronous fifo

Owner:SUZHOU METABRAIN INTELLIGENT TECH CO LTD

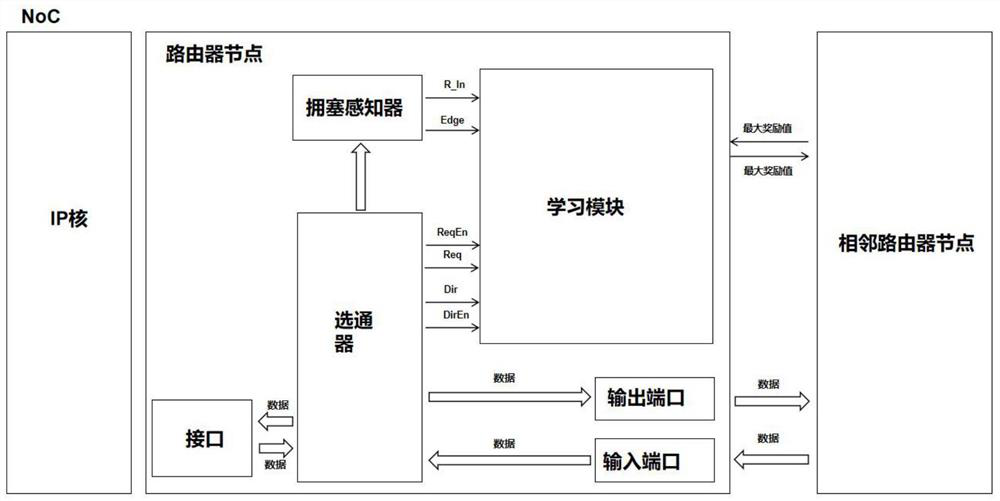

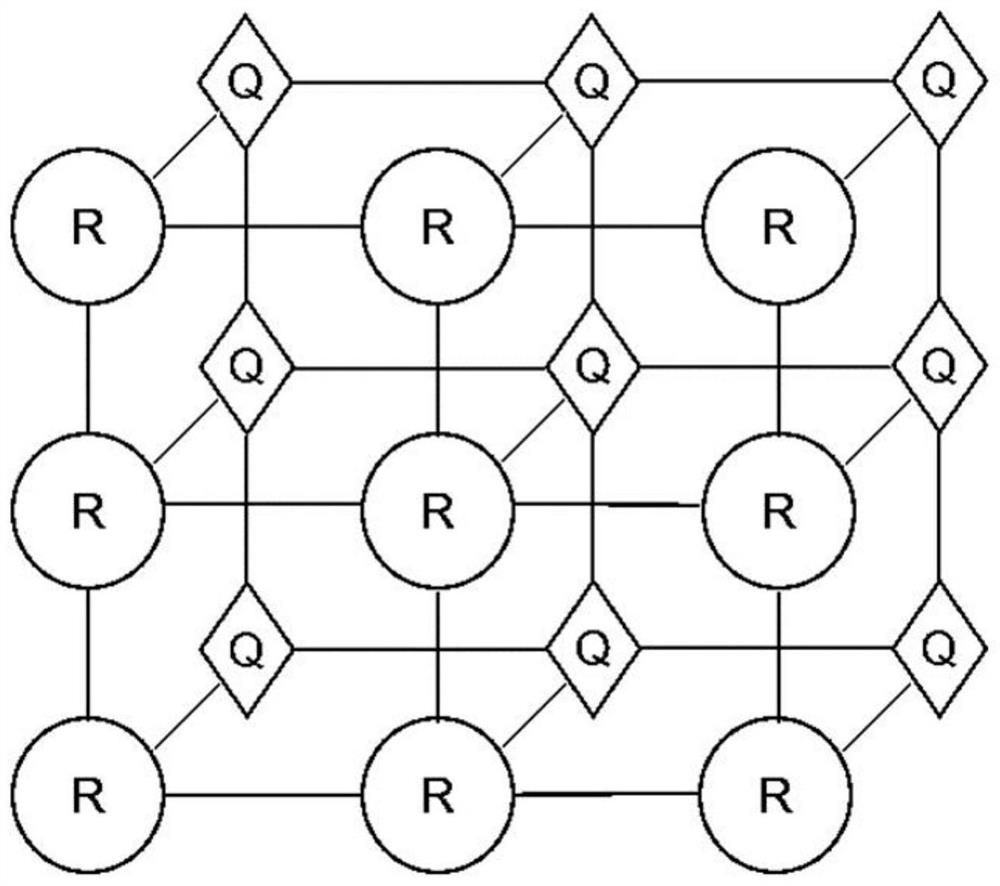

A Routing Method Based on Hierarchical q-routing Planning

The invention discloses a routing method based on hierarchical Q-routing planning, which is to obtain high-efficiency data transmission links through global layered parallel planning by sensing network congestion and interconnection link usage. The algorithm of the present invention is a routing algorithm based on a lookup table. The routing algorithm stores the planned direction in the routing table in the learning module of each router node, and the data packet is obtained by accessing the routing table in the learning module of the router node. path information. The present invention constructs a hierarchical design on the basis of split Q-routing, utilizes multi-layer congestion sensor and multi-layer parallel learning to greatly reduce the convergence time of the algorithm, thereby improving the data transmission efficiency of the on-chip network, and also compressing the routing table , reducing hardware resource consumption.

Owner:HEFEI UNIV OF TECH

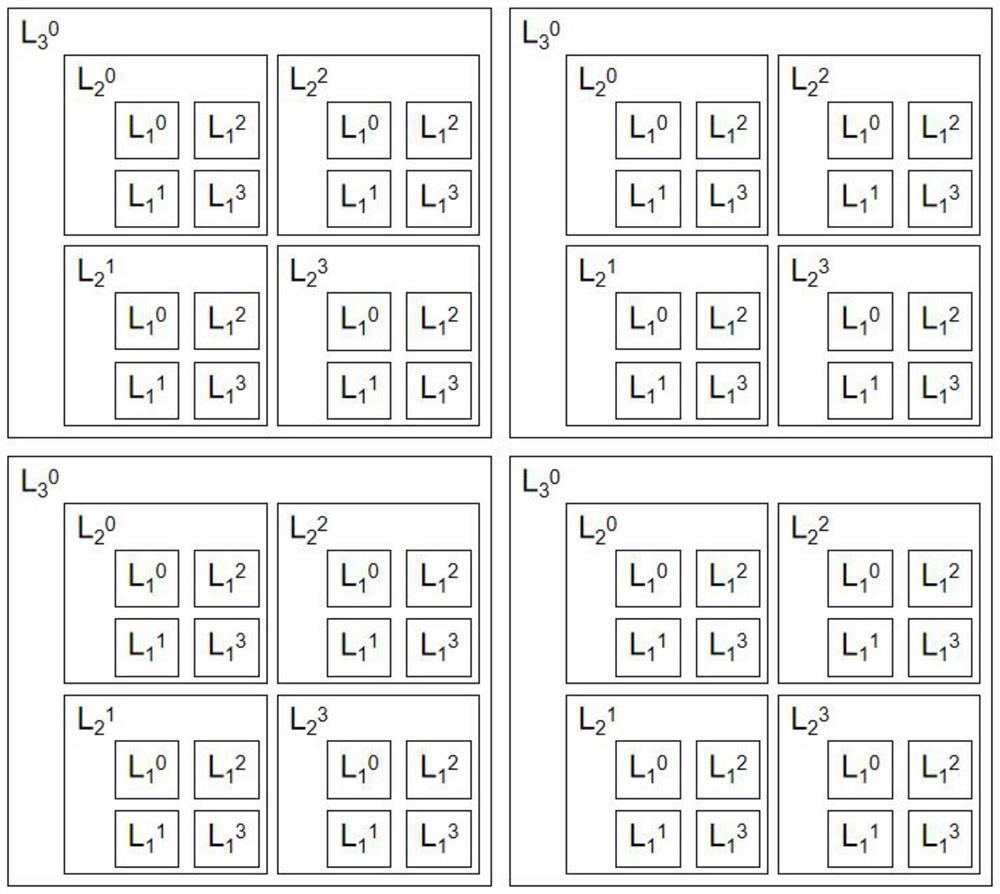

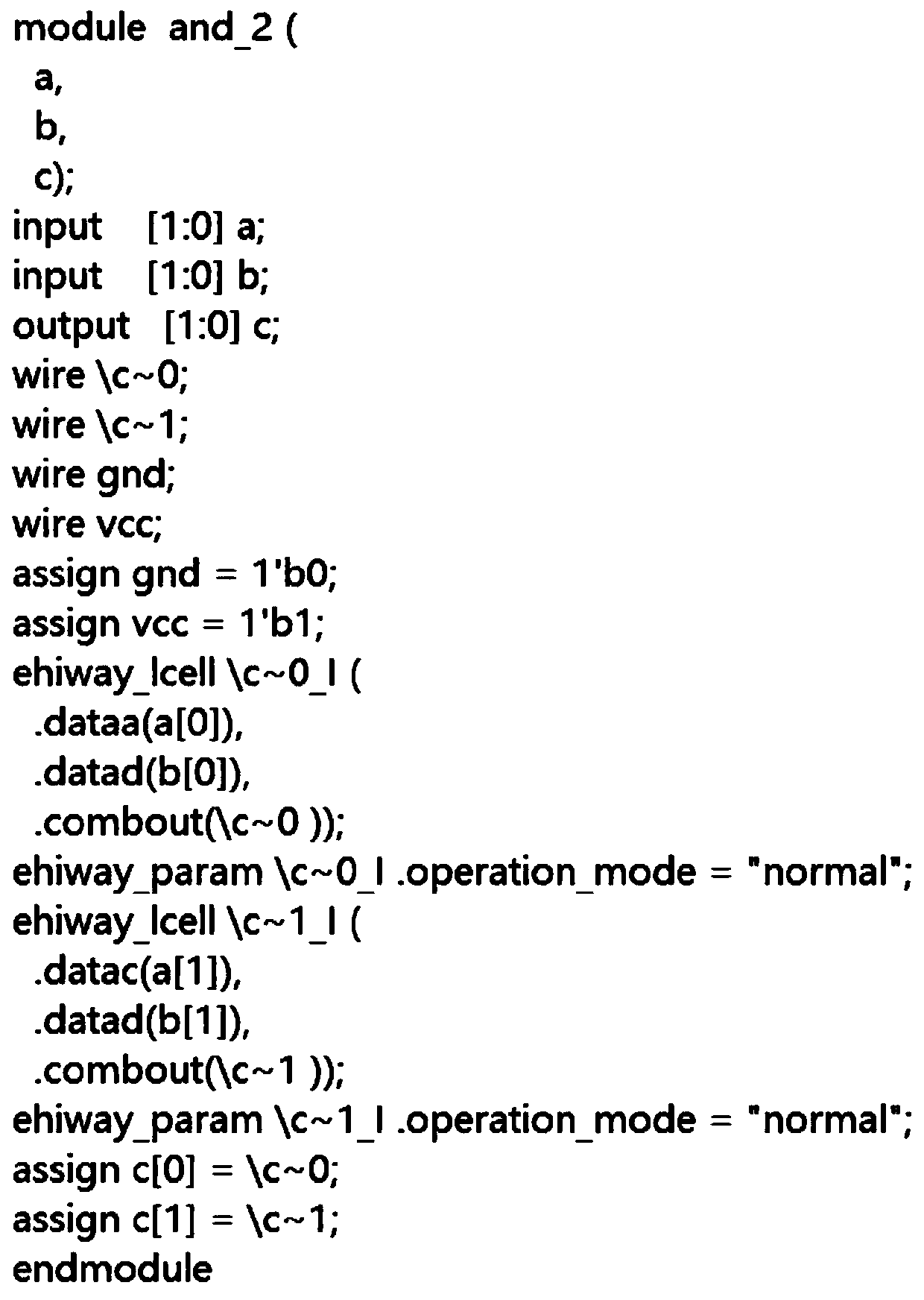

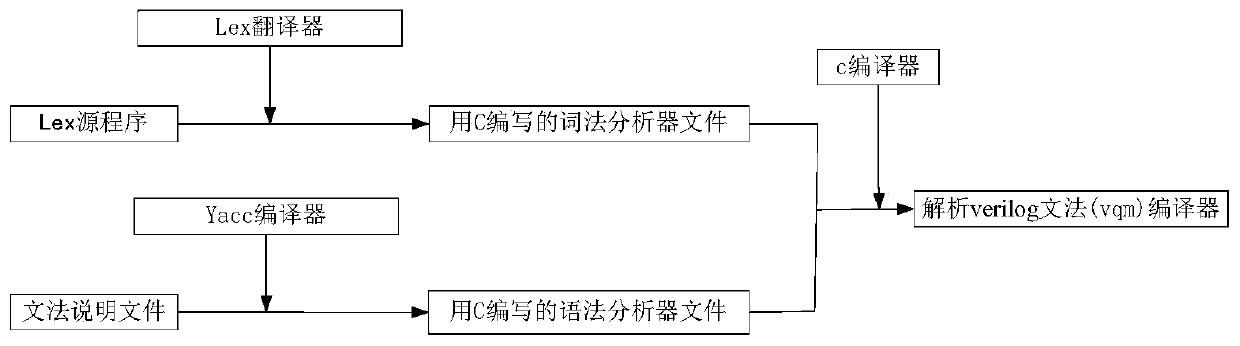

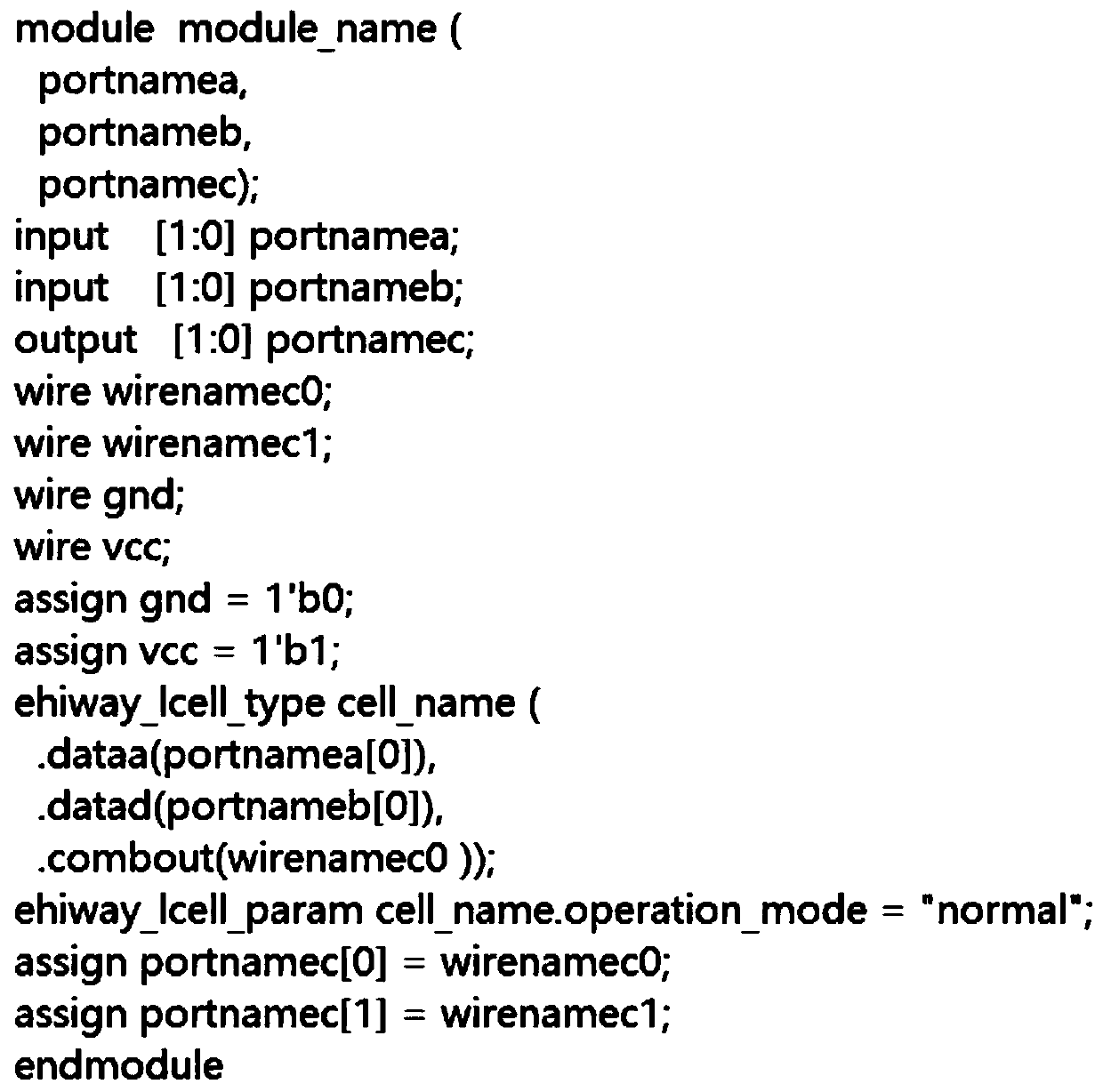

System and method for generating and analyzing verilog circuit netlist compiler

PendingCN111400984AEasy to writePromote generationComputer aided designSpecial data processing applicationsGeneration processLexical analysis

The invention discloses a system and a method for generating and analyzing a verilog circuit netlist compiler, which can greatly reduce the workload of compiling the compiler, can optimize the analysis process in a targeted manner, improves the analysis efficiency, is simple in generation process, small in workload, clear in logic structure and high in expandability, and facilitates the development of subsequent layout and wiring and the like. The system comprises a Lex translator, a Yacc compiler and a C compiler. The Lex translator is configured to analyze the Lex source program into a lexical analyzer file compiled by C; the Yacc compiler is configured to analyze the grammar description file into a syntactic analyzer file compiled by C; and the C compiler is configured to generate an analytic verilog grammar compiler from the lexical analyzer file compiled by the C and the syntactic analyzer file compiled by the C.

Owner:EHIWAY MICROELECTRONIC SCI & TECH SUZHOU CO LTD

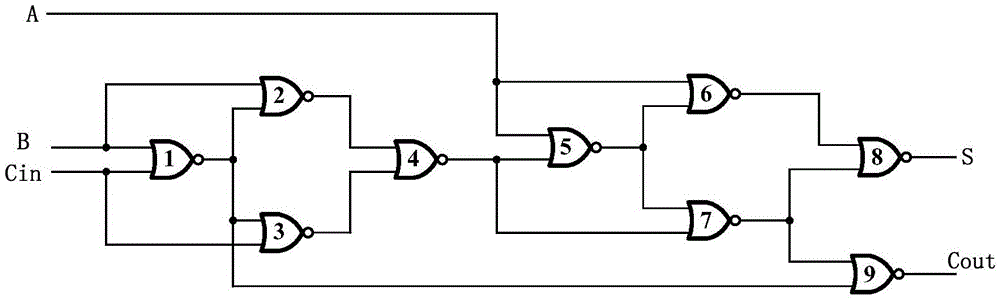

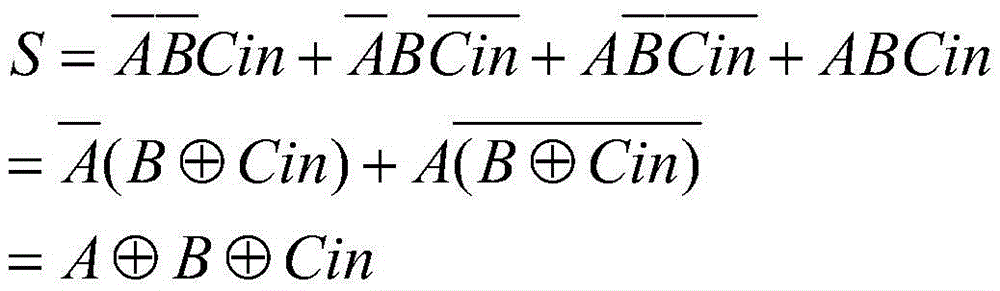

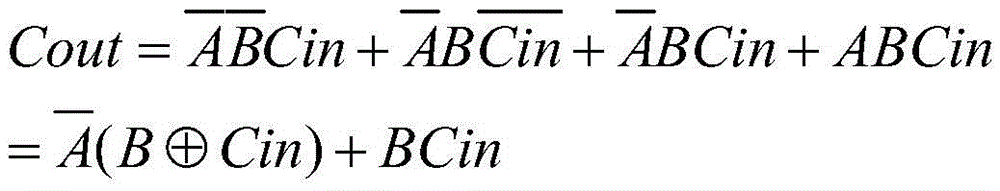

A One-bit Full Subtractor Circuit

InactiveCN103699353BStructural symmetryAvoid indirect operationsComputation using non-contact making devicesNegationNOR gate

The invention discloses a one-bit full subtracter circuit, which is suitable for subtraction and division operation. The circuit structurally comprises nine NOR gates. Inputs comprise a minuend A, a subtrahend B and a borrow bit Cin from a lower bit; outputs comprise a difference bit S and a borrow bit Cout to a high bit. A process from the input to the difference bit output or the borrow bit output passes through six stages of NOR gates, the circuit structure is symmetrical and the locating and the wiring are facilitated. The one-bit full subtracter circuit can be directly used for subtraction, the borrow bit output of the highest bit directly expresses a sign bit and the indirect operation process of subtraction completed by using an adding circuit after negation and plus one of subtrahend is avoided.

Owner:XI AN JIAOTONG UNIV