Centralized cache device and design method based on field programmable gate array

A design method and gate array technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as increasing design costs, consuming FPGA hardware resources, and the design maximum frequency does not meet the requirements, so as to achieve less resource occupation and improve System clock frequency, effect of saving design cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

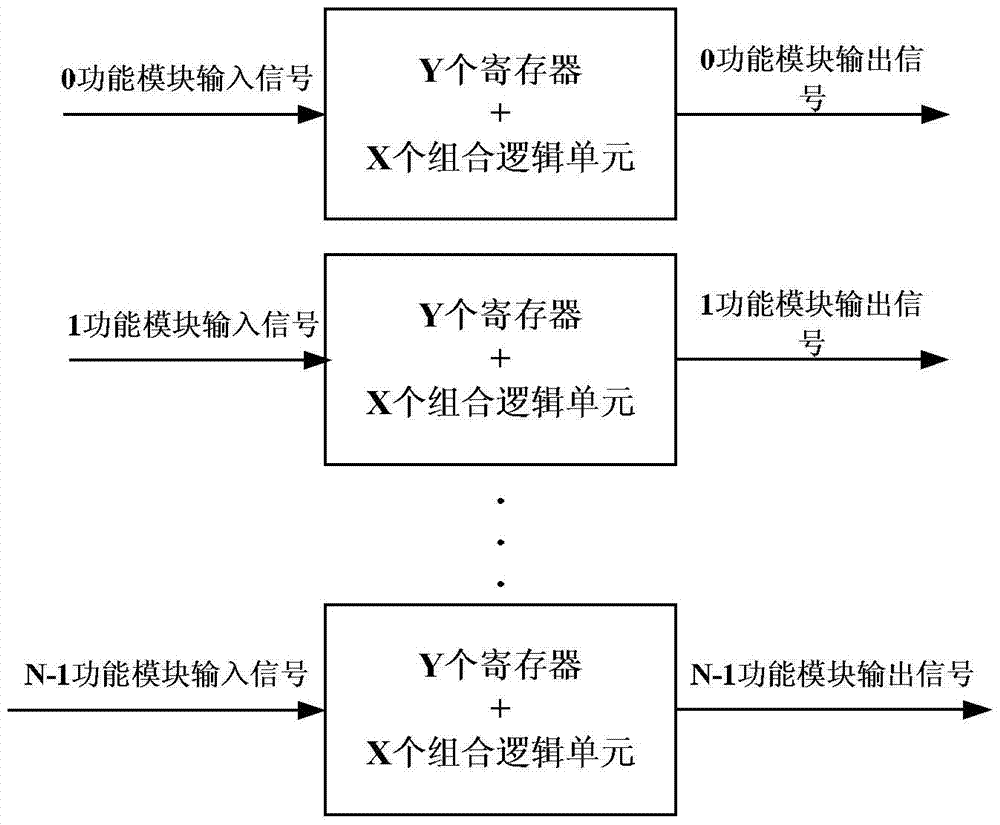

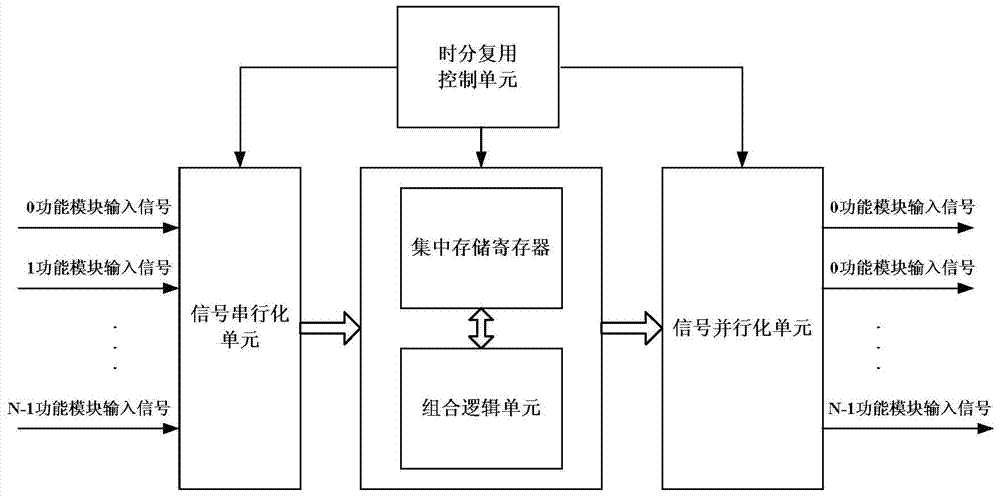

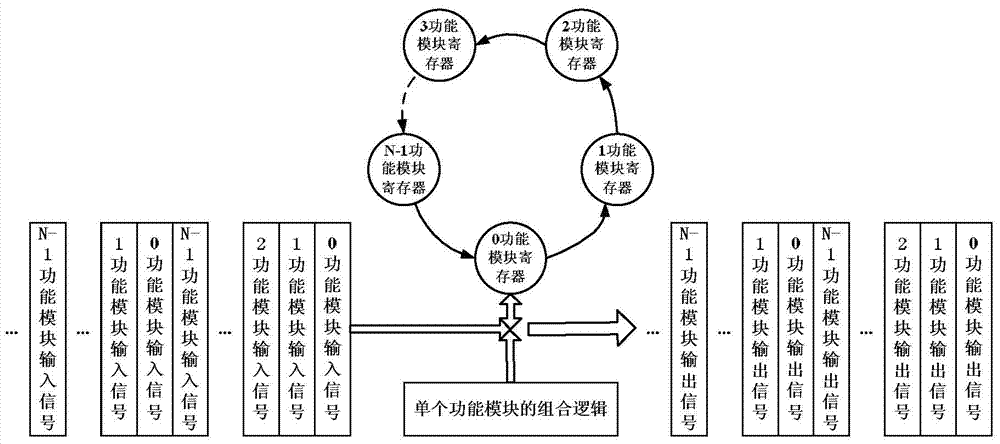

[0024] see figure 2 As shown, a centralized caching device based on a field programmable gate array is suitable for at least two identical functional modules, including a time division multiplexing control unit, a signal serialization unit, a centralized storage register, a combinational logic unit, and a signal parallelization unit. The time division multiplexing control unit is used to divide the time cycle into at least 2 time slots of equal duration, each time slot corresponds to a functional module in sequence, and each functional module performs input signal in the corresponding time slot Processing: the time slots divided by the time-division multiplexing control unit circulate continuously in sequence. The signal serialization unit is used to convert the parallel input signal of each functional module into a serial input signal; the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More