A Routing Method Based on Hierarchical q-routing Planning

A layered and routing technology, applied in transmission systems, electrical components, etc., can solve problems such as difficulty in meeting demands, loss of timeliness, and increased power consumption, and achieve the effects of reducing area resource consumption, facilitating layout and wiring, and reducing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

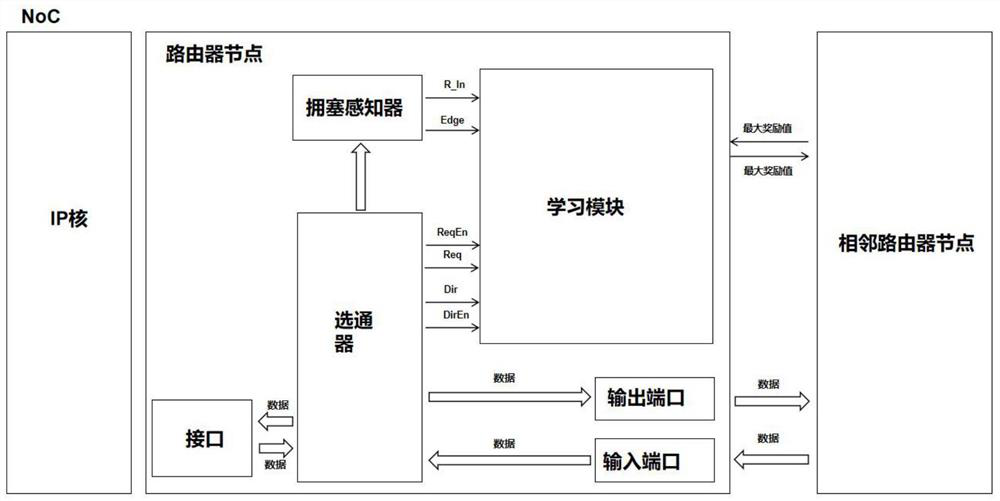

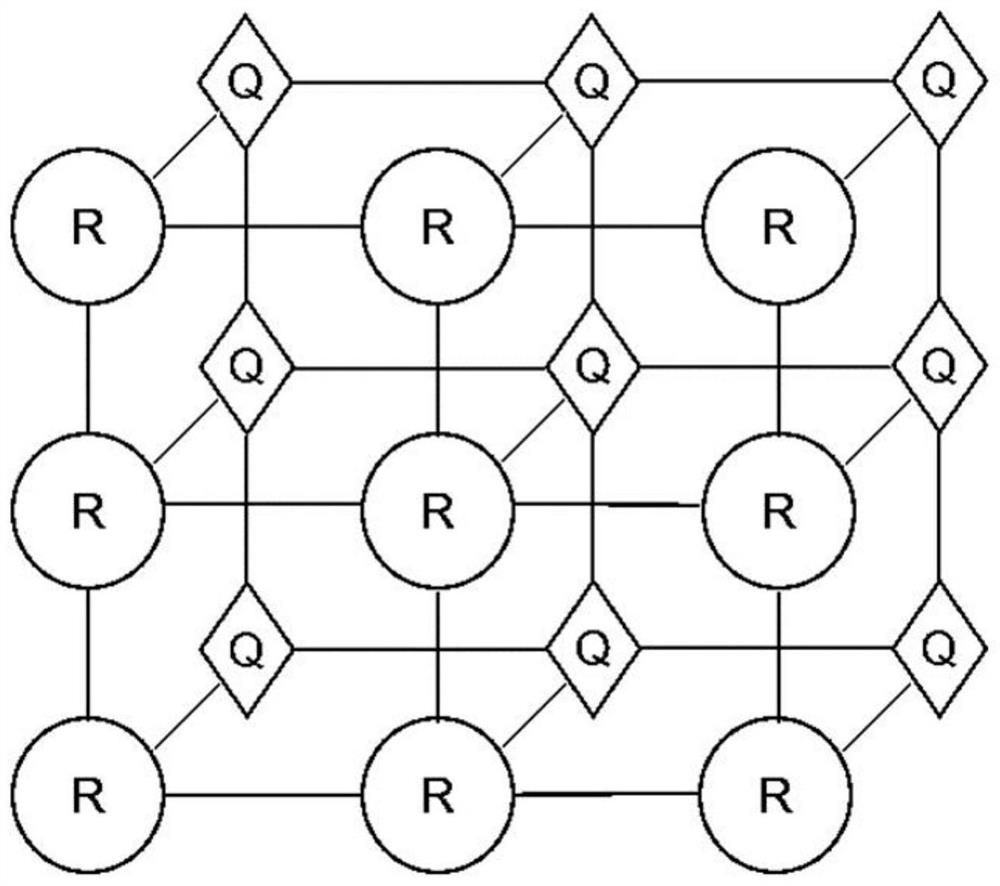

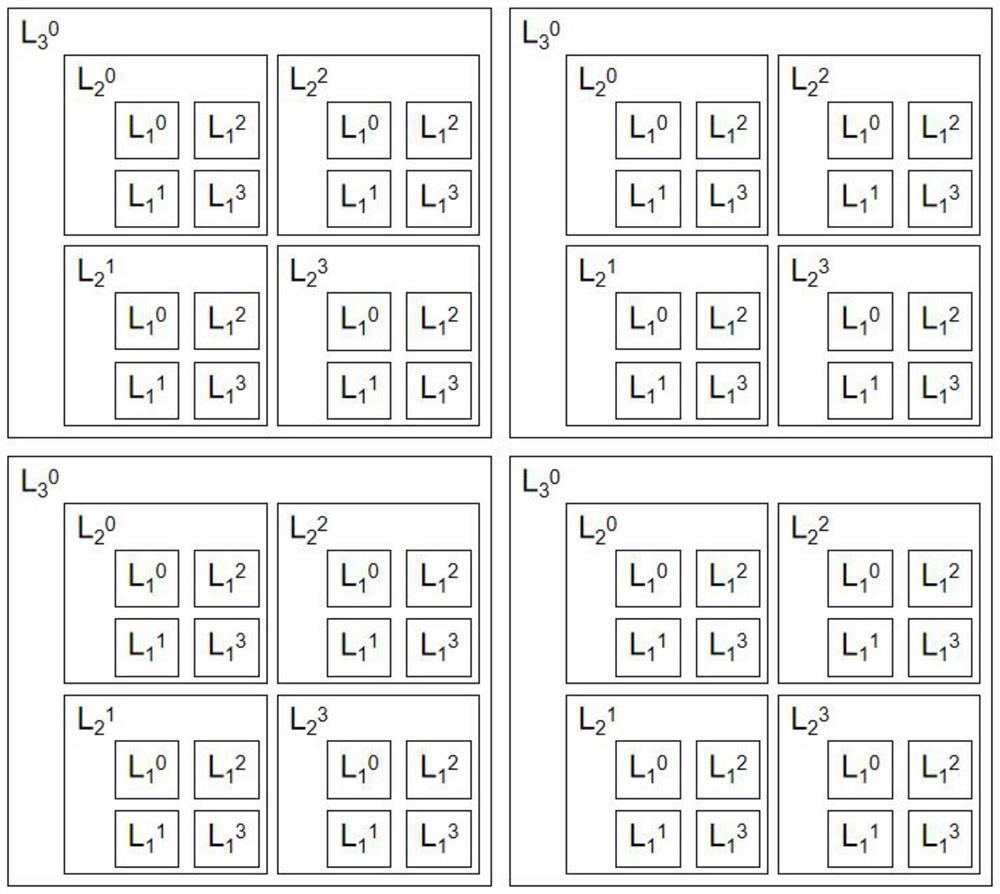

[0063] A routing method based on hierarchical Q-routing planning in this embodiment is implemented in an on-chip network composed of 64 router nodes, 64 resource nodes and several interconnection channels. Refer to figure 1 and figure 2 The shown learning module configuration mode is configured, and the router node includes an input port, an output port, a congestion sensor, a multiplexer, and an access routing table; it is characterized in that the learning module is set in the router node; refer to Figure 4 , the learning module includes: a learning mode arbiter, a hierarchical control module, a routing table selection module, 3 sub-learning modules, and 3 routing tables. You can increase the network structure and the number of sub-learning modules and routing tables to adapt to more router node networks; refer to Figure 7 , the routing method is carried out as follows:

[0064] Step 1: See image 3 , divide all router nodes into a three-layer network structure accordi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More