a synchronous fifo

A technology of registers and multiplexers, applied in the field of digital circuits, can solve the problems of waste of resources, expensive tape-out, and large occupied area, and achieve the effects of avoiding waste of RAM resources, reducing chip area, and facilitating layout and wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

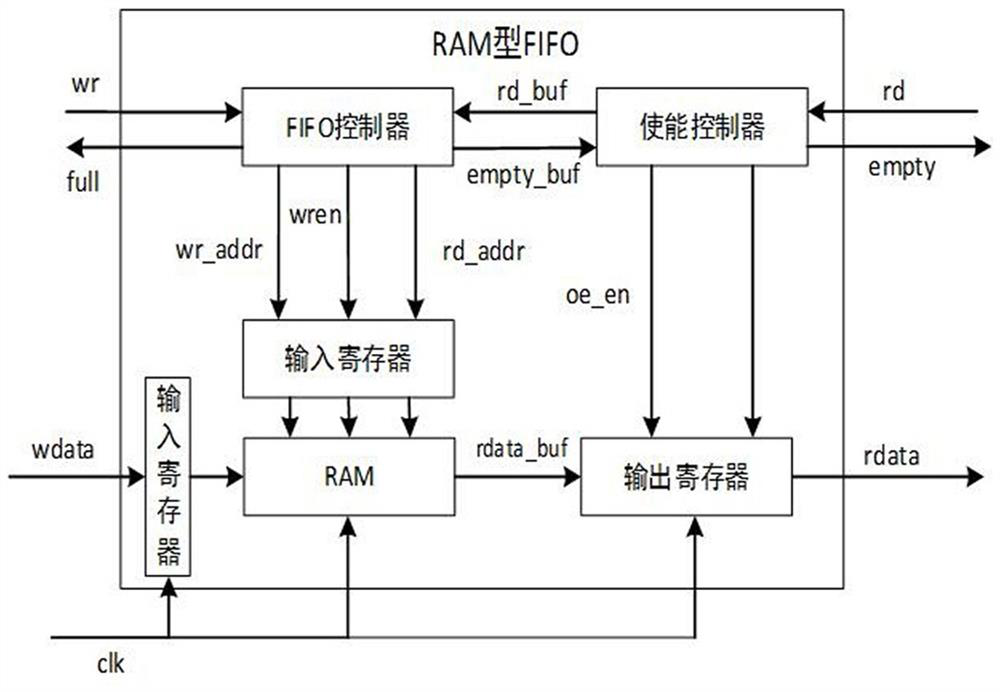

[0049]The core of this application is to provide a synchronous FIFO, which does not need to occupy RAM and avoids the waste of RAM resources. In the design with less memory depth, it can greatly reduce the chip area, save costs, and is more convenient for layout and wiring.

[0050] In order to make the purposes, technical solutions and advantages of the embodiments of the present application clearer, the technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Obviously, the described embodiments It is a part of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

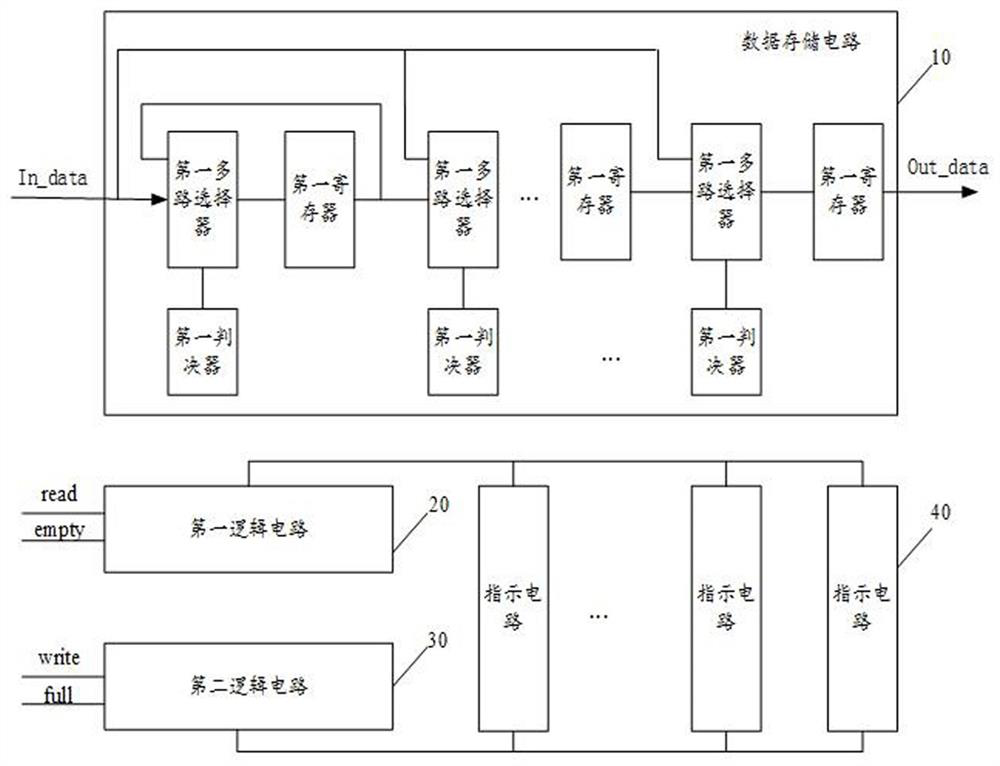

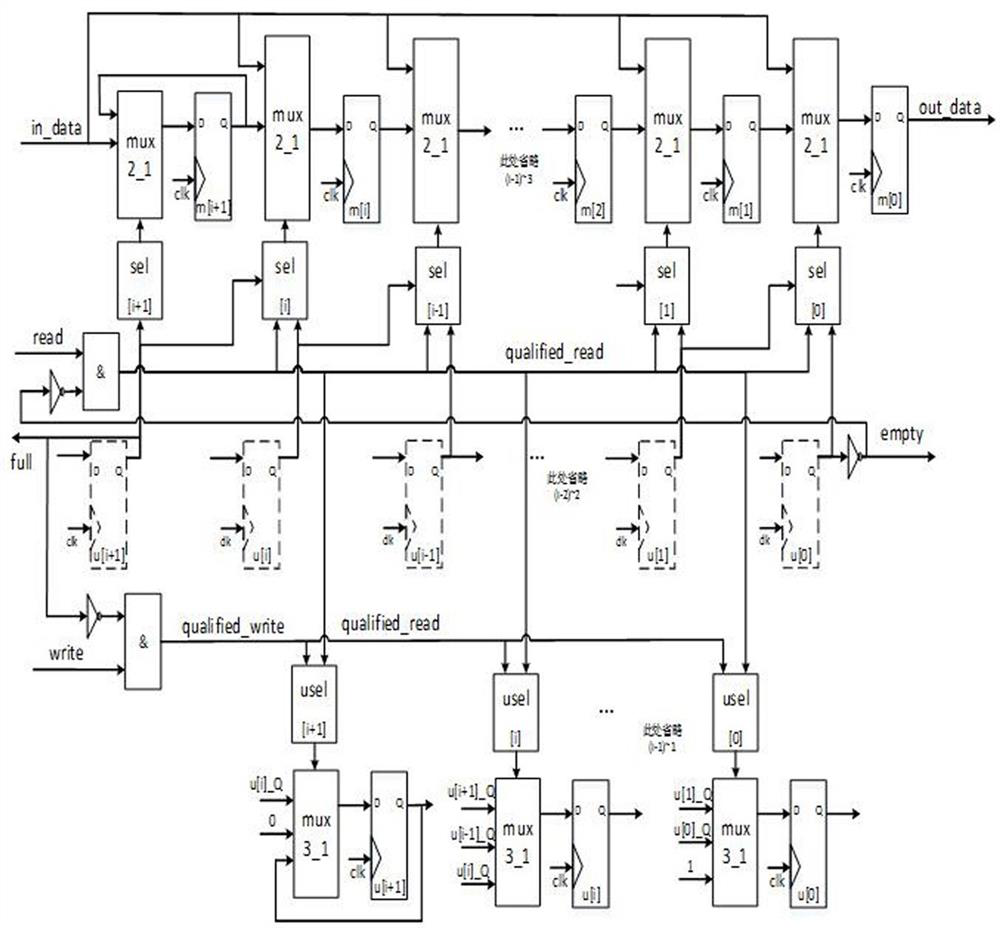

[0051] Please refer to figure 2 , figure 2 For a schematic diagram of a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More