System and method for generating and analyzing verilog circuit netlist compiler

A circuit netlist and compiler technology, applied in compiler construction, code compilation, parser generation, etc., can solve the problems of losing advantages, missing the market, spending a lot of time, etc., to reduce workload, reduce workload, and facilitate The effect of writing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

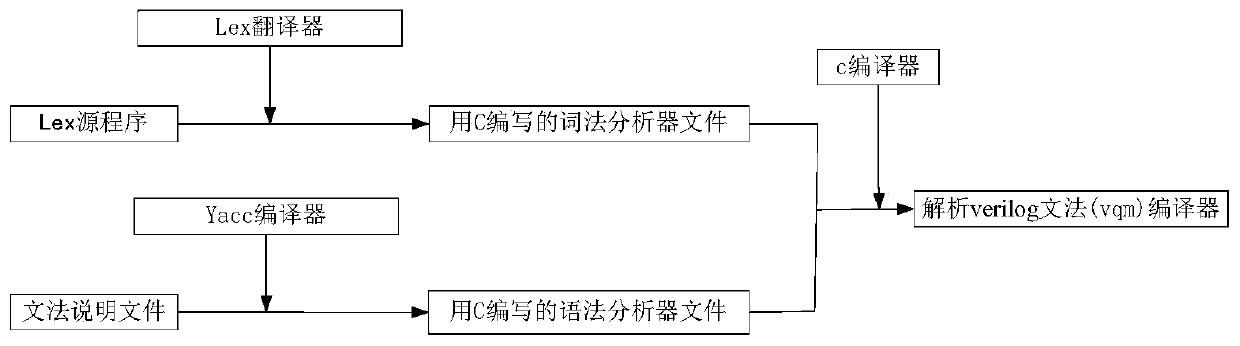

[0019] like figure 2 As shown, the system for generating and analyzing verilog circuit netlist compilers includes: Lex translator, Yacc compiler, and C compiler;

[0020] a Lex translator configured to parse Lex source programs into lexical analyzer files written in C;

[0021] Yacc compiler configured to parse grammar specification files into parser files written in C;

[0022] C compiler configured to generate a parsing verilog grammar compiler from lexer files written in C and parser files written in C.

[0023] The present invention parses the Lex source program into the lexical analyzer file written in C by the Lex translator, the Yacc compiler parses the grammar description file into the lexical analyzer file written in C, and the C compiler uses the lexical analyzer written in C file and a syntax analyzer file written in C to generate and parse the verilog grammar compiler, so for circuit netlists of different formats, it is enough to write the grammar description fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More