Ultra-high-speed aes processor based on fpga and its realization method

An implementation method and processor technology, applied in the field of communications, can solve problems such as large resource occupation, long delay time, complex control logic, etc., and achieve the effects of ensuring effectiveness, improving reliability, and simple storage control logic.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the drawings.

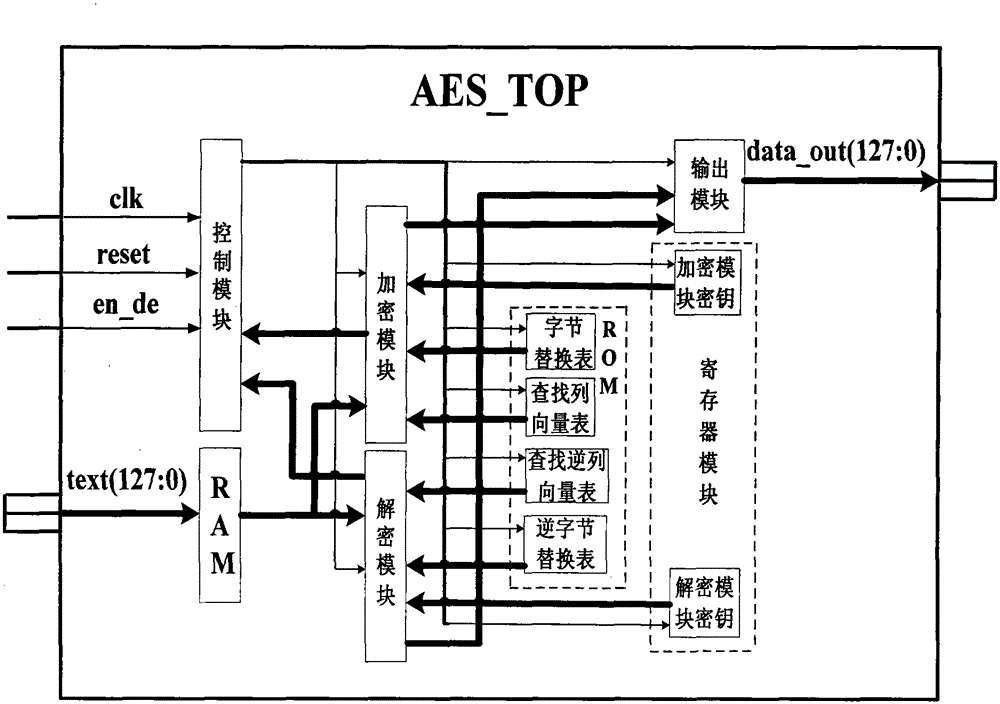

[0043] Reference attached figure 1 The overall structure of the processor of the present invention will be further described.

[0044] The processor of the present invention includes an interface storage area buffer module, a control module, an AES encryption and decryption module, a read-only memory look-up table module, a register module, and an output module; the interface storage area buffer module and the AES encryption and decryption module are connected to the control bus through a data bus ; Read-only memory look-up table module, register module, control module, output module are connected with the control bus through the data bus.

[0045] The interface storage area buffer module is used to temporarily store the data on the input data bus. The interface storage area buffer module includes four random access memory RAMs arranged in the front buffer of the encryption and decryptio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More