A One-bit Full Subtractor Circuit

A technology of full subtractor and circuit, which is applied in the direction of calculation using non-contact manufacturing equipment and calculation using number system, which can solve the problem of increasing circuit area and achieve the effect of facilitating layout and wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

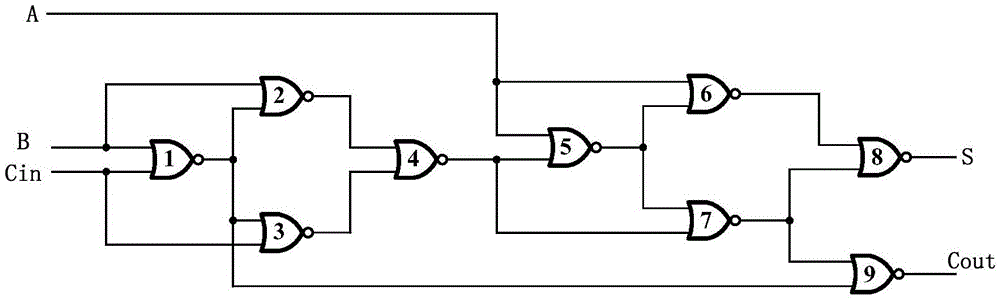

[0022] see figure 1 , the present invention includes symmetrically setting six-level NOR gates, and these six-level NOR gates are connected in series from input to output; The input terminals of the NOR gate and the fifth-level NOR gate are connected with the input signal, and the output terminal of the sixth-level NOR gate is used as the result output terminal. The input signal includes the minuend A, the subtrahend B, and the borrow Cin from the low bit; the output result includes the difference S and the borrow Cout to the high bit; where, the minuend A is input to the fourth-level NOR gate and the first-level NOR gate respectively. On the input terminal of the five-level NOR gate; the subtrahend B and the borrow Cin are both input to the input terminals of the first-level NOR gate and the second-level NOR gate.

[0023] The highest bit bor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More