Generation method and device of CKE signal

A technology of clock signal and generation method, which is applied in the field of communication, can solve the problems of difficulty in layout and wiring of staff, large number of clock enabling and driving circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

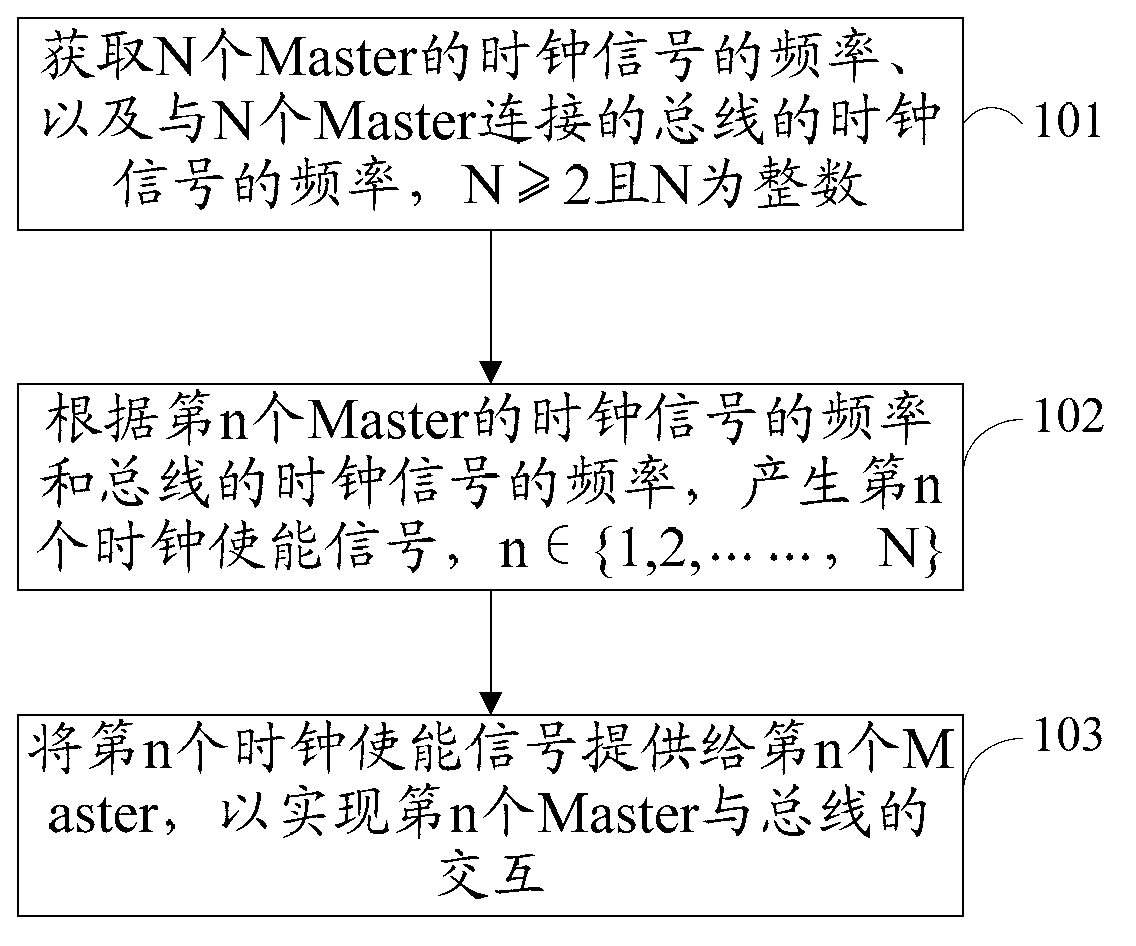

[0051] An embodiment of the present invention provides a method for generating a clock enable signal, see figure 1 , the method includes:

[0052] Step 101: Obtain the frequencies of clock signals of N Masters and the frequencies of clock signals of buses connected to the N Masters, where N≥2 and N is an integer.

[0053] Wherein, the Master and the bus adopt a synchronous architecture, and it is easy to know that in the synchronous architecture, the clock signal of the Master and the clock signal of the bus are both generated by frequency division of the same source clock.

[0054] Further, since the clock signal of the Master and the clock signal of the bus are both generated by frequency division of the same source clock, the frequency of the clock signal of the Master and the frequency of the clock signal of the bus can be represented by their frequency division coefficient relative to the source clock, Such as 2 frequency division, 3 frequency division and so on.

[005...

Embodiment 2

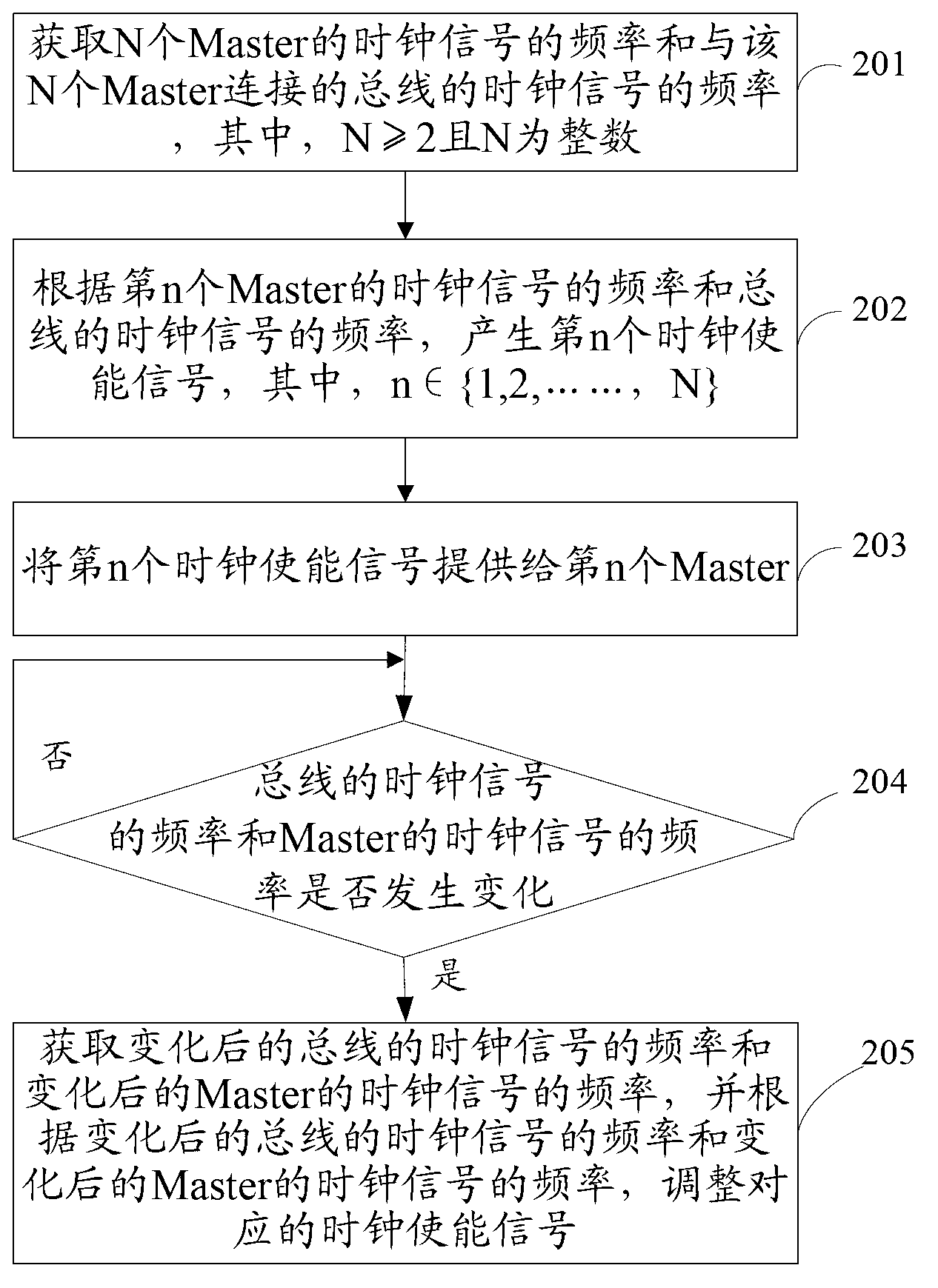

[0067] An embodiment of the present invention provides a method for generating a clock enable signal, see figure 2 , the method includes:

[0068] Step 201: Obtain the frequencies of clock signals of N Masters and the frequencies of clock signals of buses connected to the N Masters, where N≥2 and N is an integer.

[0069] Among them, the N masters and the bus adopt a synchronous architecture. It is easy to know that in the synchronous architecture, the frequency of the clock signal of the bus and the frequency of the clock signal of the Master are generated based on the same source clock, usually in the same frequency or multiplied relationship. Therefore, the frequency of the clock signal of the master and the frequency of the clock signal of the bus can be represented by their frequency division coefficient relative to the source clock, such as frequency division by 2, frequency division by 3, and so on.

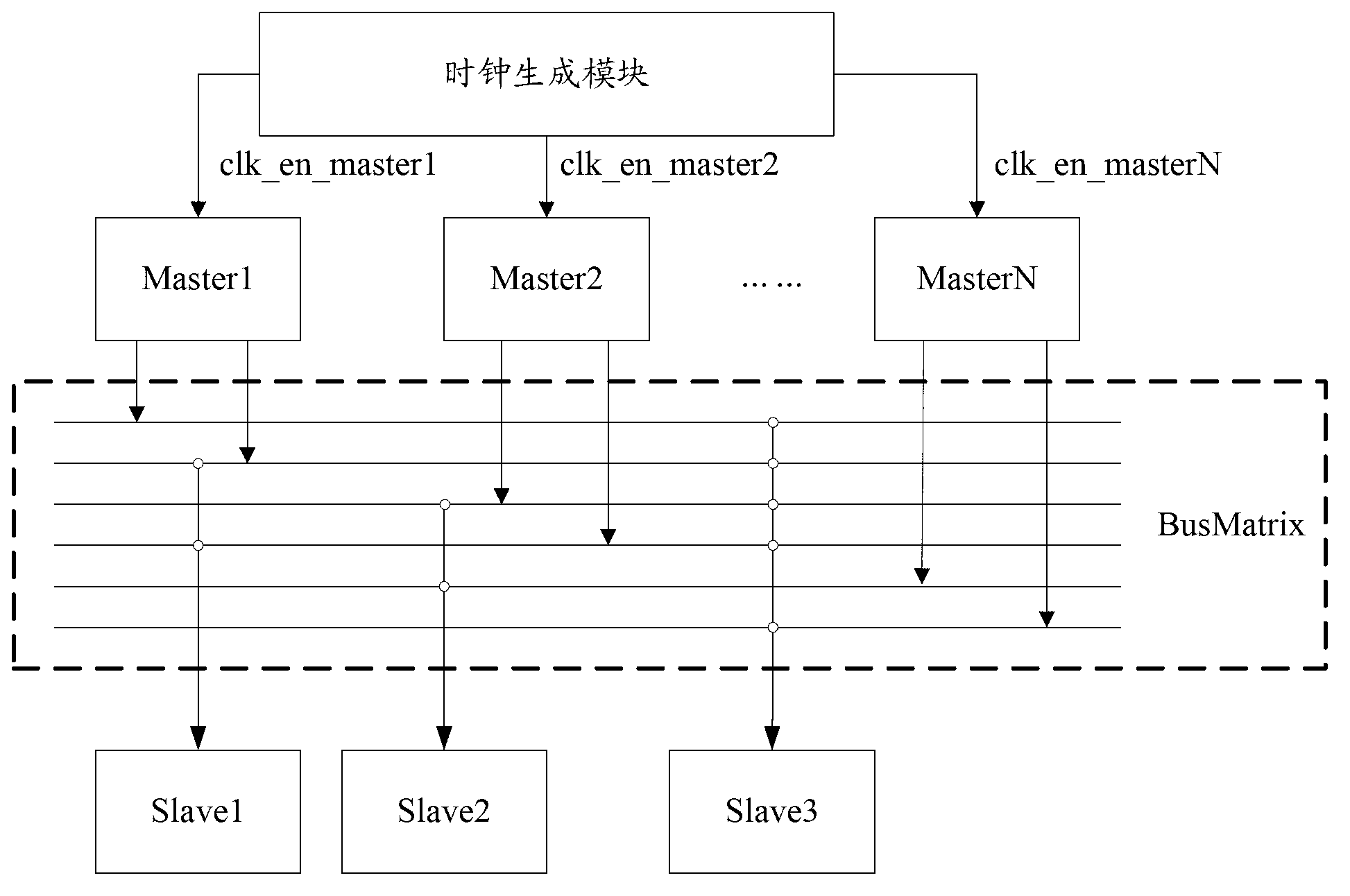

[0070] Specifically, see image 3 , in the synchronization archit...

Embodiment 3

[0091] An embodiment of the present invention provides a method for generating a clock enable signal, see Figure 5 , the method includes:

[0092] Step 301: Obtain the frequencies of clock signals of N Masters and the frequencies of clock signals of buses connected to the N Masters, where N≥2 and N is an integer.

[0093] This step 301 is the same as step 201 in Embodiment 2 of the present invention, and will not be described in detail here.

[0094] Step 302: Generate the nth preliminary clock enable signal based on the source clock according to the frequency of the clock signal of the nth Master and the frequency of the clock signal of the bus, where n∈{1,2,...,N}.

[0095] Wherein, the high level duration of the nth preparation clock enable signal is one clock cycle of the nth Master; and the falling edge of the nth preparation clock enable signal is higher than the rising edge of the clock signal of the corresponding bus Edge, one clock cycle ahead of the nth Master.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More