Optimized BCH (Bose-Chaudhuri-Hocquenghem) decoder

A BCH code and decoding technology, applied in the field of error correction control coding, can solve the problems of wasting hardware resources and ignoring the properties of BCH codes, and achieves the effect of reducing the number of iterations and solving technical difficulties.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

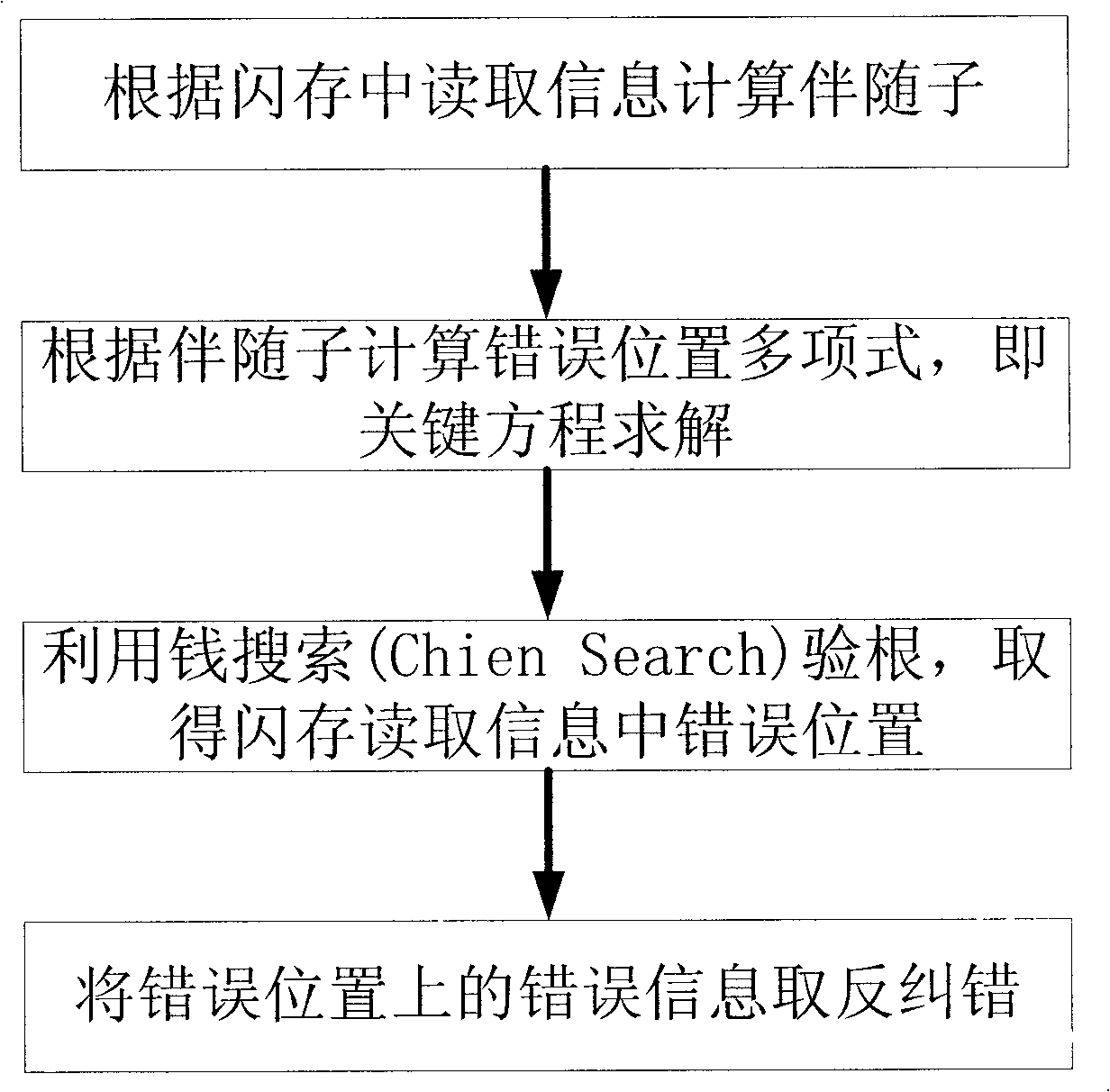

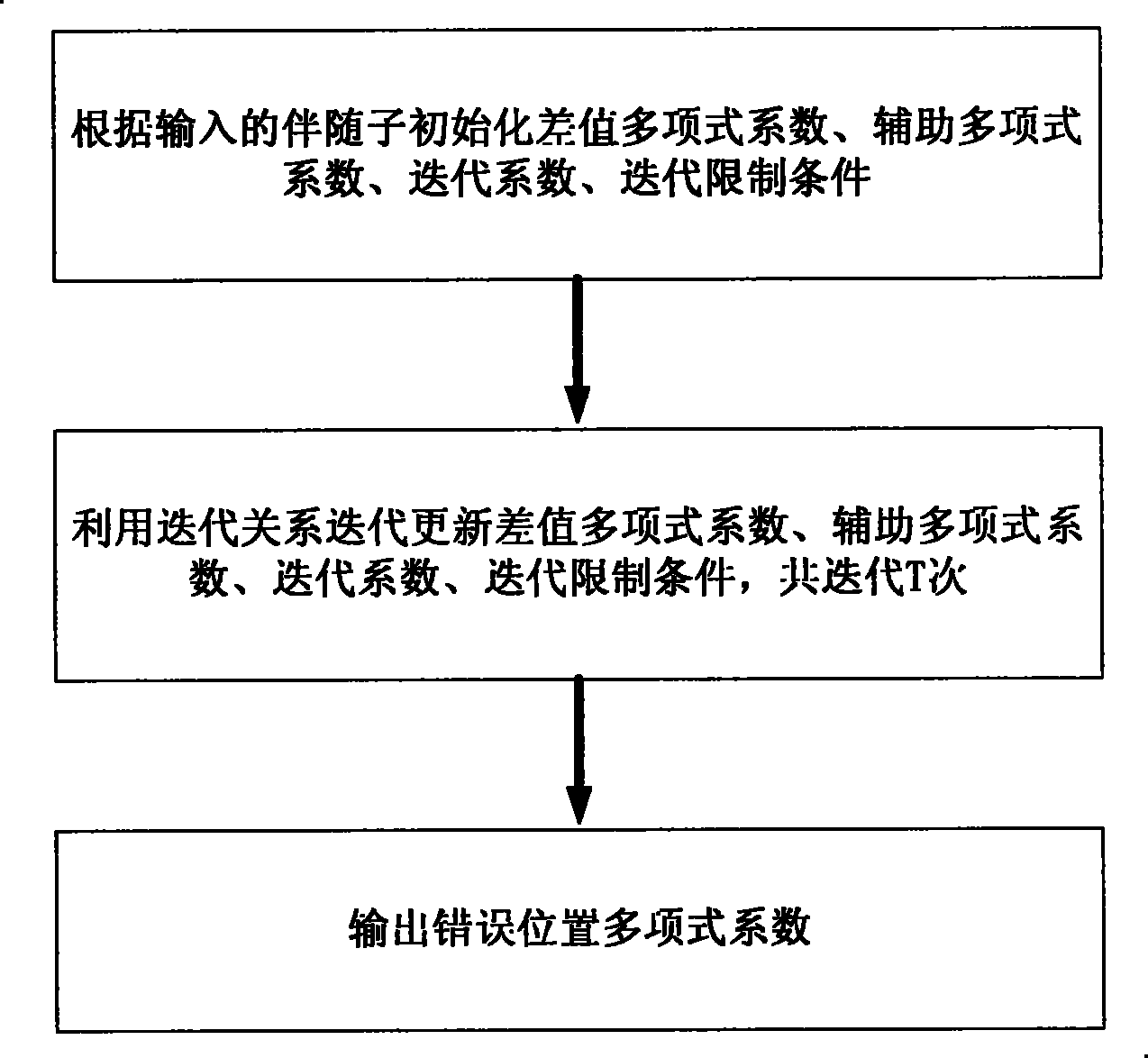

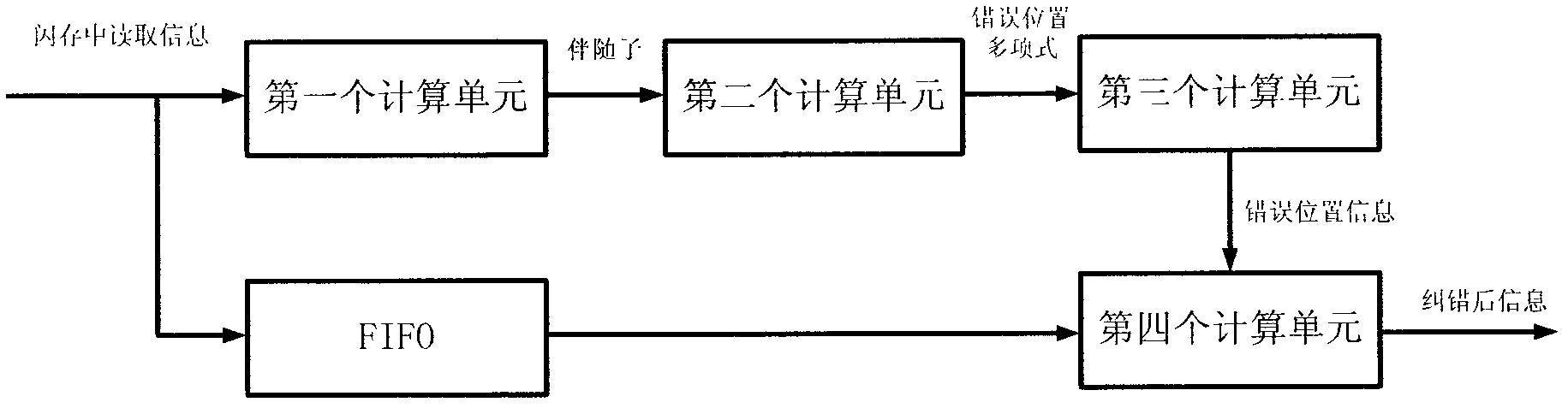

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0027] Many parameters are involved in the specific embodiment, and its meaning is described as follows:

[0028] (1) N: the length of the code word in the BCH code, that is, the length of the information plus the redundant parity bit. In the flash memory controller, N=K+MT.

[0029] (2) K: the length of the information in the BCH code. In the flash memory controller, the information is a shortened code, and K is usually 8192=1KB.

[0030] (3) T: The error correction capability of the BCH code.

[0031] (4) Indicates the largest integer less than or equal to T / 2.

[0032] (5) M: BCH code is based on the operation on Galois field GF(2^M), if K=8192, M=14.

[0033] (6) L: the parallelism of the BCH code, since the flash memory is operated in units of bytes, L=8.

[0034] (7)S i (i=0, 1, . . . , 2T-1): the accompaniments for reading infor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More