Adder

A technology of adder and full adder, which is applied in the field of adder, can solve the problem of long time-consuming and achieve the effect of shortening the time required

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

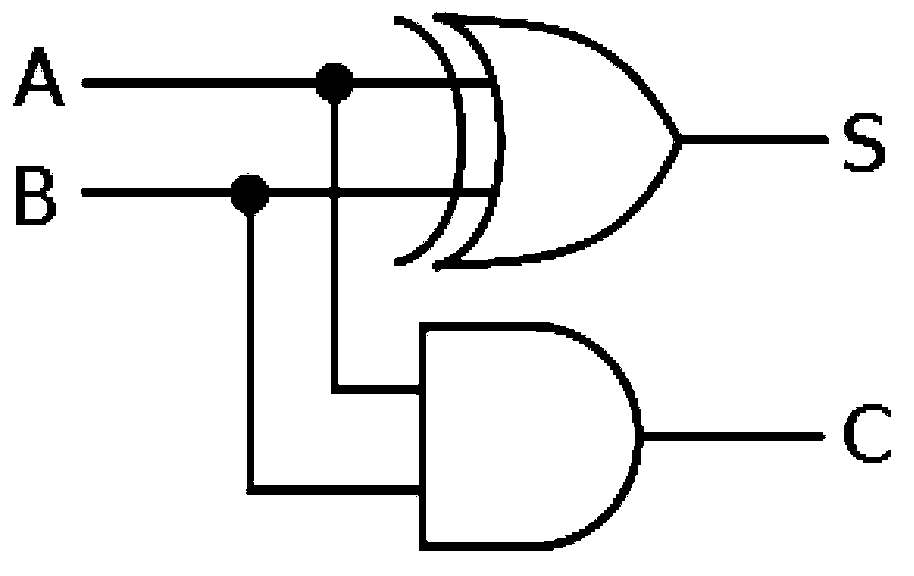

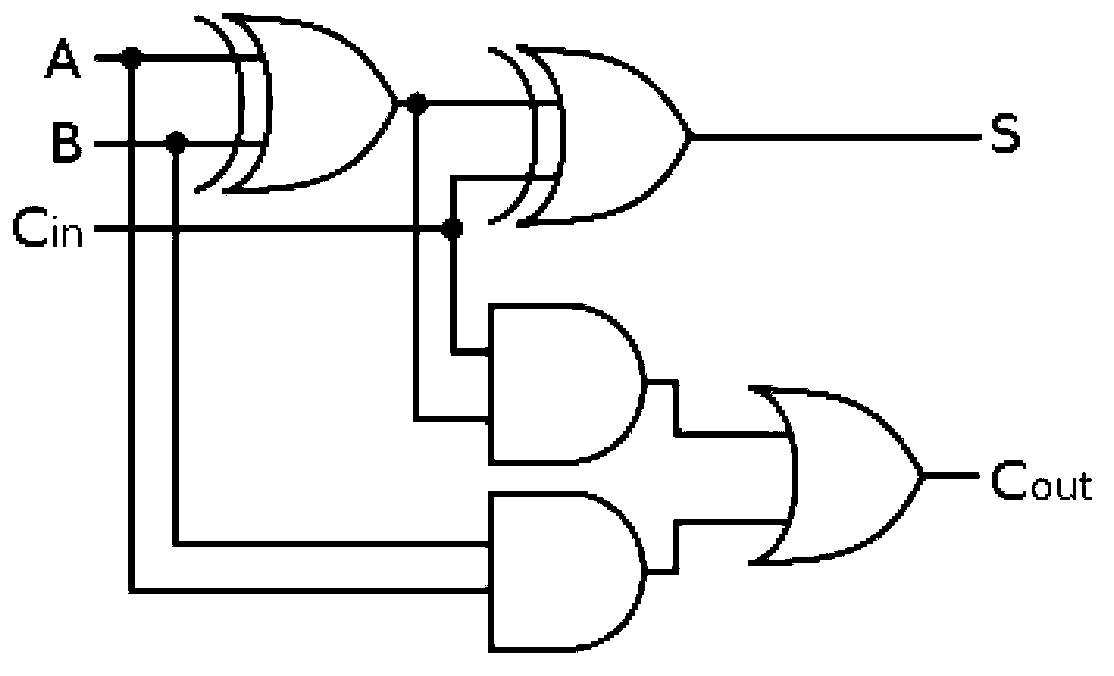

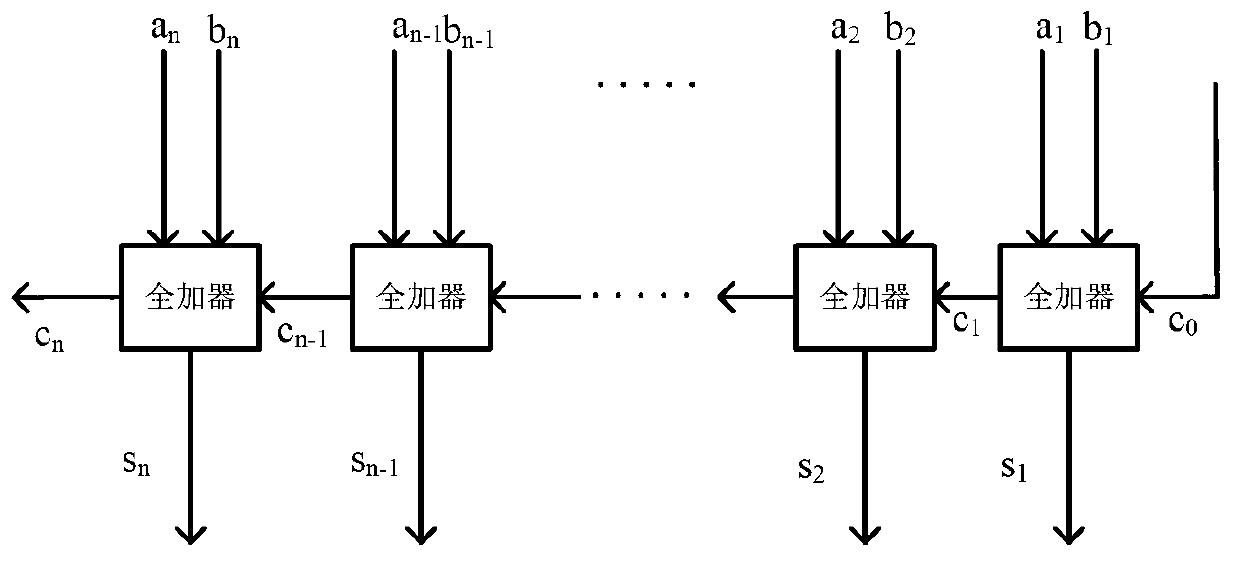

[0039] In order to solve the problem in the prior art that using a one-bit full adder to implement multi-bit binary addition takes a long time, an embodiment of the present invention provides an adder. The adder can process multi-bit one-digit numbers in parallel to realize multi-bit binary addition.

[0040] The embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention. And in the case of no conflict, the embodiments in this description and the features in the embodiments can be combined with each other.

[0041] Embodiments of the present invention firstly provide a simple adder, the specific structural diagram of the adder is as follows image 3 As shown, it includes n one-bit full adders (hereinafter referred to as full adders) that are connected in s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More