Operation core and instruction management method thereof

An instruction management and instruction technology, which is applied to the instruction management of the computing core and the computing core field. It can solve the problems of high hardware overhead, intensified conflict of instruction fetch operations, and congestion of communication networks, so as to improve computing efficiency and reduce the waiting time for instruction fetching. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0038] In the following description, specific details are set forth in order to provide a thorough understanding of the present invention. However, the present invention can be implemented in many other ways than those described here, and those skilled in the art can make similar extensions without departing from the connotation of the present invention. Accordingly, the present invention is not limited to the specific embodiments disclosed below.

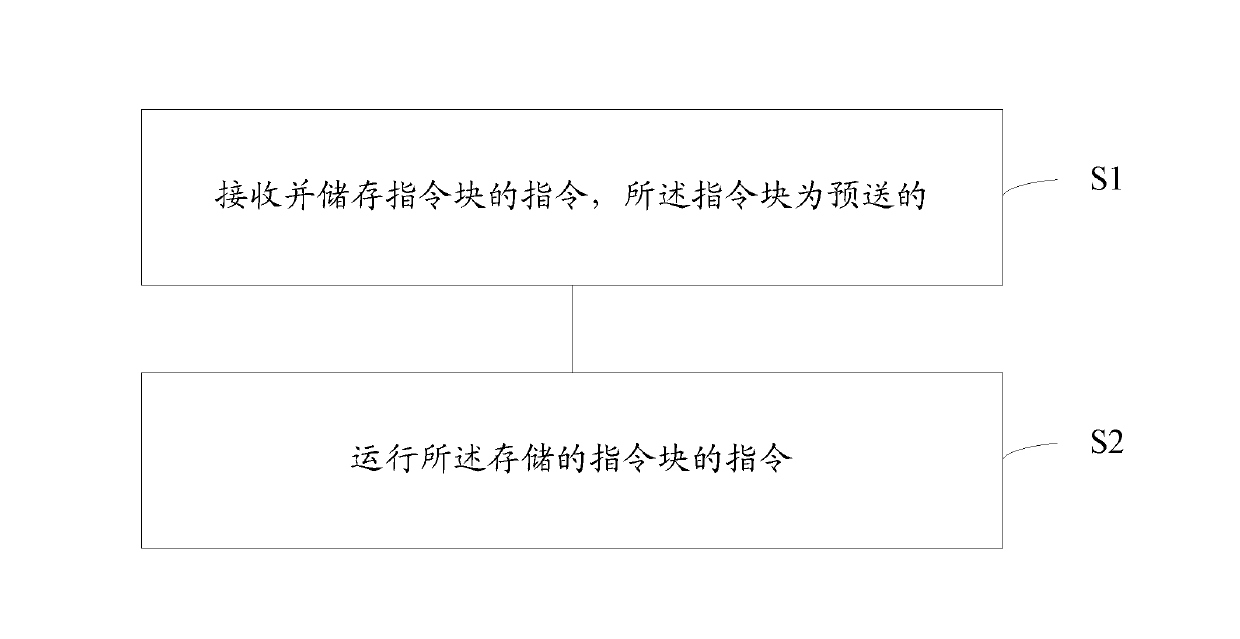

[0039] figure 1 It is a flow chart of the instruction management method of the computing core provided by the embodiment of the present invention, combined below figure 1 Detailed description.

[0040] The instruction management method of the operation core includes:

[0041] Step S1, r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More