Complementary Metal-Oxide-Semiconductor Anti-Latch-Up Structure

An oxide semiconductor, complementary technology, used in semiconductor devices, transistors, electrical solid devices, etc., can solve the problems of limited protection capability, limited effective area of the protective layer, single latch protection structure, etc., to increase the effective area, The effect of improving the discharge current capability and improving the latch protection capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

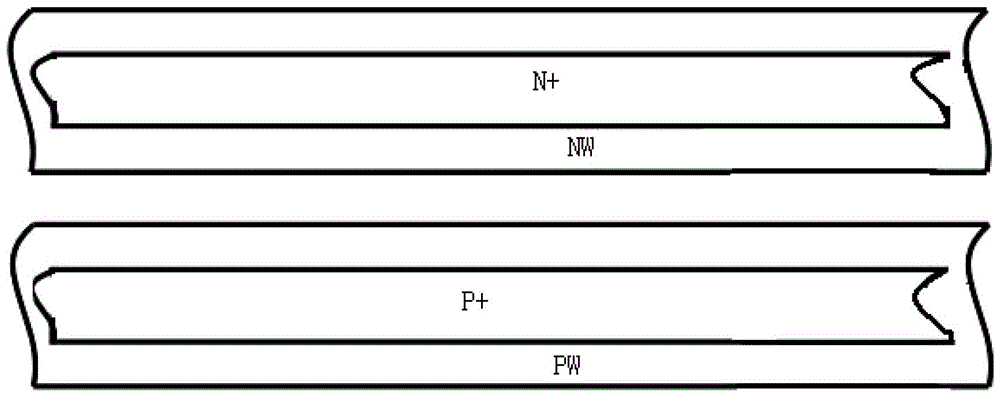

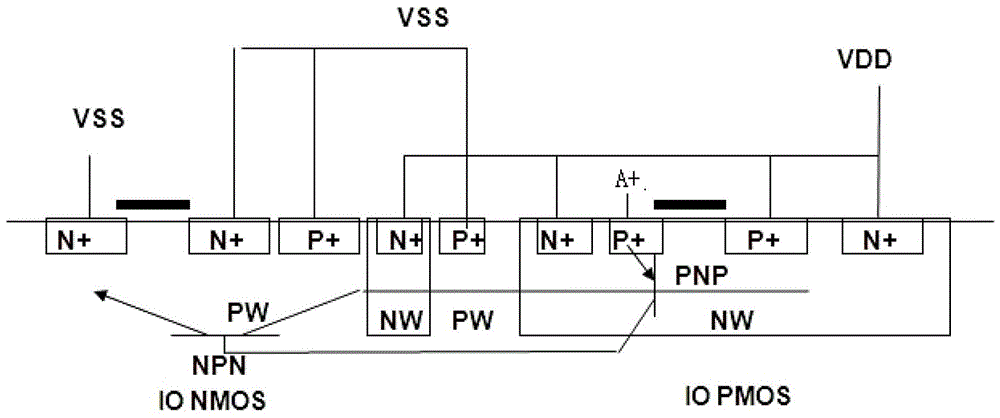

[0031] The complementary metal oxide semiconductor anti-latch-up structure of the present invention includes: an N-type latch-up protection layer and a P-type latch-up protection layer; wherein: the N-type latch-up protection layer can be composed of an N-type deep well and an N-type buried layer of the device , N well, and N-type diffusion region; the P-type latch protection layer can be composed of one or more of the P-type deep well, P-type buried layer, P well, and P-type diffusion region of the device;

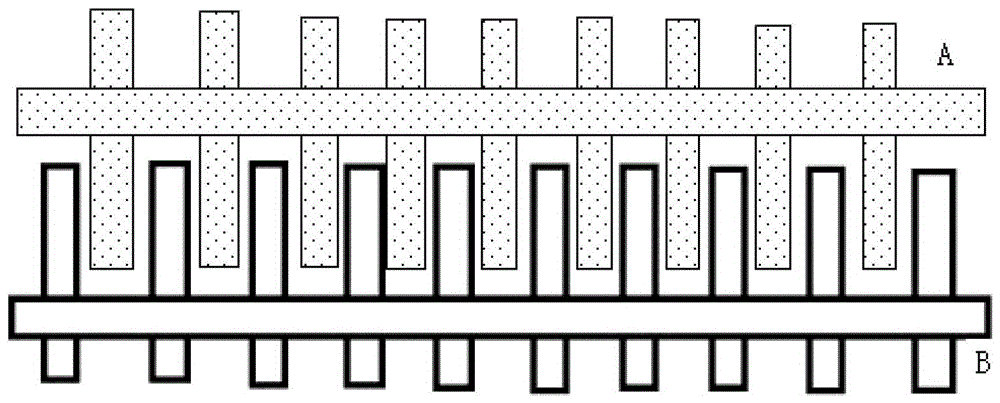

[0032] Such as figure 2 As shown, wherein, the N-type latch protection layer and the P-type latch protection layer are arranged in multiple groups in a cross shape.

[0033] The width of the N-type latch protection layer and the P row latch protection layer is between 0.5 um and 50 um, preferably 10 um, 20 um, 25.25 um, 30 um, and 40 um.

[0034] The length of the intersection of the N-type latch protection layer and the P-type latch protection layer is between 0.5um an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More