Fan-out-type wafer-level packaging structure and manufacturing process

A wafer-level packaging and manufacturing process technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as difficulty, slippage, and dislocation are difficult to control, and achieve the effect of improving warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with specific drawings.

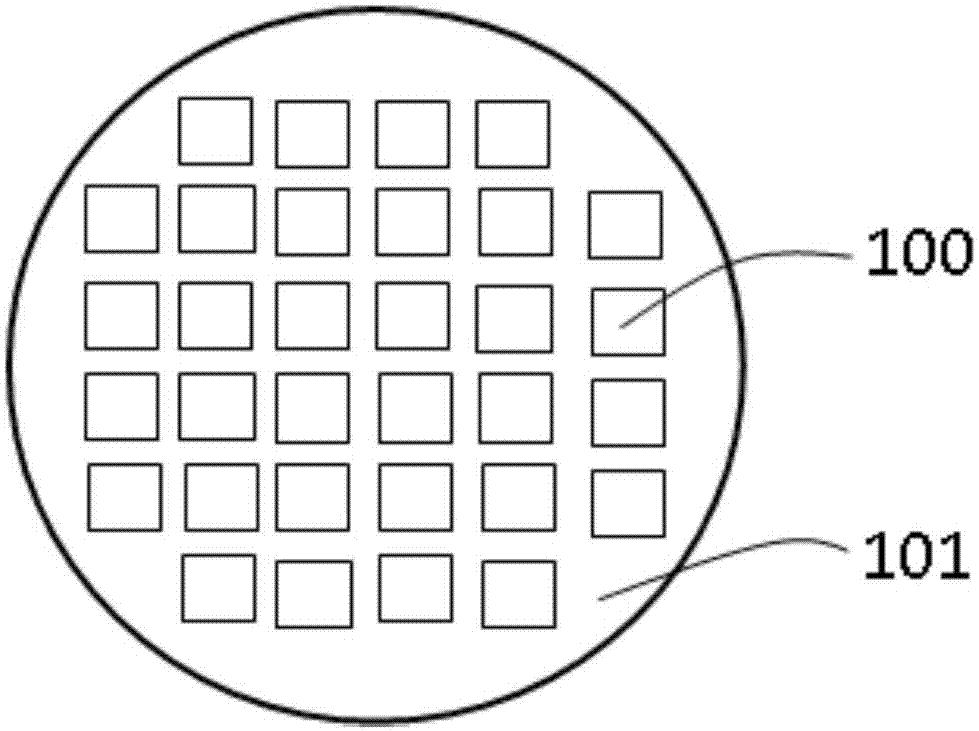

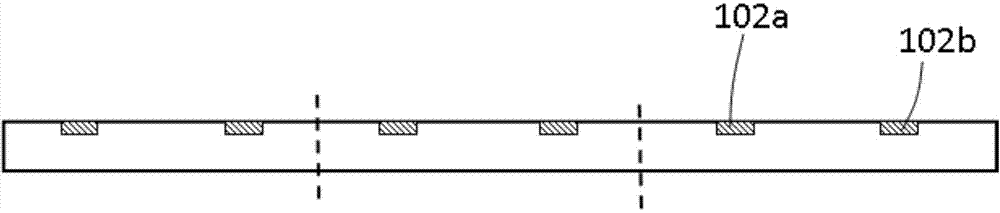

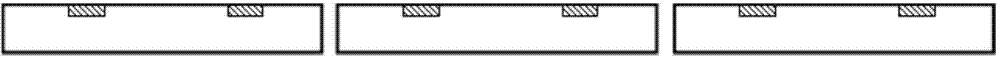

[0031] Such as Figure 9a , Figure 9b As shown: the fan-out wafer level packaging structure includes a chip 100 with a first metal electrode 102a and a second metal electrode 102b and a metal layer 203, and the chip 100 and the metal layer 203 are molded into a whole by a plastic packaging material 501; The front side 100a of the chip 100 is located on the same plane as the front side 501a of the molding material 501, the back side 100b of the chip 100 and a surface 203a of the metal layer 203 are located on the same plane as the back side 501b of the molding material 501, and the height of the metal layer 203 is smaller than that of the chip 100, so that the other surface 203b of the metal layer 203 is located in a different plane from the front 100a of the chip 100; a dielectric layer 901 is arranged on the front 501a of the plastic encapsulation material 501, and a rewiri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More