Accurate-period simulation model for reconfigurable special processor core and hardware architecture thereof

A processor core and simulation model technology, applied in software simulation/interpretation/simulation, electrical digital data processing, special data processing applications, etc., can solve problems such as short time to market, long design cycle, and increased construction period, and achieve good software Hardware interface, fast simulation speed, easy to build effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The solution of the present invention will be described in detail below in conjunction with the accompanying drawings.

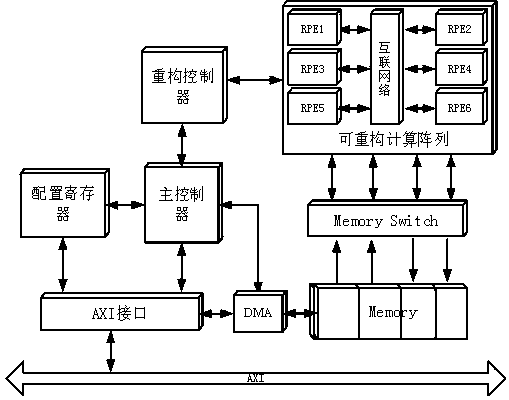

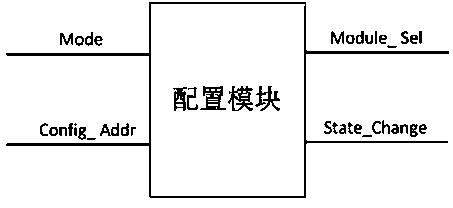

[0030] The cycle-accurate simulation model of the reconfigurable dedicated processor core provided in this embodiment is based on the SystemC cycle-accurate model, including a control module, a transmission module and an operation module. The control module sends configuration parameters for controlling the interaction with the outside of the model and the working status of each module inside the model. The transmission module receives the configuration parameters sent by the control module, and is used for data transmission with the outside of the dedicated processor core and inside the dedicated processor core. The operation module receives the configuration parameters sent by the control module, and is used to perform operations according to the algorithm selected and set by the received configuration parameters.

[0031] Furthermore, the control ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More