Multi-core cascade-based cycle accurate model of vector calculation hardware accelerator

A hardware accelerator, accurate model technology, applied in digital computer components, architectures with a single central processing unit, instruments, etc., to achieve the effect of fast simulation speed and high simulation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in detail below in conjunction with the accompanying drawings and specific implementation cases.

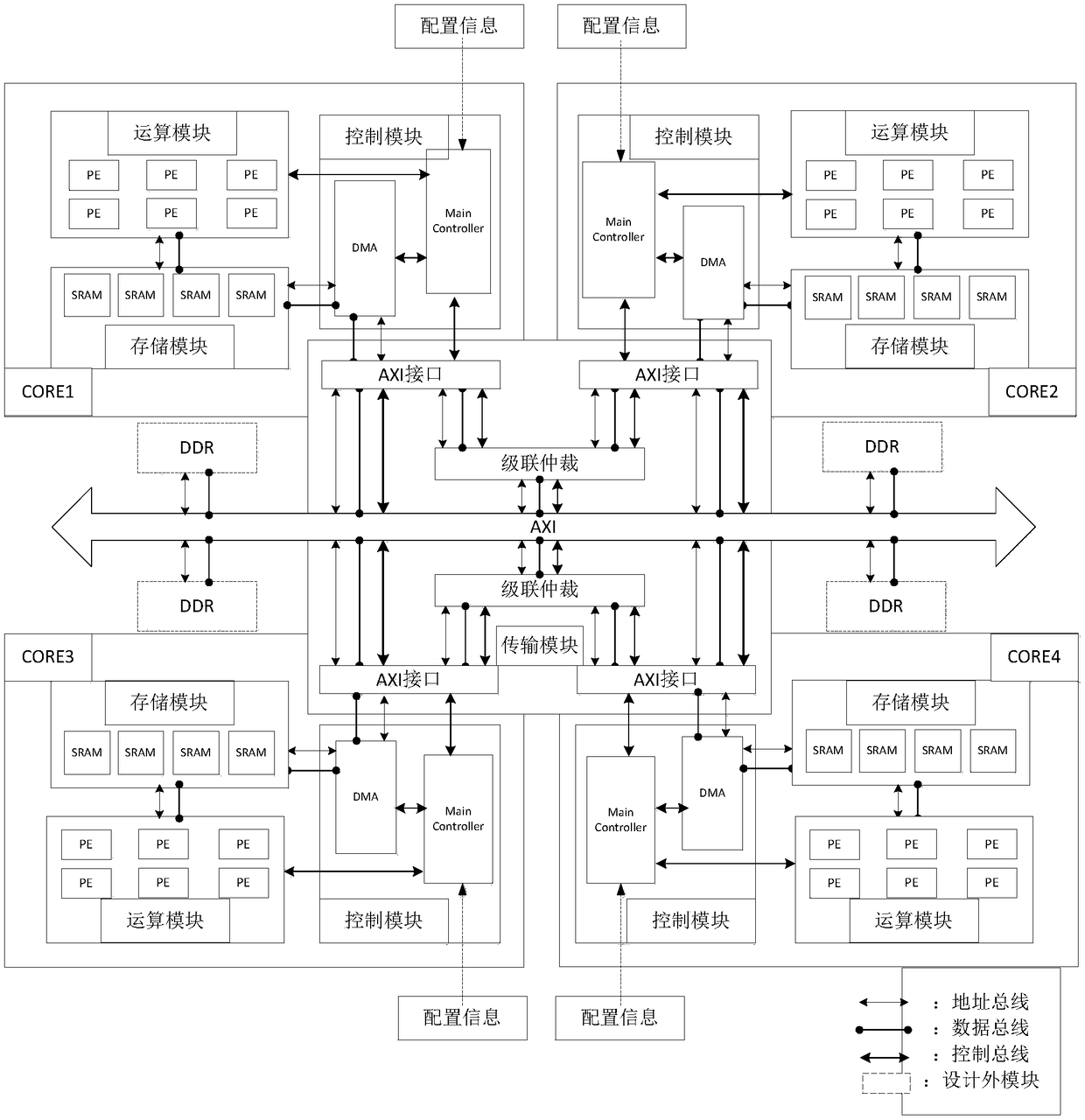

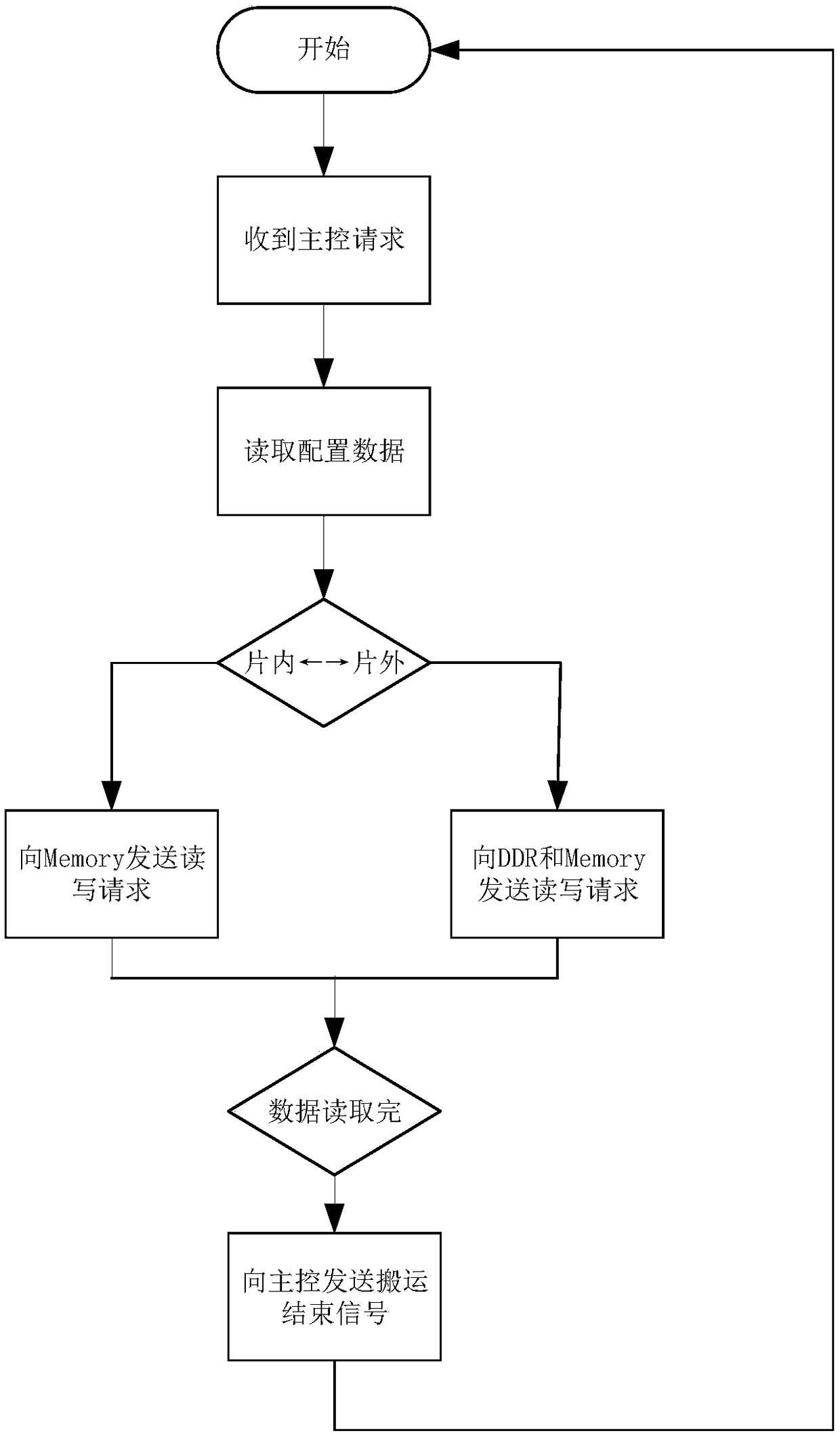

[0027] The cycle-accurate simulation model of the multi-core cascade of the vector operation hardware accelerator provided in this embodiment adopts the SystemC cycle-accurate model, including a control module, a transmission module, an operation module and a storage module. The control module generates configuration parameters, which are used to control the interaction with the outside of the model, the working status of each module inside the model, and switch the mode of data transmission, data division and data address mapping according to the number of calculation points of different algorithms; the transmission module receives all The configuration parameters generated by the above control module are used for data and address transmission with the outside of the dedicated processor core, inside the dedicated processor core, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More