Polycrystalline silicon film morphology forming method

A polysilicon and film technology, applied in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problem of inconsistency in the longitudinal width of polycrystalline strips, achieve uniform longitudinal width, reduce or eliminate narrow edges. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

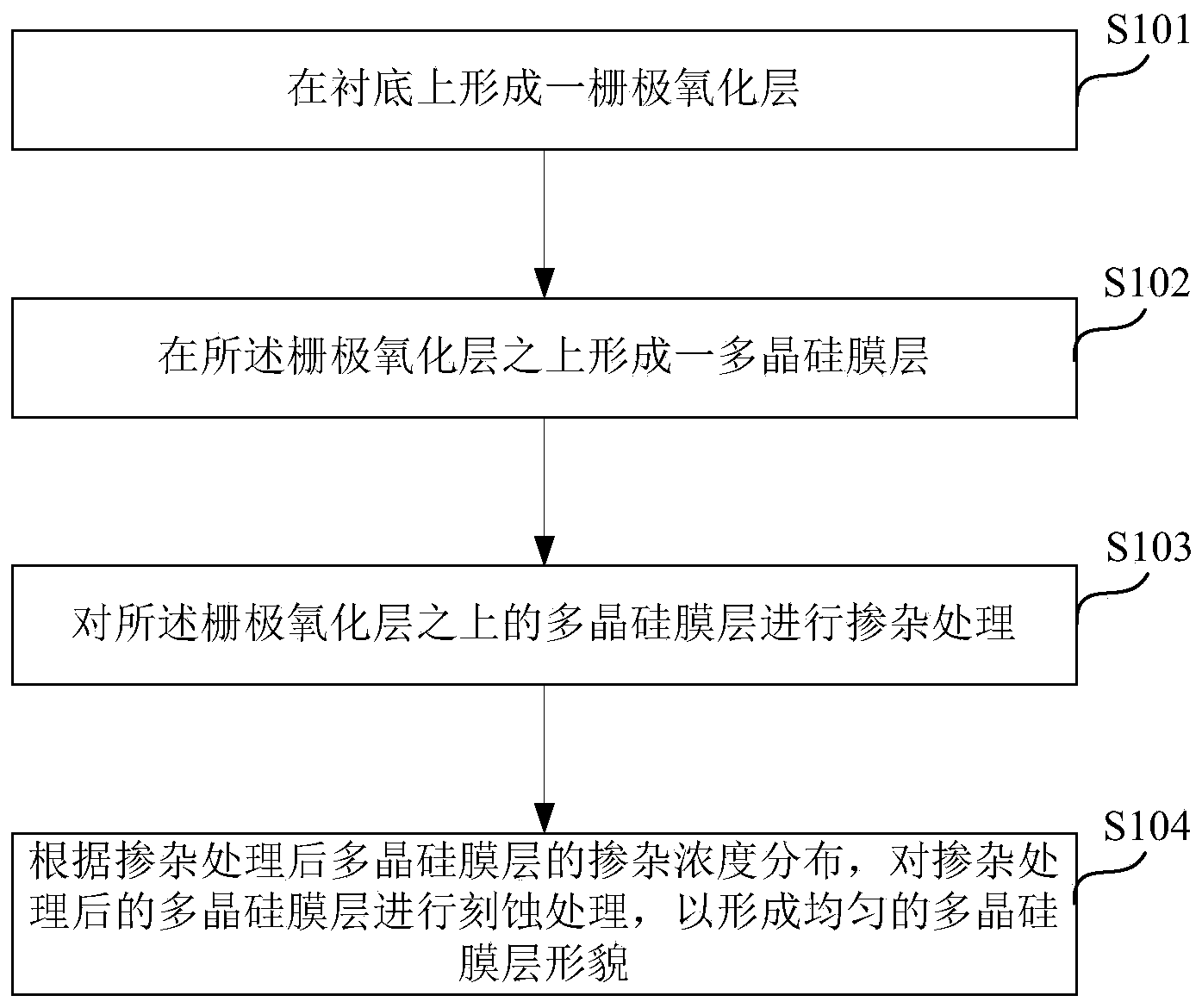

[0033] figure 1 It is a schematic flow chart of a method for forming a polysilicon film layer morphology in an embodiment of the present invention; as figure 1 As shown, it can specifically include:

[0034] S101, forming a gate oxide layer on the substrate;

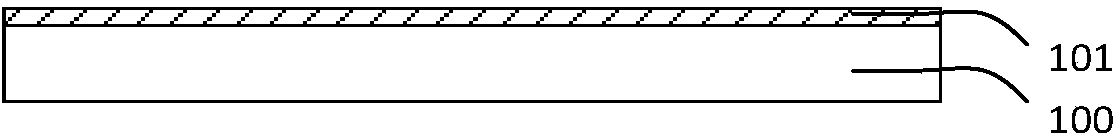

[0035] In this embodiment, the gate oxide layer may be formed by thermally oxidizing the substrate. The thickness of the gate oxide layer is 50-200A, preferably 100A. For details, see figure 2 , figure 2 It is a schematic diagram of the structure of the semi-finished product after step S101 according to Embodiment 1 of the present invention. A gate oxide layer 101 has been formed on the substrate 100 .

[0036] It should be noted that the formation of the gate oxide layer is not limited to the method of thermally oxidizing the substrate, and other methods may also be used according to process requirements.

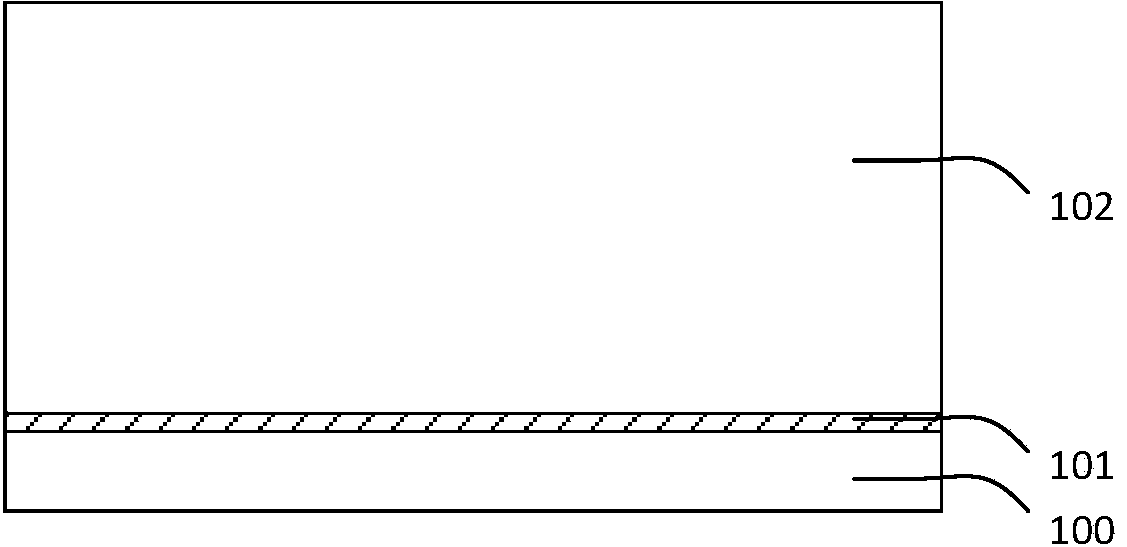

[0037] S102, forming a polysilicon film layer on the gate oxide layer;

[0038] In this embodiment, consi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com