A Clock Control Circuit And Method

A clock control and circuit technology, applied in program control design, electrical digital data processing, signal generation/distribution, etc., can solve problems such as difficulty in implementing large processors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

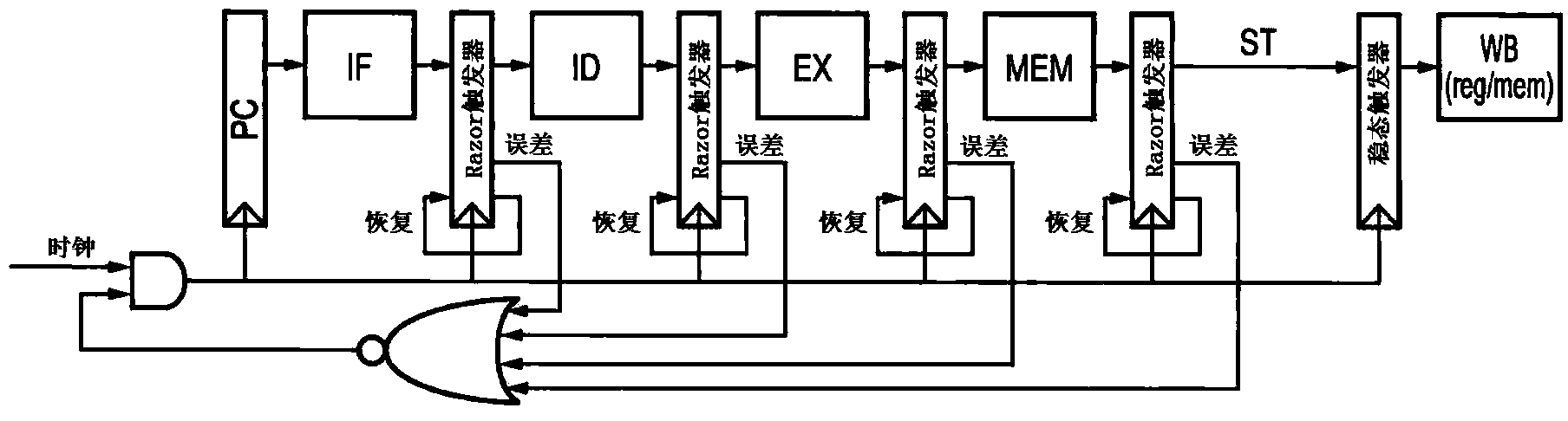

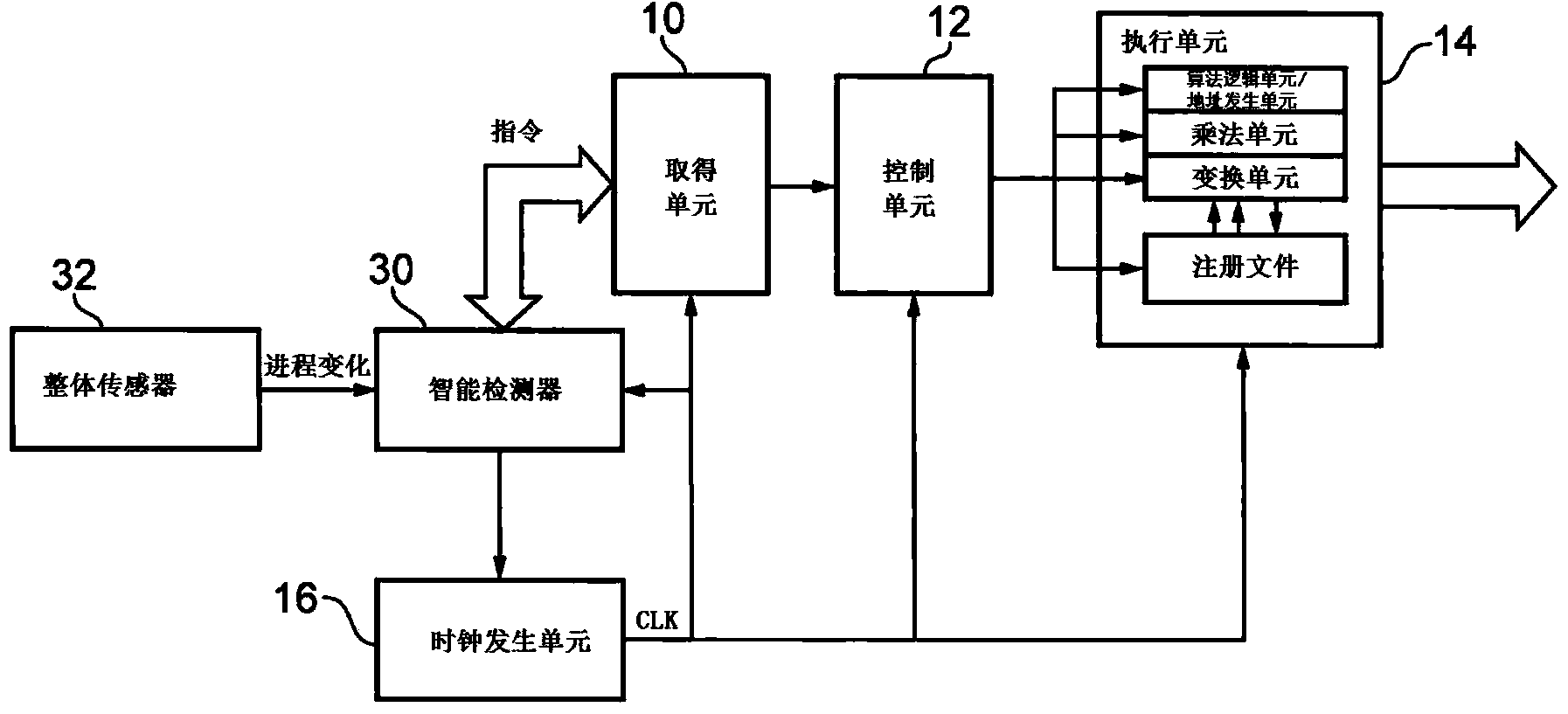

[0048] The present invention provides a clock control circuit that can be added to any on-the-fly processor to solve timing problems due to variations in process output and environmental conditions. Detect critical instructions (executed as critical paths) during environmental detection (such as process, temperature, and voltage). This information is used to control cycle stealing.

[0049] The present invention thus provides an architecture that is tolerant to variation to provide better than worst-case CPU designs. The present invention uses an intelligent error predictor, which is based on critical instructions. An intelligent in-transit stall unit is used to preserve the in-transit context and allow the correct execution of critical orders. If a critical instruction is executed, there will only be a penalty of one clock cycle.

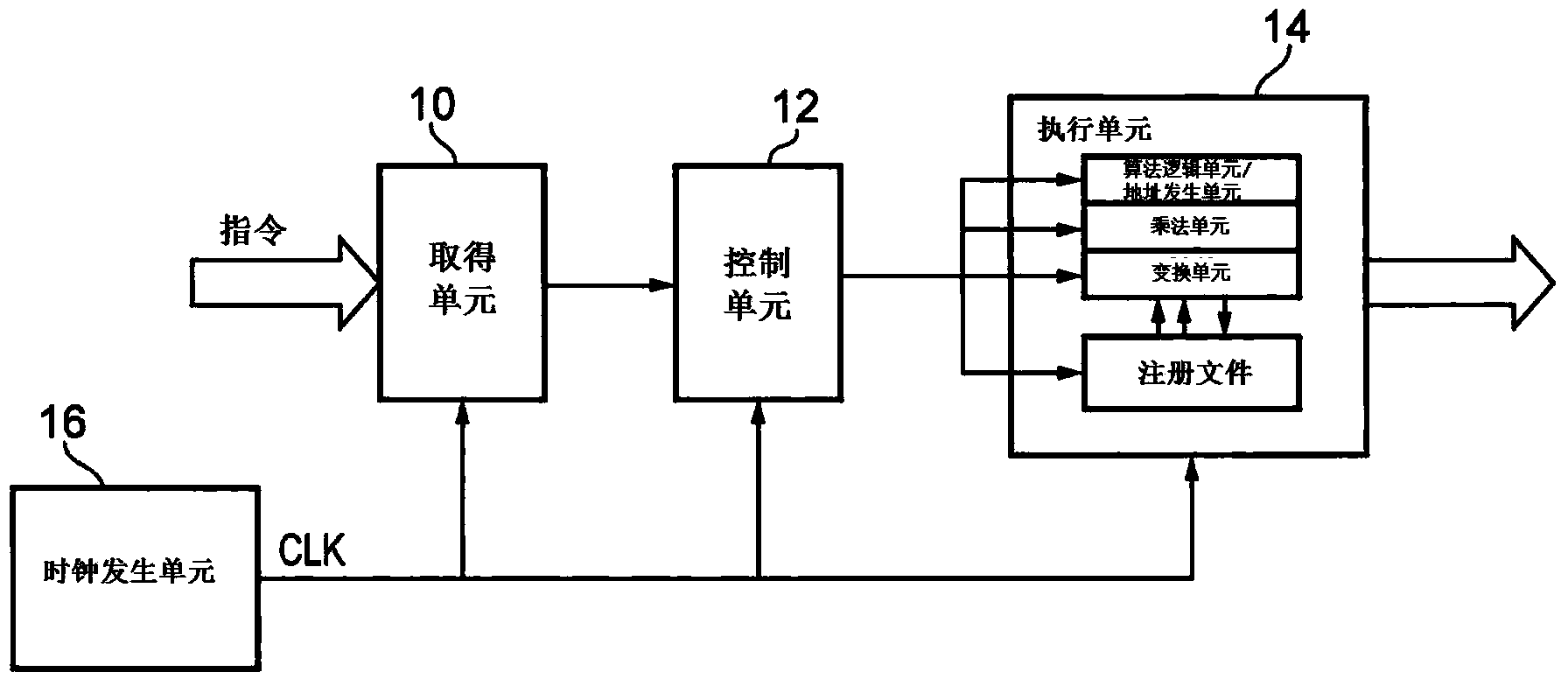

[0050] figure 2 Shown is a block diagram of a general-purpose processor into which the system of the present invention can be incorporated. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More