Low-temperature and shock-resistant semiconductor package structure

A packaging structure and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of large size and inertia of high-power chips, and achieve low operating temperature rise and extended service life. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

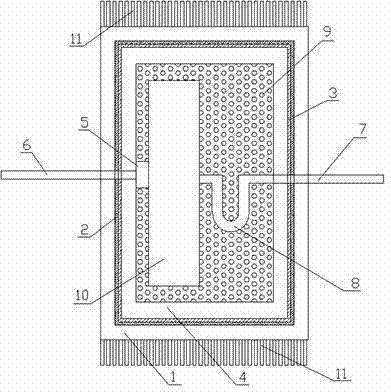

[0012] Such as figure 1 As shown, a low-temperature shock-resistant semiconductor packaging structure includes a functional device, a packaging layer and a heat sink 11, the packaging layer wraps and covers the functional device, and the functional device includes a large-area contact piece 5, a semiconductor device 10, a micro tension U U-shaped conductive shrapnel 8 and elastic thermally conductive colloid 9, the elastic thermally conductive colloid 9 wraps and covers the large-area contact piece 5, the semiconductor device 10 and the micro-tension U-shaped conductive shrapnel 8, and the large-area contact piece 5 is electrically connected to the semiconductor device 10, The semiconductor device 10 is electrically connected to the micro-tension U-shaped conductive elastic piece 8, the large-area contact piece 5 is electrically conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More