Reading circuit of non-volatile memory capable of preventing side channel attack

A memory read and bypass attack technology, applied in static memory, read-only memory, information storage, etc., can solve problems such as read bypass signal leakage, unacceptable array area, and extended read time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063] The specific implementation of the present invention will be further described in detail below in conjunction with the examples.

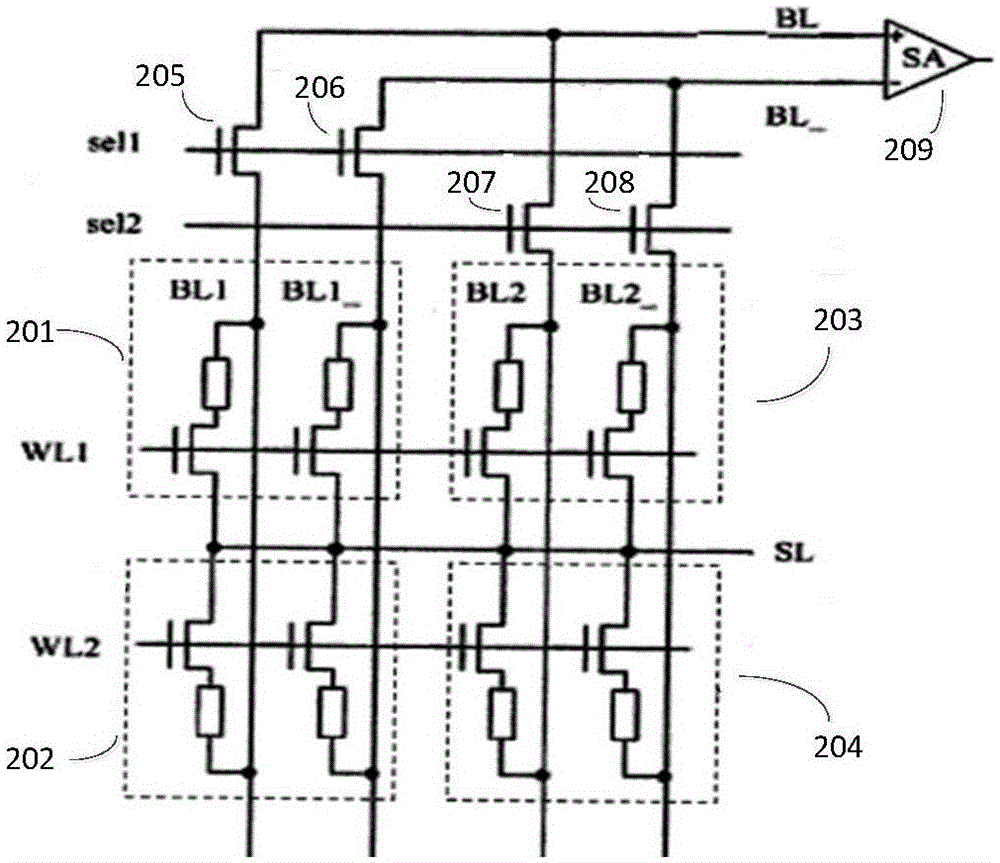

[0064] Figure 7 is based on Figure 4 A specific embodiment of the first circuit structure proposed by the present invention is shown, taking a resistive memory as an example, and focusing on an implementation of a voltage difference amplifier circuit. Figure 7 Among them, the storage unit 701 is a 1T1R unit composed of a transistor and a resistive unit R connected in series, and the reference unit 702 in the on state is a reference unit composed of a transistor connected in series with a resistive unit RL preset to low resistance. Unit, the reference unit 703 in the non-conducting state is a reference unit composed of a transistor connected in series with a resistive switching unit RH preset to high resistance.

[0065] The voltage difference amplifying circuit 707 includes an inverter Inv1 721 whose inversion voltage is specially adjus...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More