Gate turn-on voltage compensation circuit, display panel, driving method and display device

A gate opening and voltage compensation technology, applied to static indicators, instruments, etc., can solve the problems of opening voltage differences, affecting the quality of display images, and horizontal split screens

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

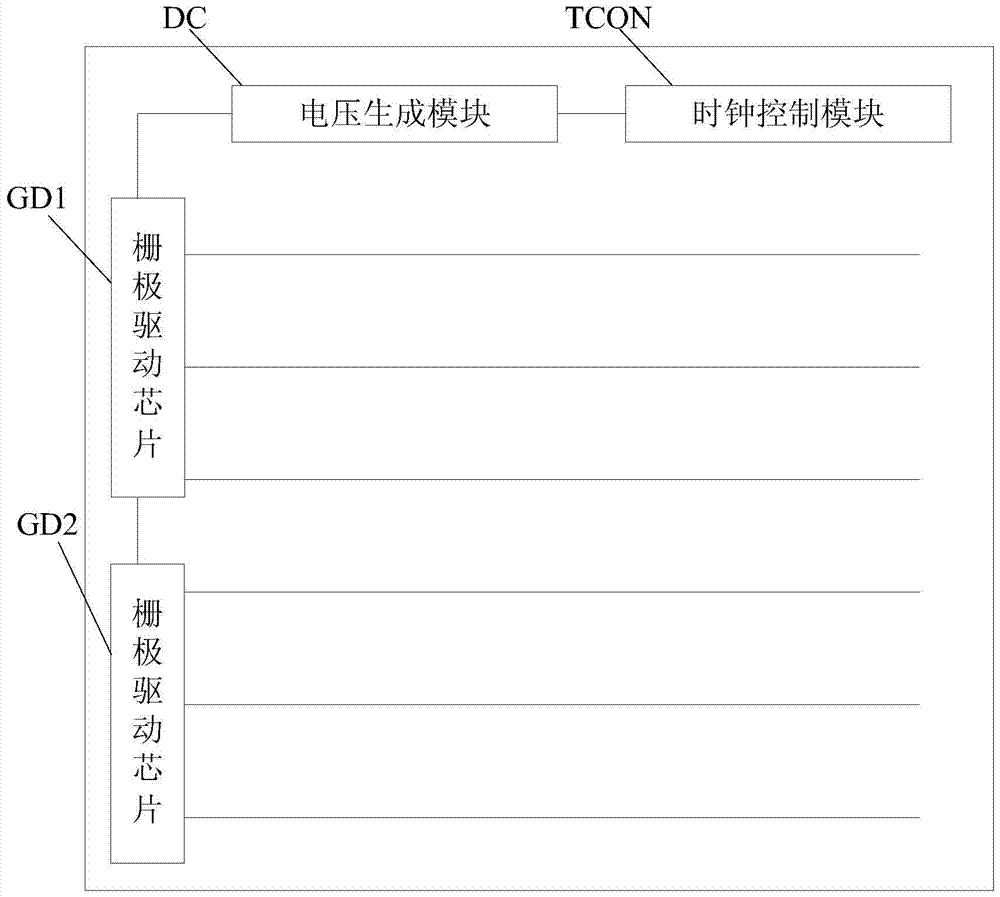

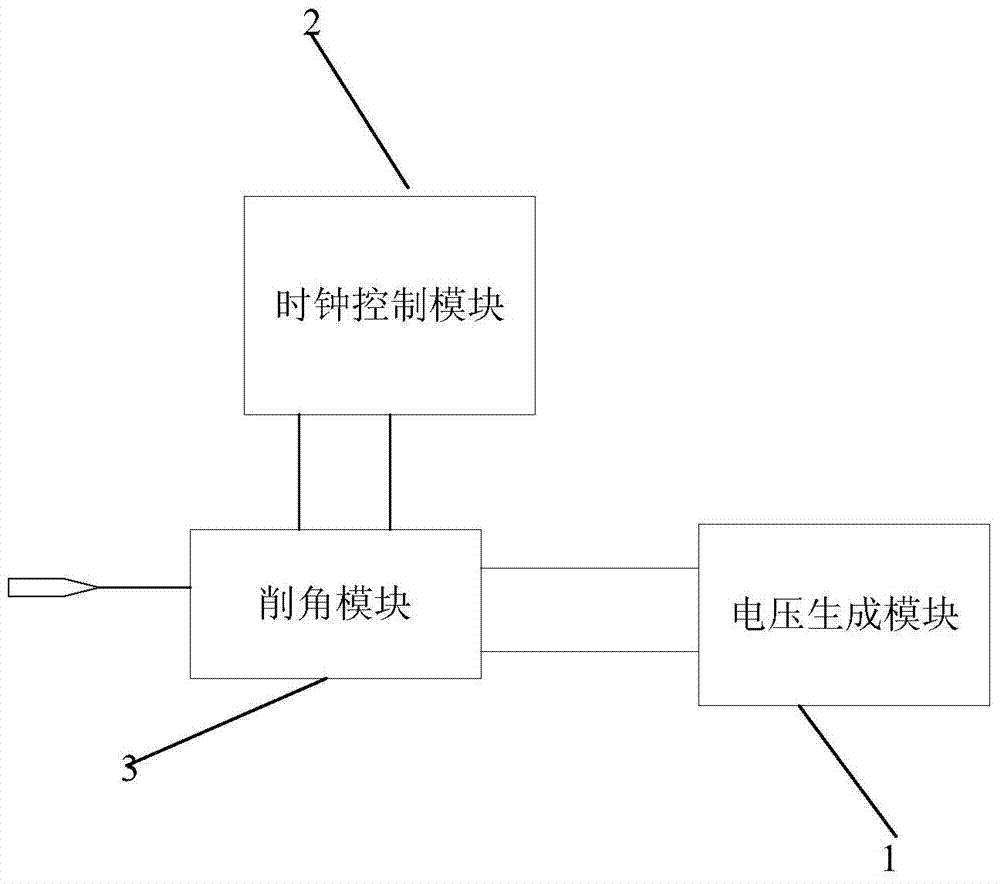

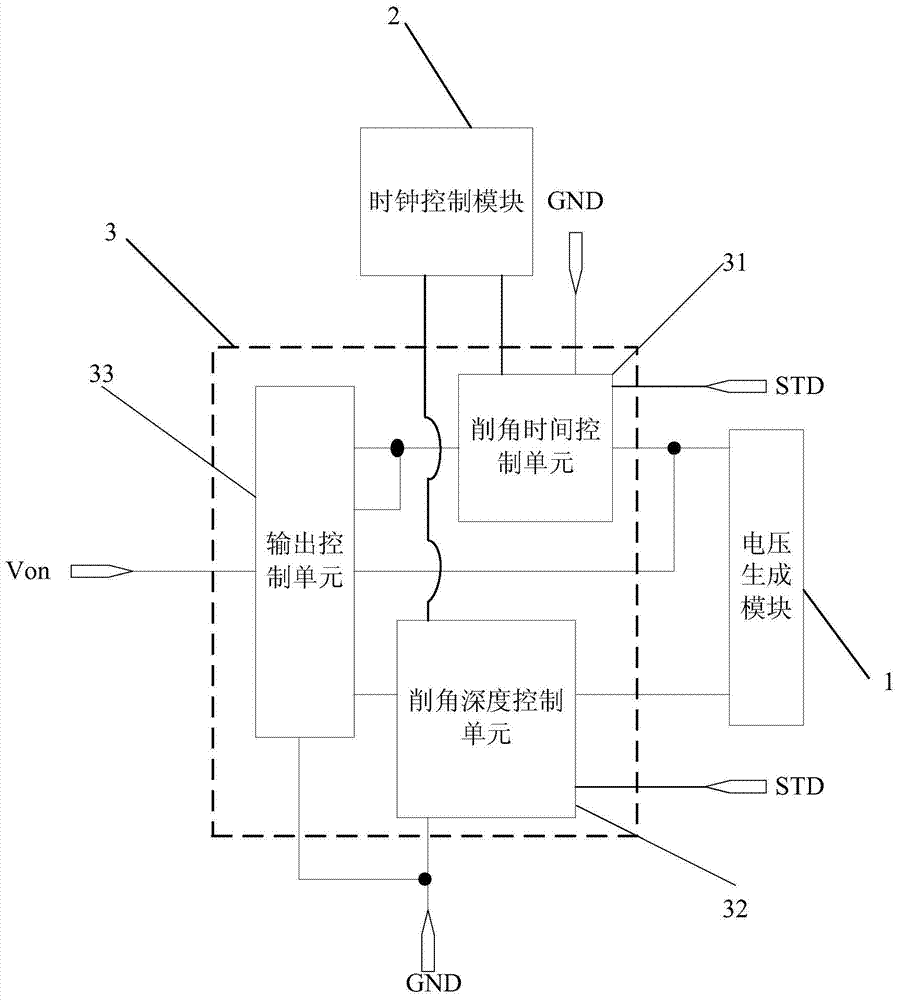

[0050] Specific implementations of the gate turn-on voltage compensation circuit, the display panel, its driving method, and the display device provided by the embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0051] An embodiment of the present invention provides a gate turn-on voltage compensation circuit, such as figure 2 As shown, it may include: a voltage generation module 1, a clock control module 2 and a chamfering module 3; wherein,

[0052] The first voltage output end of the voltage generation module 1 is connected with the first voltage input end of the chamfering module 3, the second voltage output end of the voltage generation module 2 is connected with the second voltage input end of the chamfering module 3, and the voltage generation module 1 For correspondingly outputting the generated first voltage signal and the second voltage signal to the first voltage input terminal and the second voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More