A calibration module and calibration method for clock mismatch error of tiadc system

A system clock and mismatch error technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve the problems of input signal frequency limitation, unsatisfactory calibration effect, high requirements for reference channels, etc., achieve fast calibration speed, good calibration effect, The effect of low computational complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

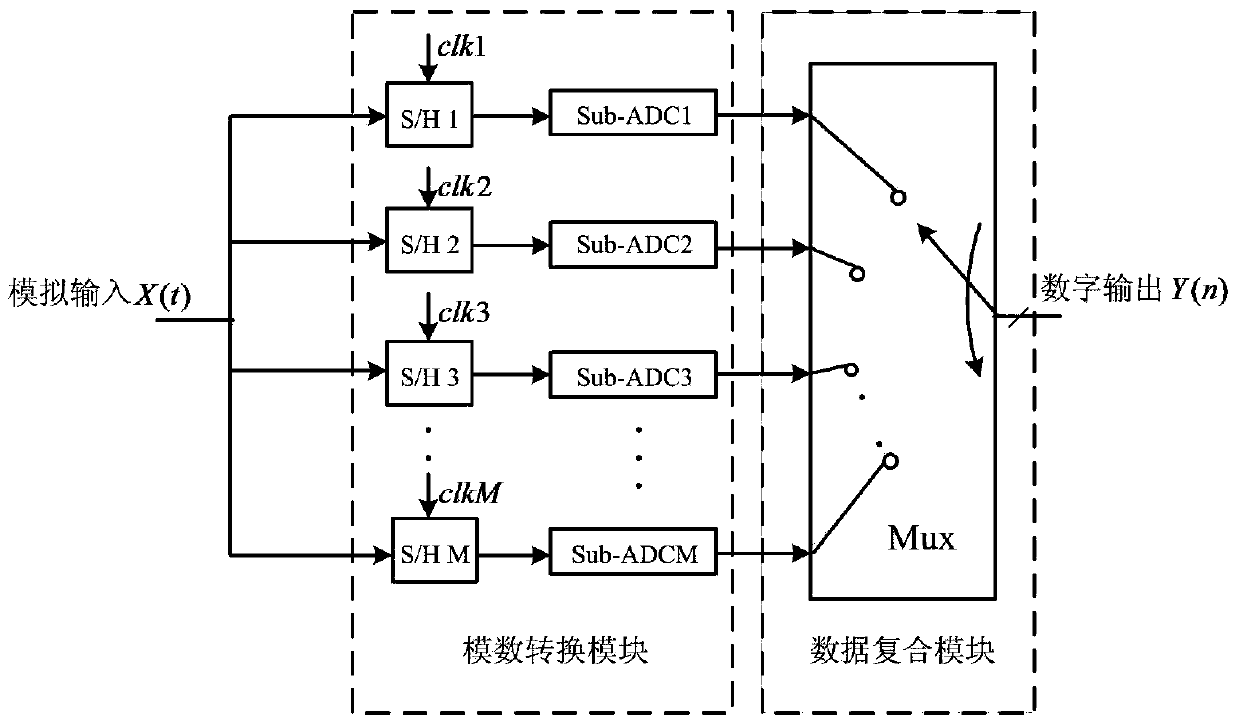

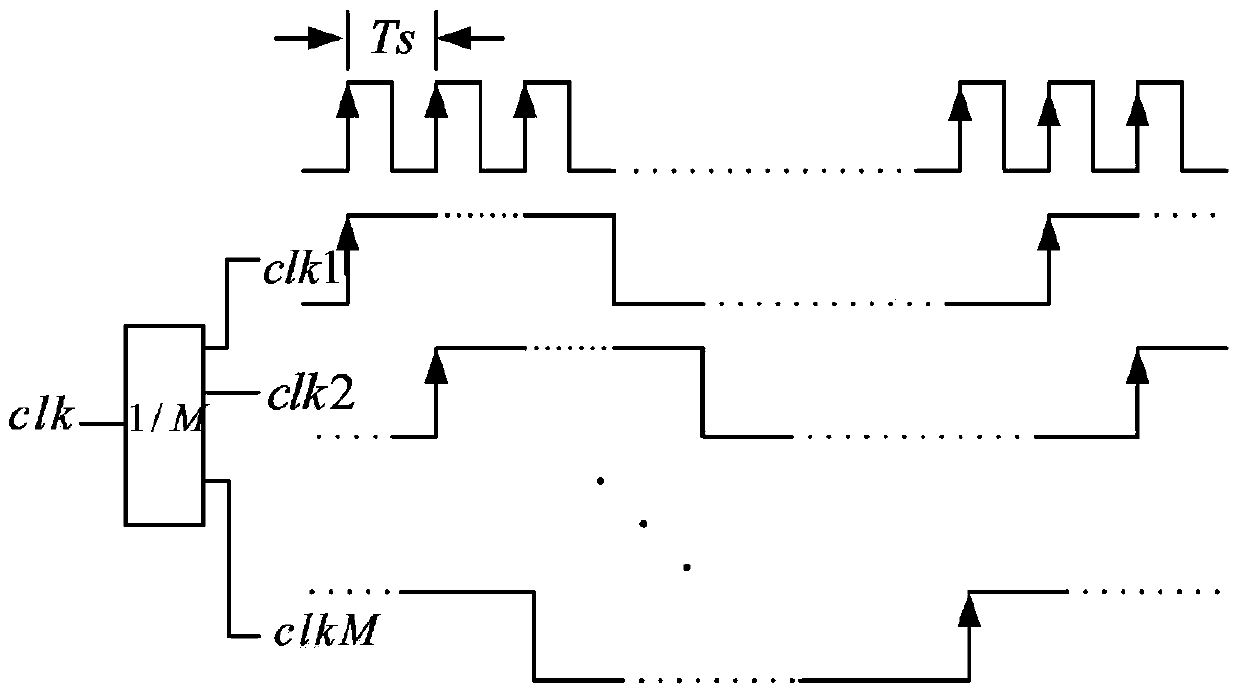

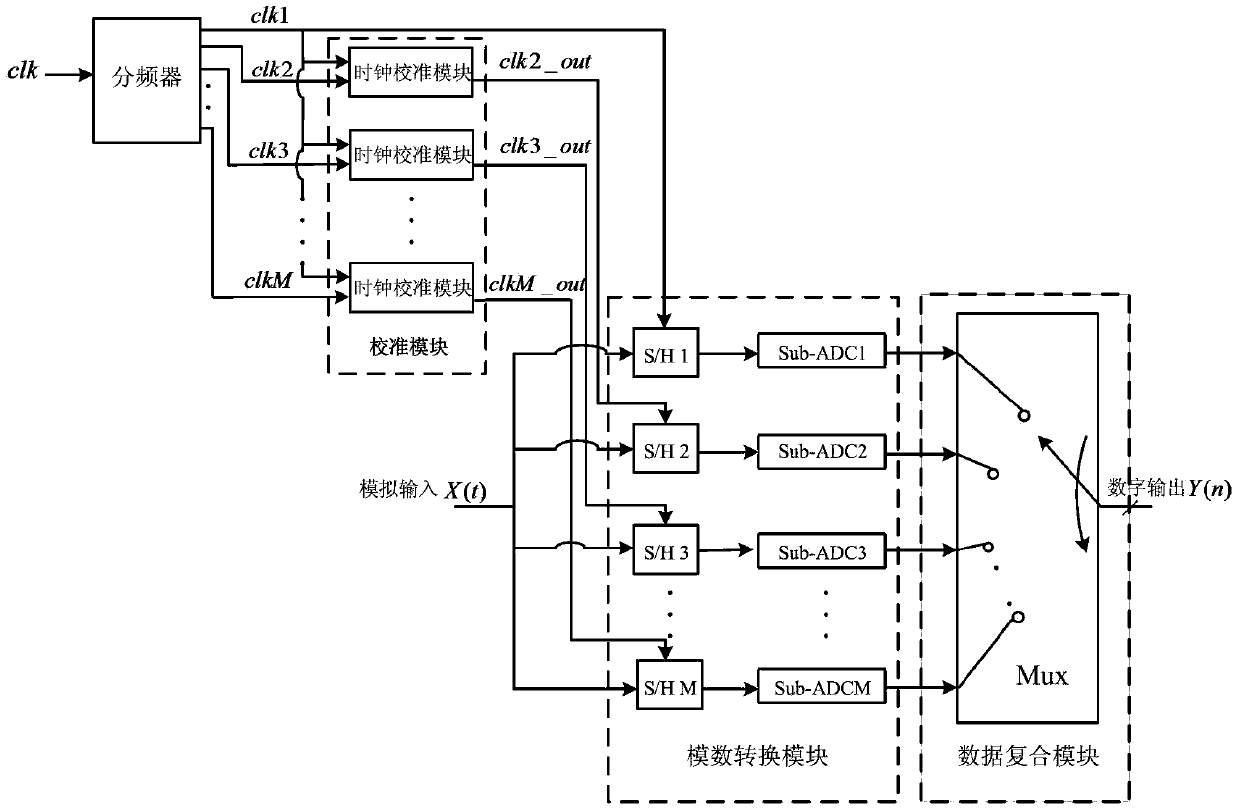

[0093] In this embodiment, a TIADC system in a calibration module for TIADC system clock mismatch error is composed of an analog-to-digital conversion module and a data composite module, such as Figure 1a As shown, wherein, the analog-to-digital conversion module is composed of M sampling and holding circuits and M sub-channel ADCs; the M sampling and holding circuits are respectively controlled by M sampling clock signals; as Figure 1b As shown, M sampling clock signals are obtained by frequency division of the sampling clock clk of the TIADC system through a frequency divider; the sampling clock period of a single sub-channel ADC is M times the sampling clock period of the TIADC system;

[0094] The sampling clock signal clk1 of the first sub-channel ADC is used as the reference clock signal, and the sampling clock signals of the remaining M-1 sub-channel ADCs are calibrated, and the M-1 sampling clock signals except the first sub-channel ADC, that is, in A clock calibratio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More