CTLE value traversal optimization method and device

An optimization method and a technology for optimizing devices, which are applied in the electronic field and can solve problems such as low work efficiency and time-consuming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

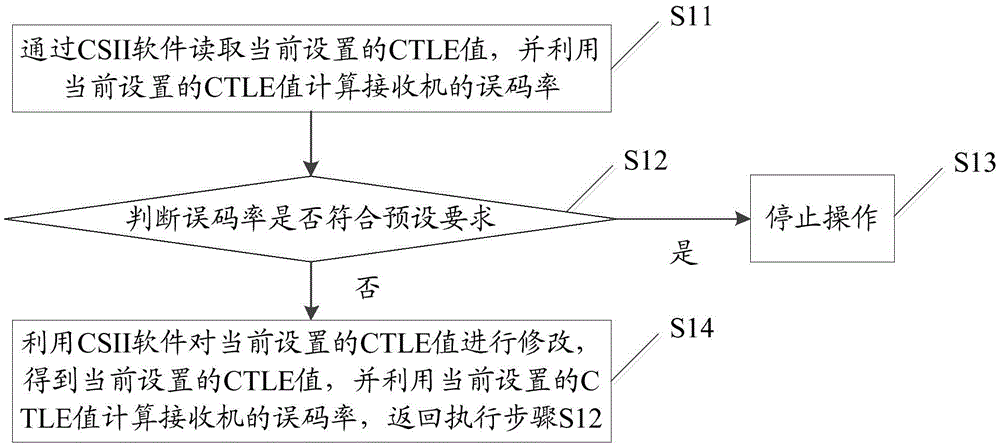

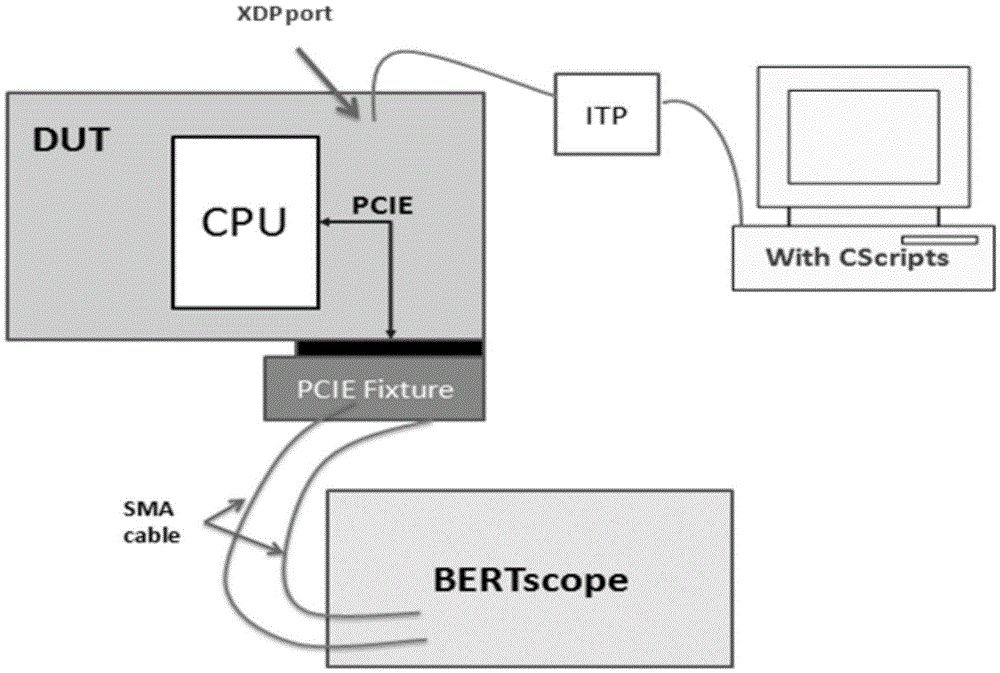

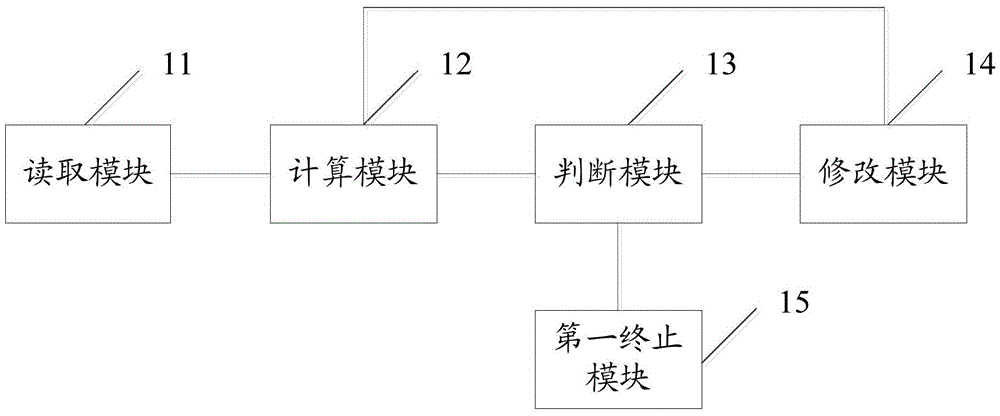

[0034] see figure 1 , which shows a flowchart of a CTLE value traversal optimization method provided by an embodiment of the present invention, the method is implemented based on BERTscope, and the CTLE value traversal optimization method may include the following steps:

[0035] S11: Read the currently set CTLE value through the CSII software, and use the currently set CTLE value to calculate the bit error rate of the receiver.

[0036] Wherein, the CSII sof...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More