Single-event upset-resistant triple-mode redundant D flip-flop with self-correcting error detection

An anti-single-event, three-mode redundancy technology, applied in pulse generation, electrical components, generating electrical pulses, etc., can solve the problem of low resistance to single-event flipping.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

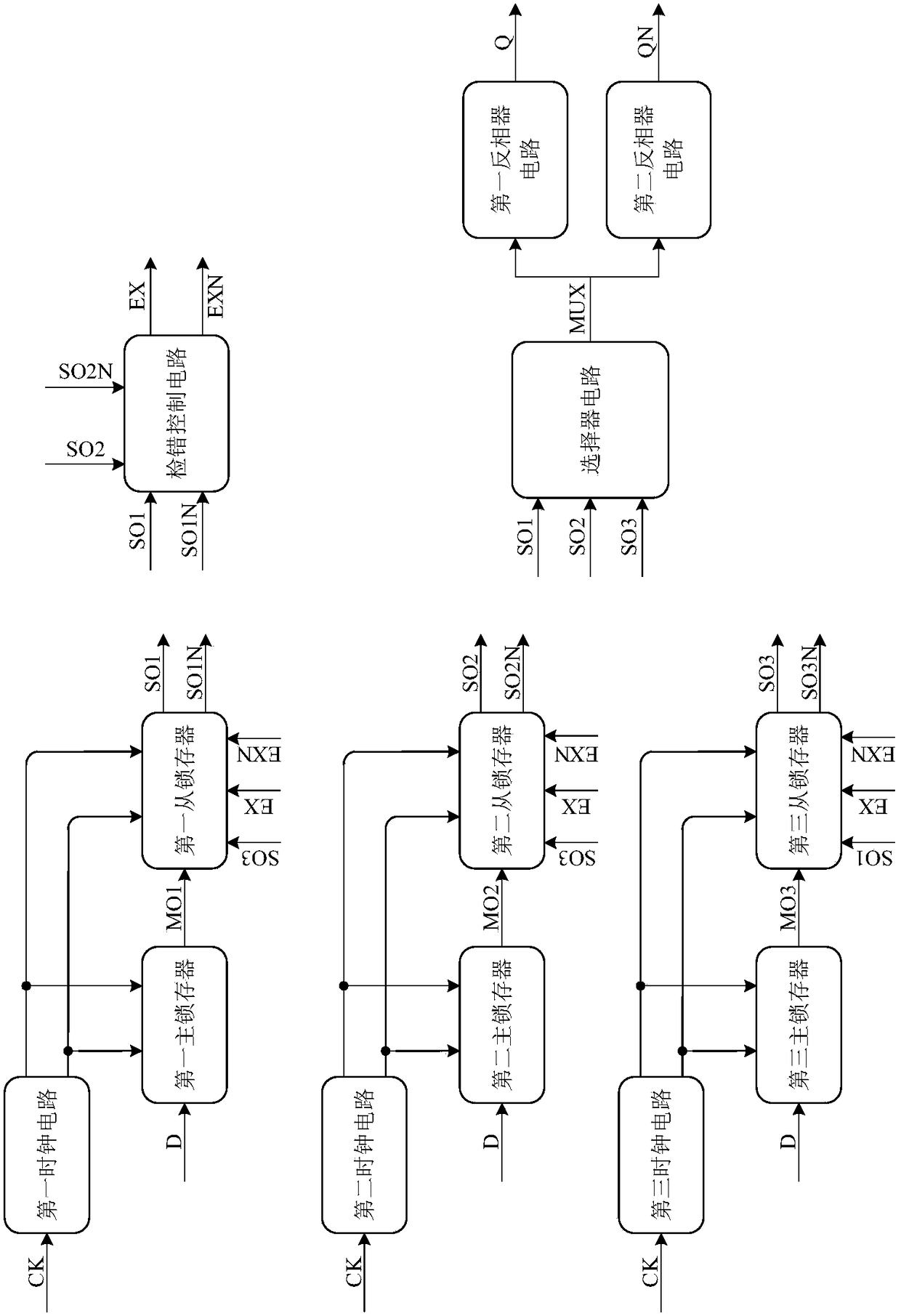

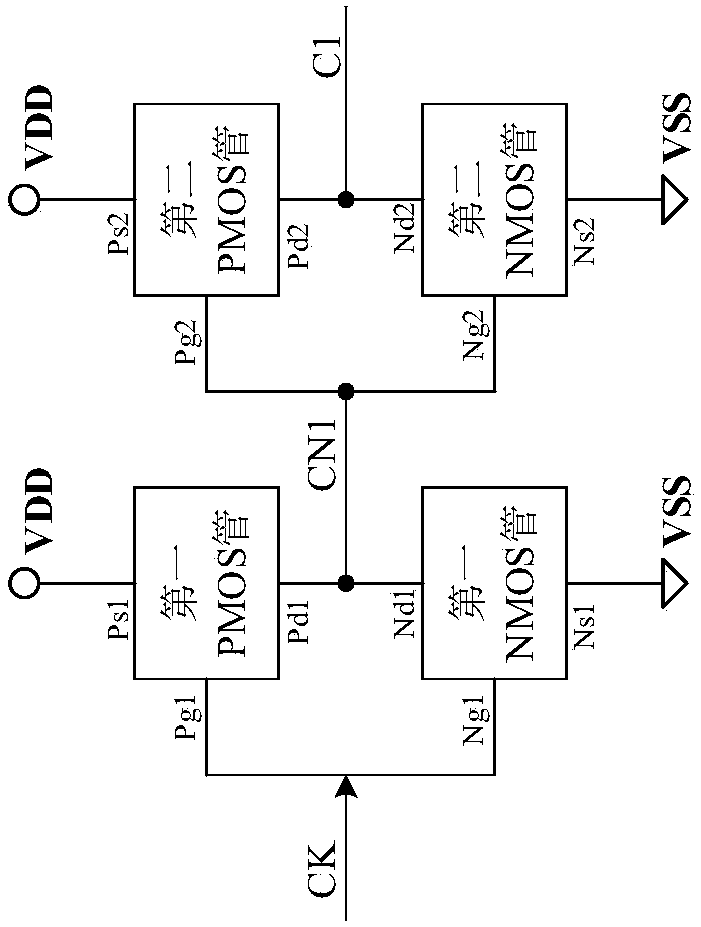

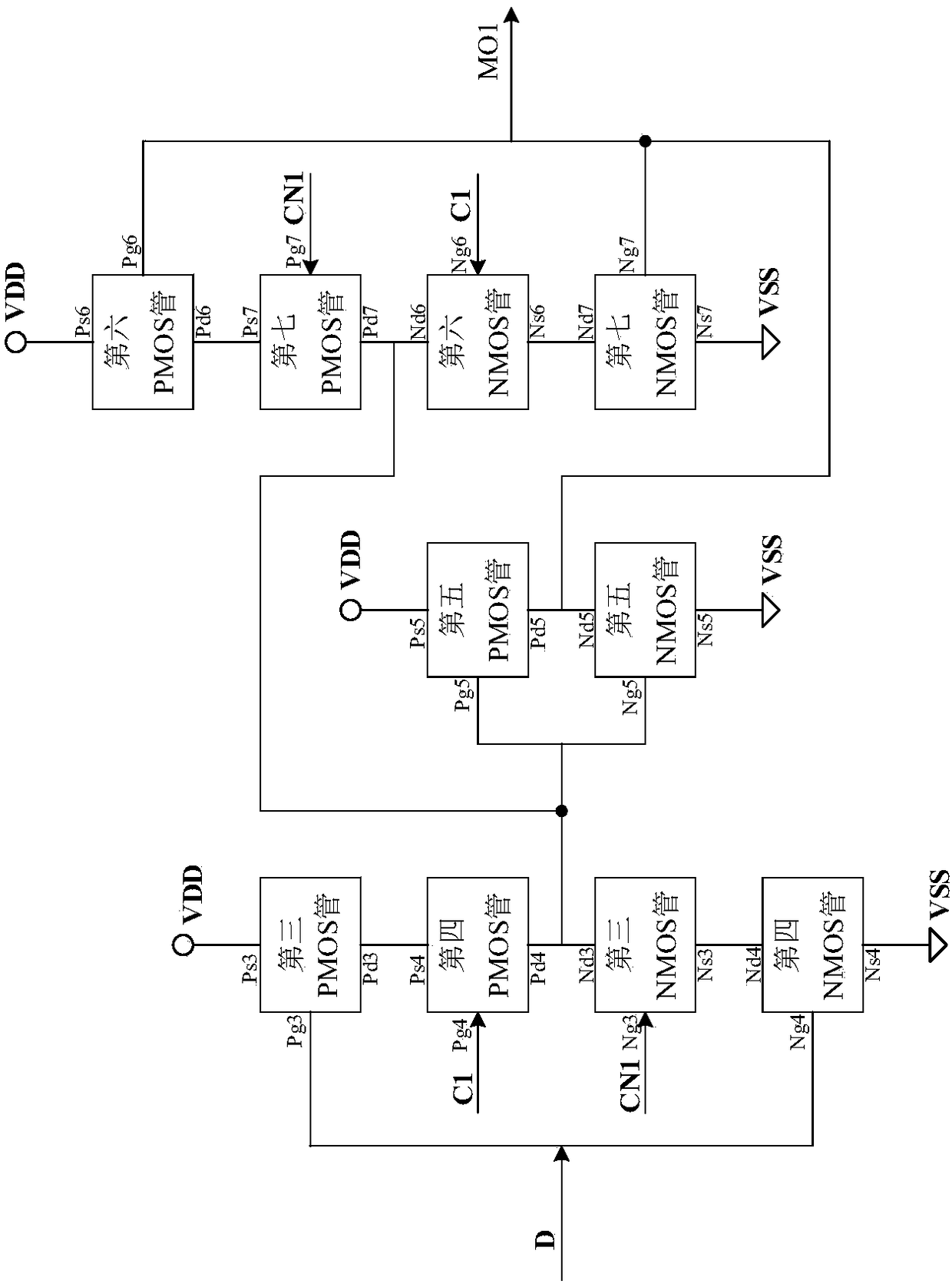

[0057] figure 1 It is a schematic diagram of the logic structure of the anti-single event reversal triple-mode redundant D flip-flop with self-correction and error detection in the present invention. The present invention consists of the first clock circuit (such as figure 2 shown), the first master latch (as image 3 shown), the first slave latch (as Figure 4 shown); the second clock circuit (such as Figure 5 shown), the second master latch (as Figure 6 shown), the second slave latch (as Figure 7 shown); the third clock circuit (such as Figure 8 shown), the third master latch (as Figure 9 shown), the third slave latch (as Figure 10 shown); selector circuit (such as Figure 11 shown), the first inverter circuit (such as Figure 12 shown), the second inverter circuit (such as Figure 13 shown); and error detection control circuit (such as Figure 14 shown) composition.

[0058] The anti-single-event reversal triple-mode redundant D flip-flop with self-correc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More