Method for reducing dynamic power dissipation and electronic device

A technology of dynamic power consumption and electronic equipment, applied in the direction of reducing energy consumption, electrical components, data processing power supply, etc., can solve the problems of large logic circuit optimization gating, the gating effect is not obvious, and the power consumption saving benefit is not obvious. , to avoid extra burden and reduce dynamic power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

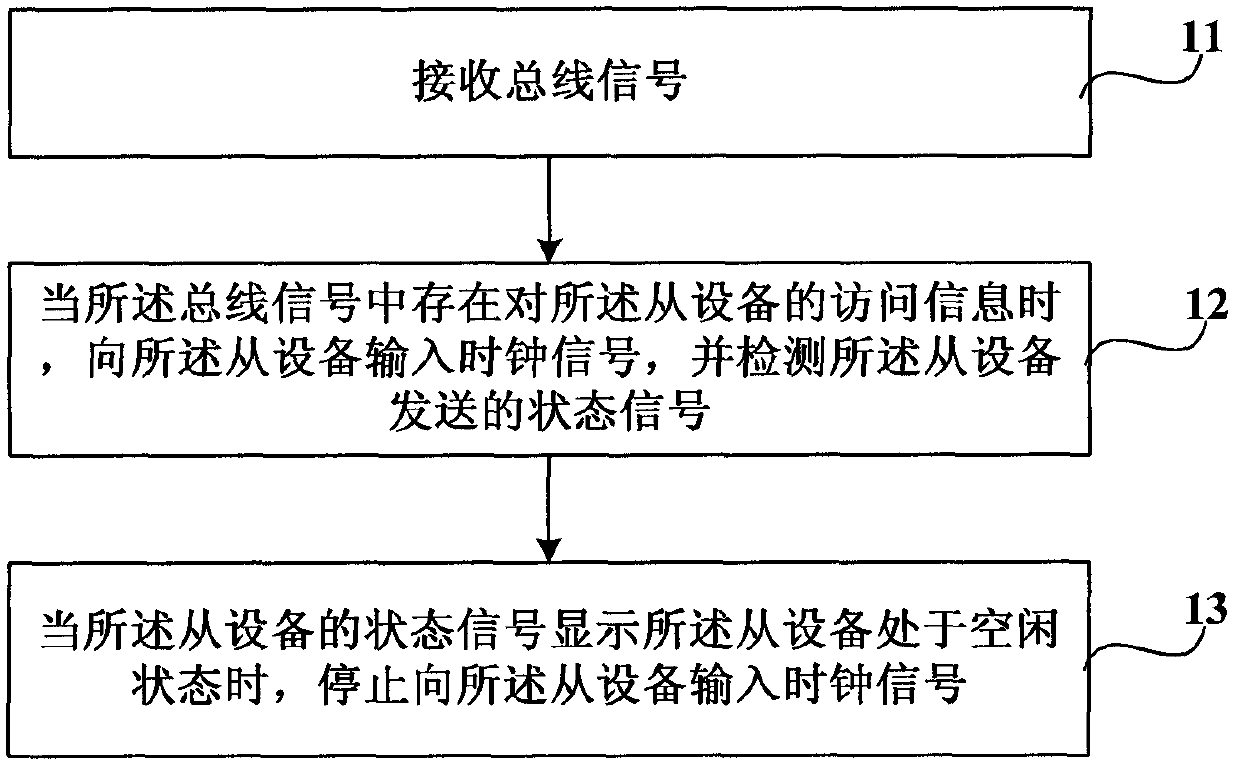

[0028] figure 1 It is a flowchart of a method for reducing dynamic power consumption provided by an embodiment of the present invention. Such as figure 1 As shown, methods to reduce dynamic power consumption include:

[0029] Step 11, receiving the bus signal.

[0030] Among them, the bus signal (bus-signal) is a general term for a combination of multiple bus signals, including HADDR[31:0] and HTRANS[1] of the AMBA2.0 bus, using HADDR[31:0] and HTRANS[1] signals...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More