Low power consumption static random memory with low level thread amplitude of oscillation

A technology of static random access and memory, applied in static memory, digital memory information, information storage, etc., can solve the problem of high dynamic power consumption of bit lines, and achieve the effect of reducing dynamic power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

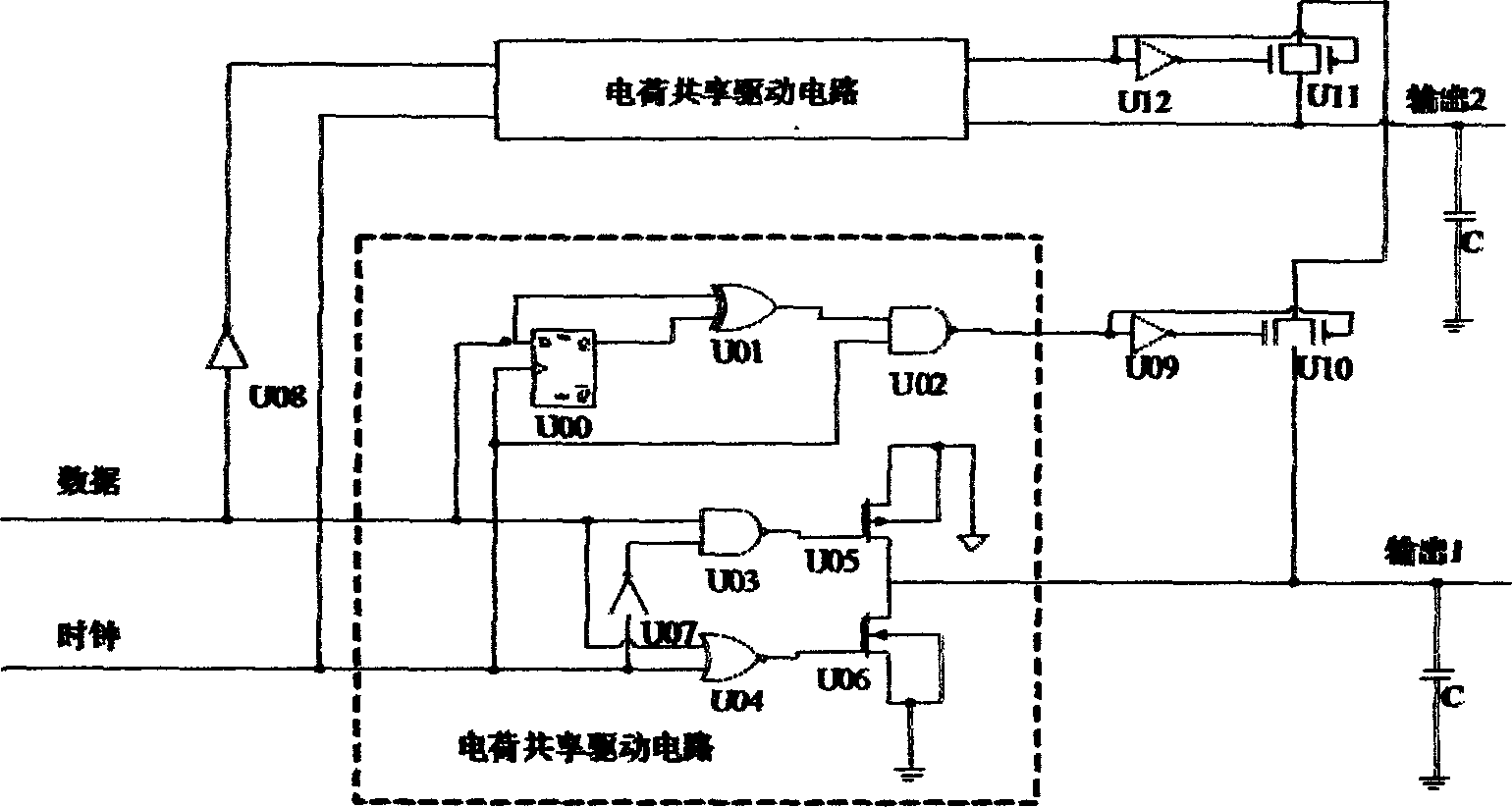

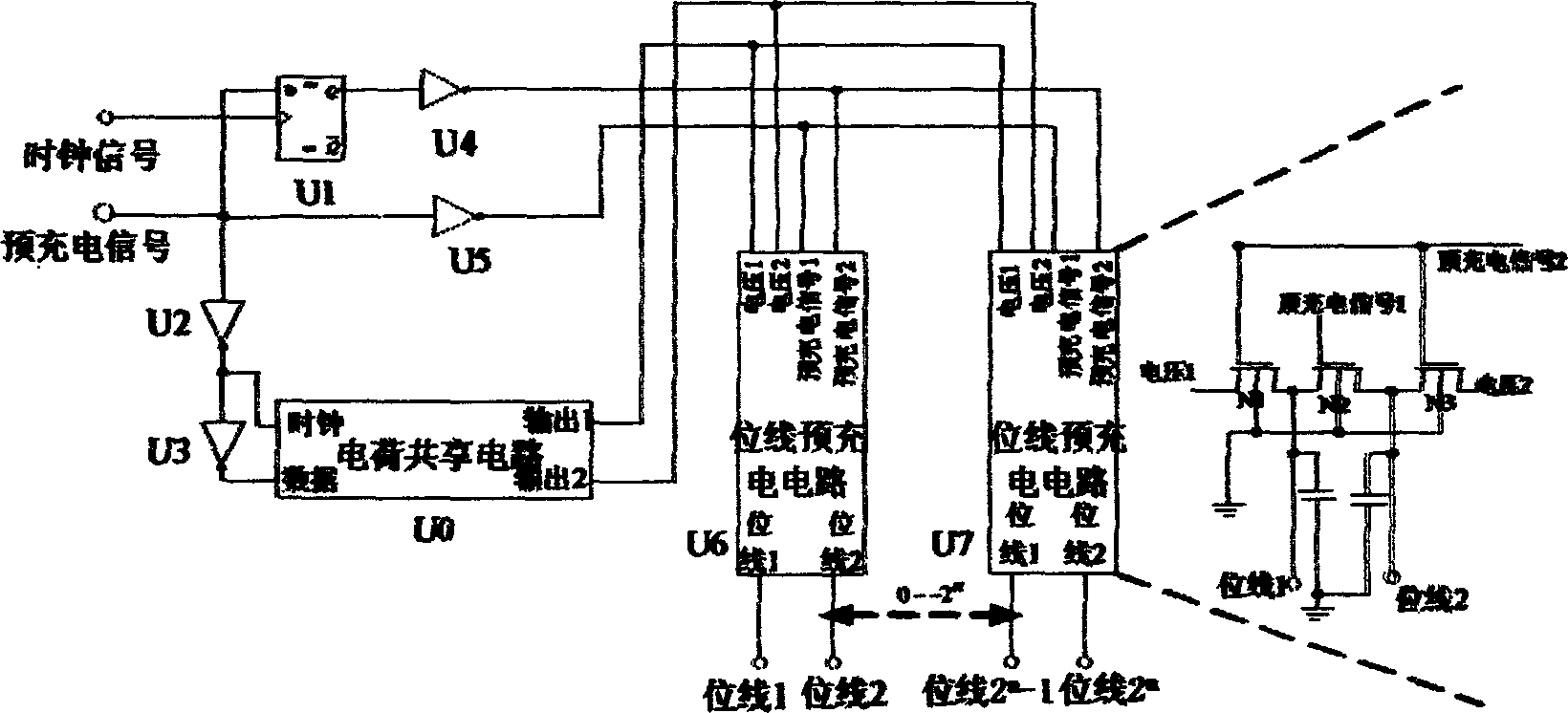

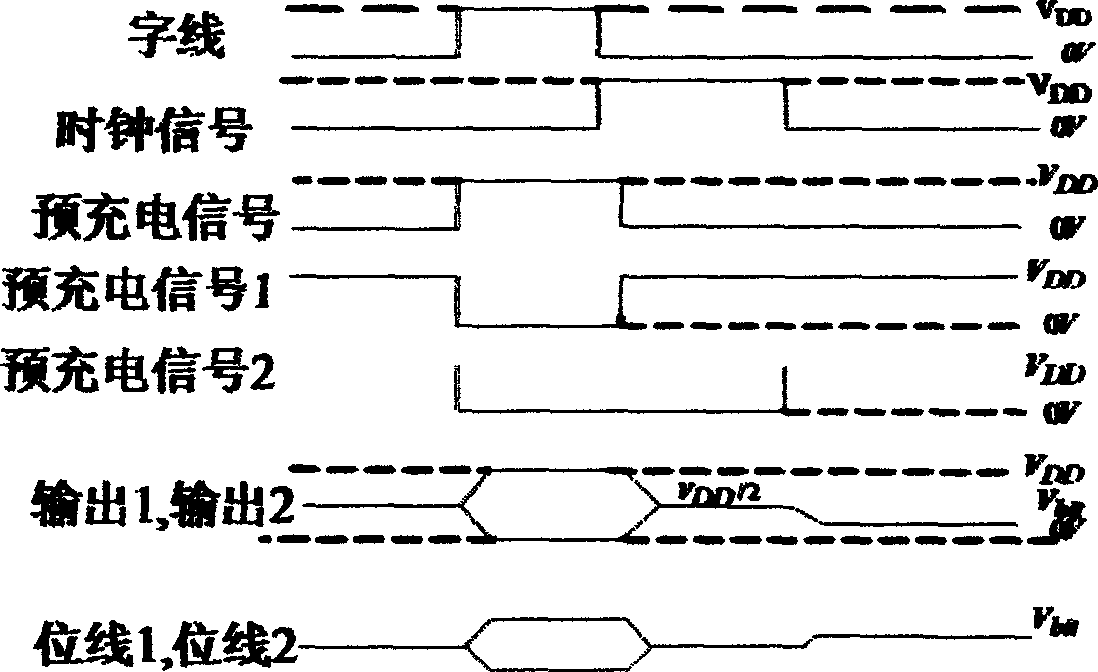

[0035] The low-power SRAM with low bit line swing of the present invention comprises a precharge circuit 1 based on charge sharing, a storage body unit 2, a row decoder 3, a column decoder 4, a selector 5, a read-write control circuit 6, a sensitive Amplifier 7, input processing circuit 8; Wherein, the "bit line" end based on the charge-sharing precharge circuit 1 is respectively connected to the "bidirectional port" of the selector 5, and the row decoder 3 is connected to the "word line". Two adjacent "bit lines" are respectively connected with a memory cell 2, and the "word line" of the memory cell 2 is connected to the "word line"; "Enable signal" end; the input terminal of the read-write control circuit 6 is connected to the read-write signal, the "amplifier enable signal" in the output end is connected to the sensitive amplifier 7, and the "write enable signal" in the output end is connected to the input processing circuit 8; The output terminals of the processing circuit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More