An Accurate Timing Analysis Method of Block Carry Chain

A technology of timing analysis and carry chain, which is applied in the direction of instrumentation, computing, electrical digital data processing, etc., and can solve the problem of not finding timing analysis, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

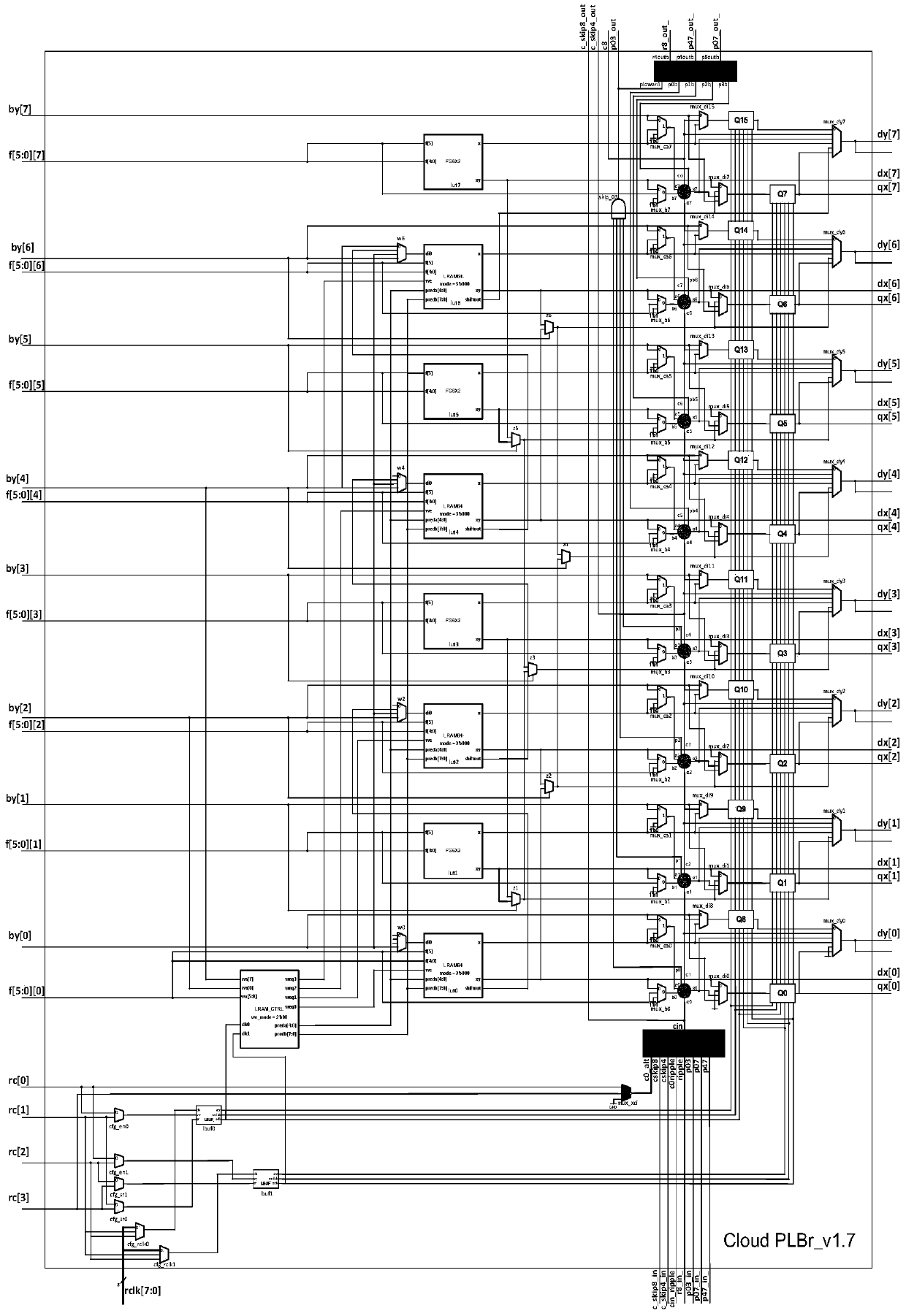

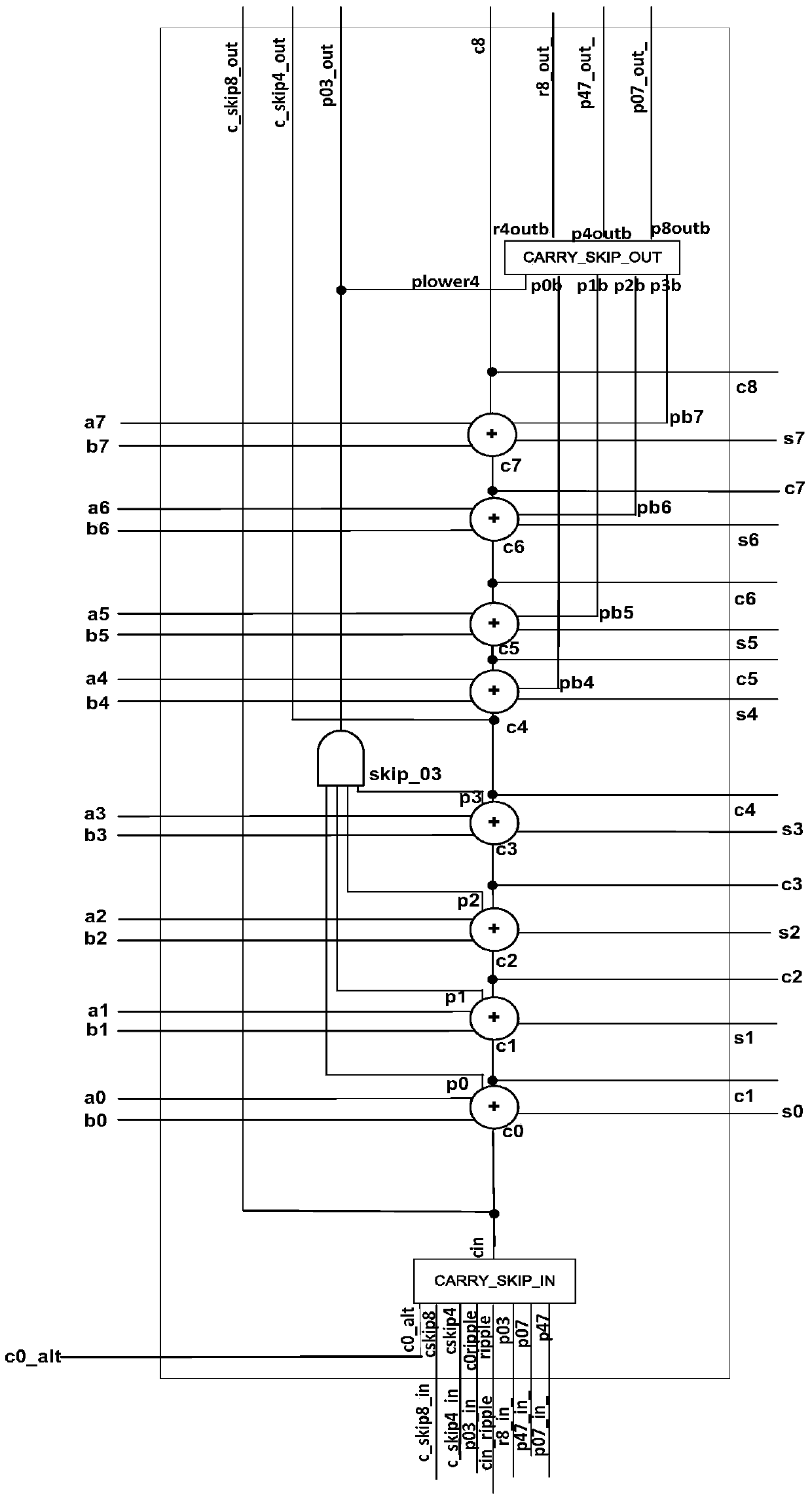

[0021] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments.

[0022] In the embodiment of the present invention, when performing timing analysis, the entire carry chain and jump logic in a PLB are analyzed as a whole, accurate and complete timing information can be obtained, and the correct optimization direction can be pointed out to the timing driver router.

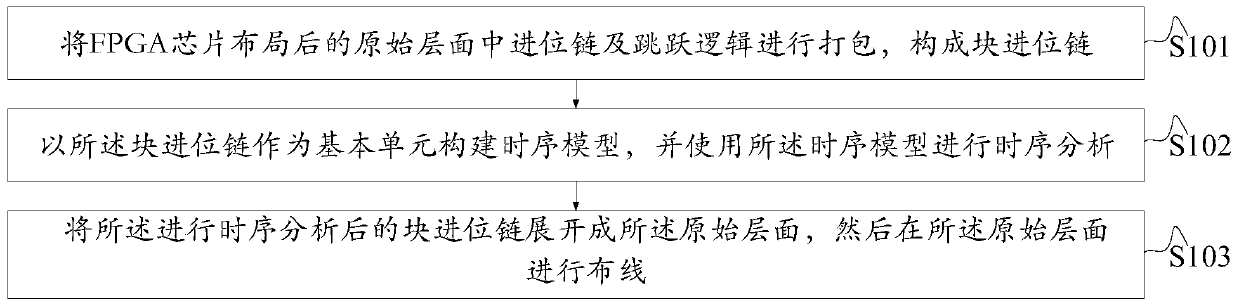

[0023] figure 1 It is a schematic flowchart of an accurate timing analysis method for a block carry chain provided by an embodiment of the present invention. Such as figure 1 As shown, an accurate timing analysis method of a block carry chain include...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More