Array substrate, preparation method thereof and display panel

A technology for array substrates and display panels, which is applied in the fields of semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, instruments, etc., and can solve the problems that the related processes of array substrates need to be improved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0085] The embodiments of the present invention are described in detail below, and those skilled in the art will understand that the following embodiments are intended to explain the present invention, and should not be regarded as limiting the present invention. Unless otherwise specified, in the following examples that do not explicitly describe specific techniques or conditions, those skilled in the art can carry out according to commonly used techniques or conditions in this field or according to product instructions. The reagents or instruments used were not indicated by the manufacturer, and they were all commercially available conventional products.

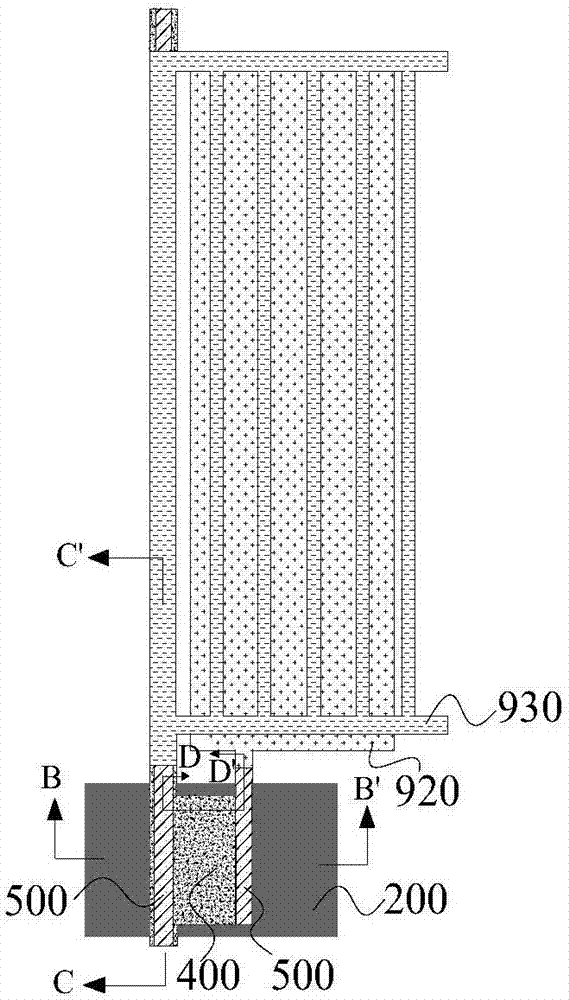

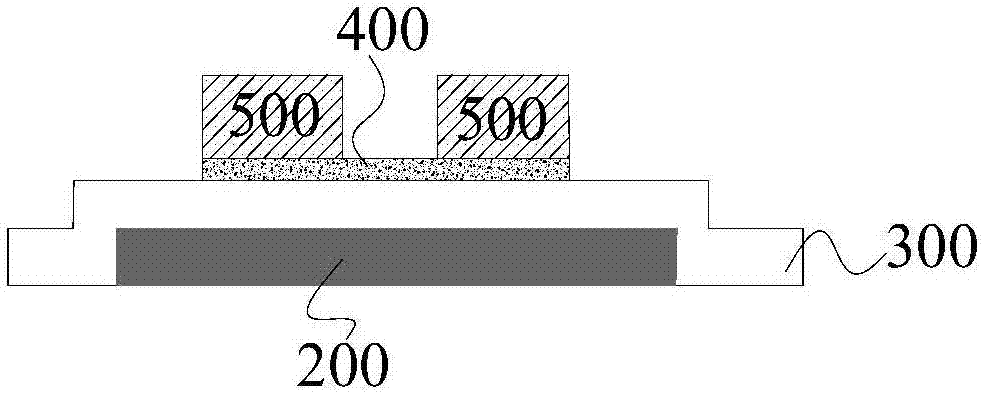

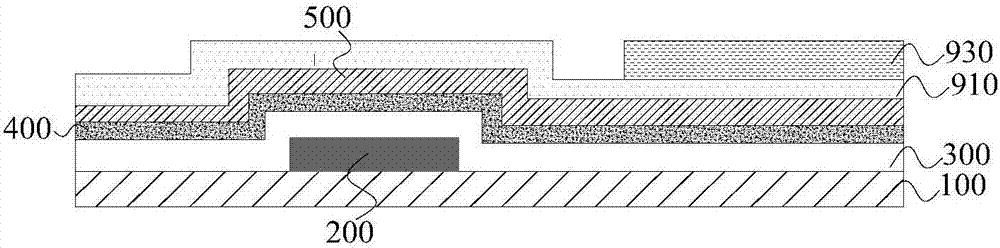

[0086] In one aspect of the present invention, the present invention provides an array substrate. refer to Figure 3a-8d , to describe the array substrate of the present invention in detail.

[0087] According to an embodiment of the present invention, the array substrate includes: a base substrate 100, a thin film trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More