PCB inner layer pattern optimization method, PCB, board splicing structure and laminating structure

A technology of inner layer pattern and optimization method, applied in the field of electronics, can solve the problems of copper foil wrinkling and lack of glue, and achieve the effect of improving pressure loss and improving the uniformity of glue flow.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods. It should be understood that the specific embodiments described here are only used to explain the present invention, and do not limit the protection scope of the present invention.

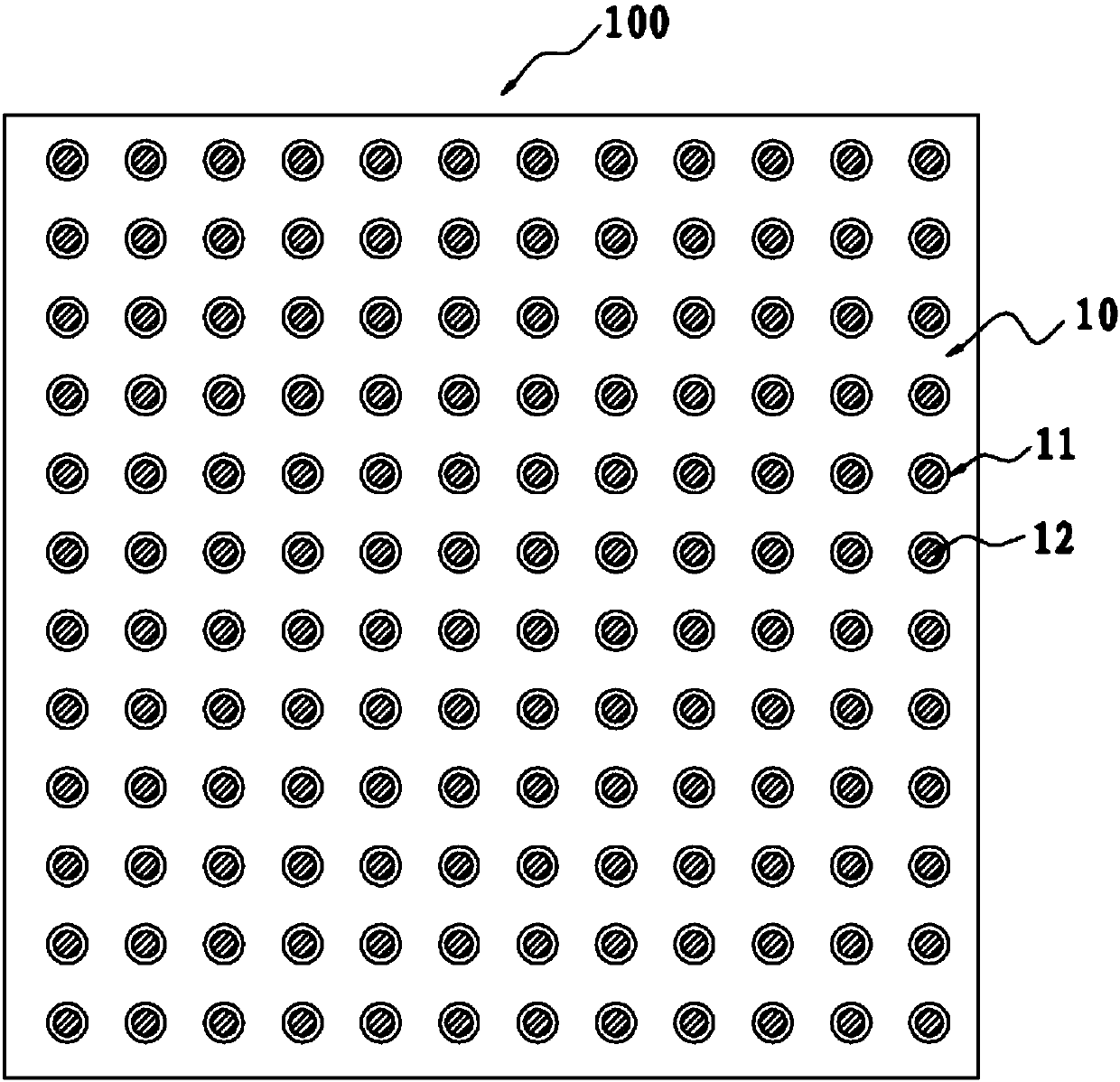

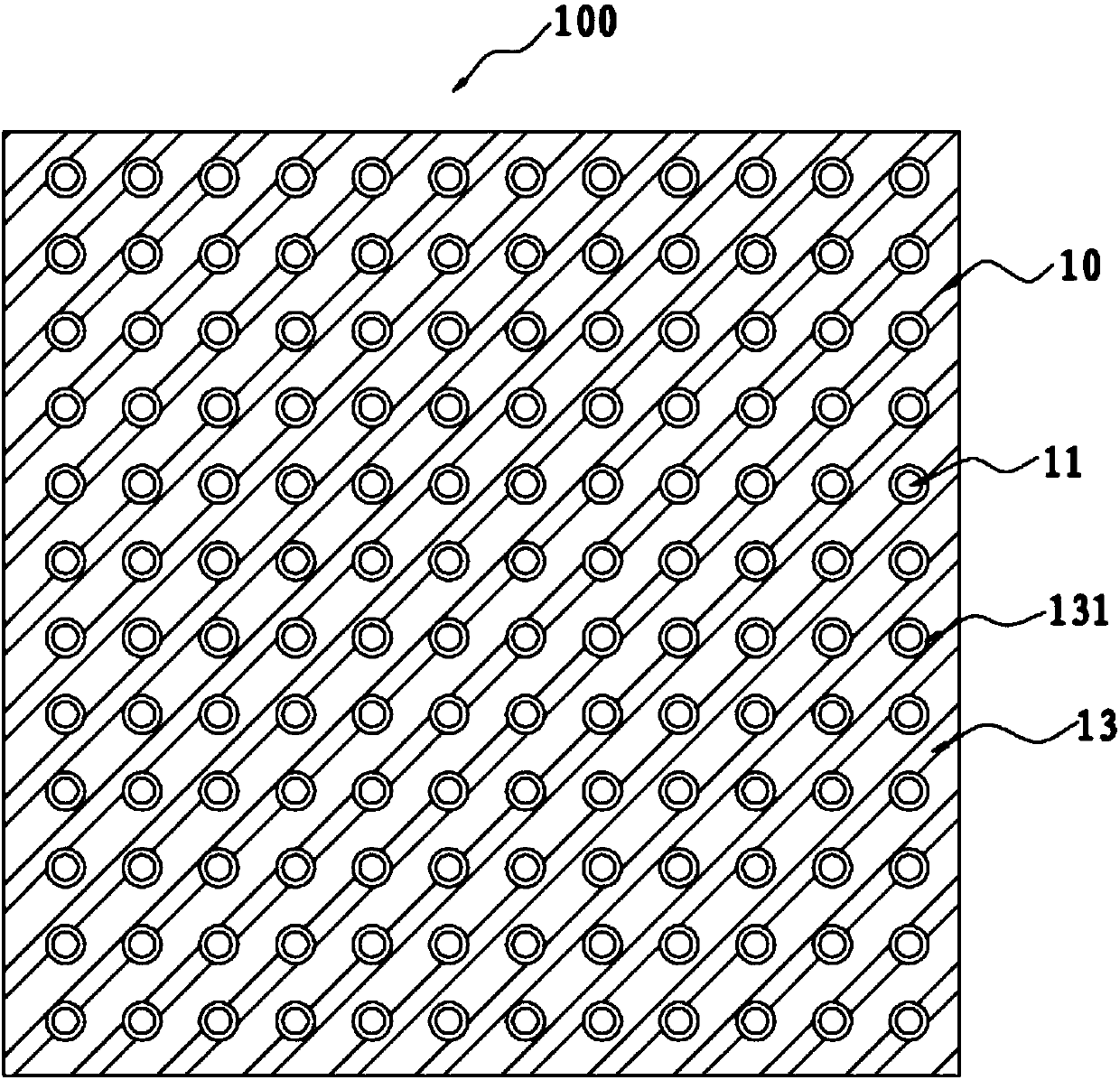

[0033] Such as figure 1 The optimization method of a kind of PCB inner layer pattern shown, PCB inner layer pattern includes copper area 600 and copper-free area 100, and described copper-free area 100 includes the via area 10 that is provided with at least one via hole 11, when there is When the remaining copper ratio of the copper area is less than a specific value, a copper point 12 is arranged at the via hole position of the via hole 11 , and the diameter of the copper point 12 is smaller than the diameter of the via hole.

[0034] Since there is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More