GOA circuit

A circuit and low-potential technology, applied to static indicators, instruments, etc., can solve problems such as grid failure, potential pull-down, and residual image in the effective display area, so as to improve user experience and eliminate residual image.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

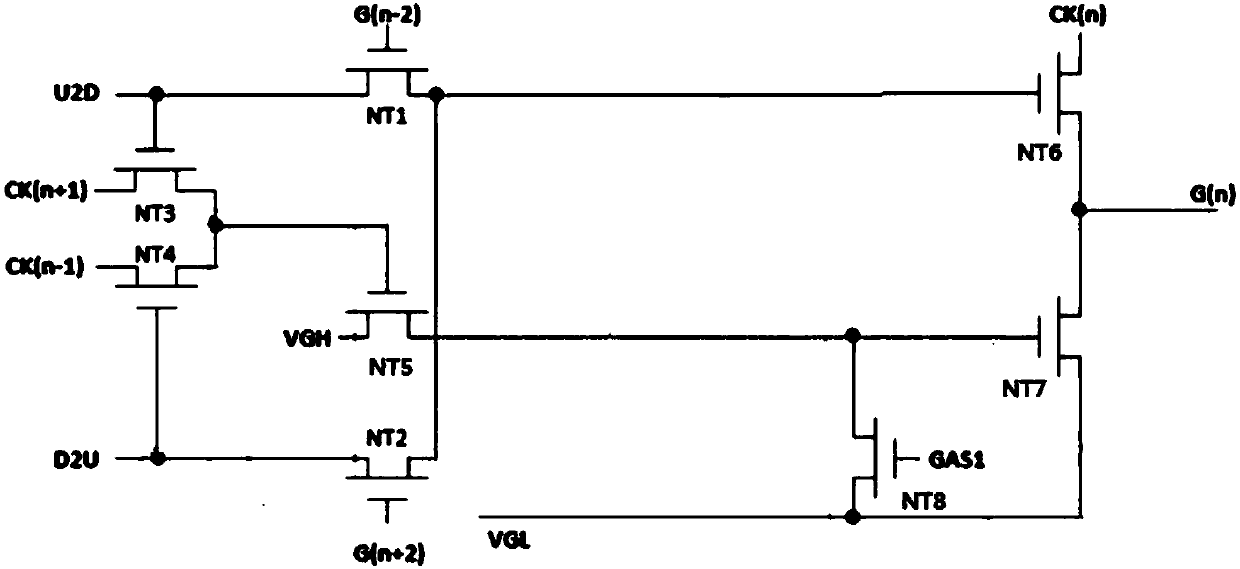

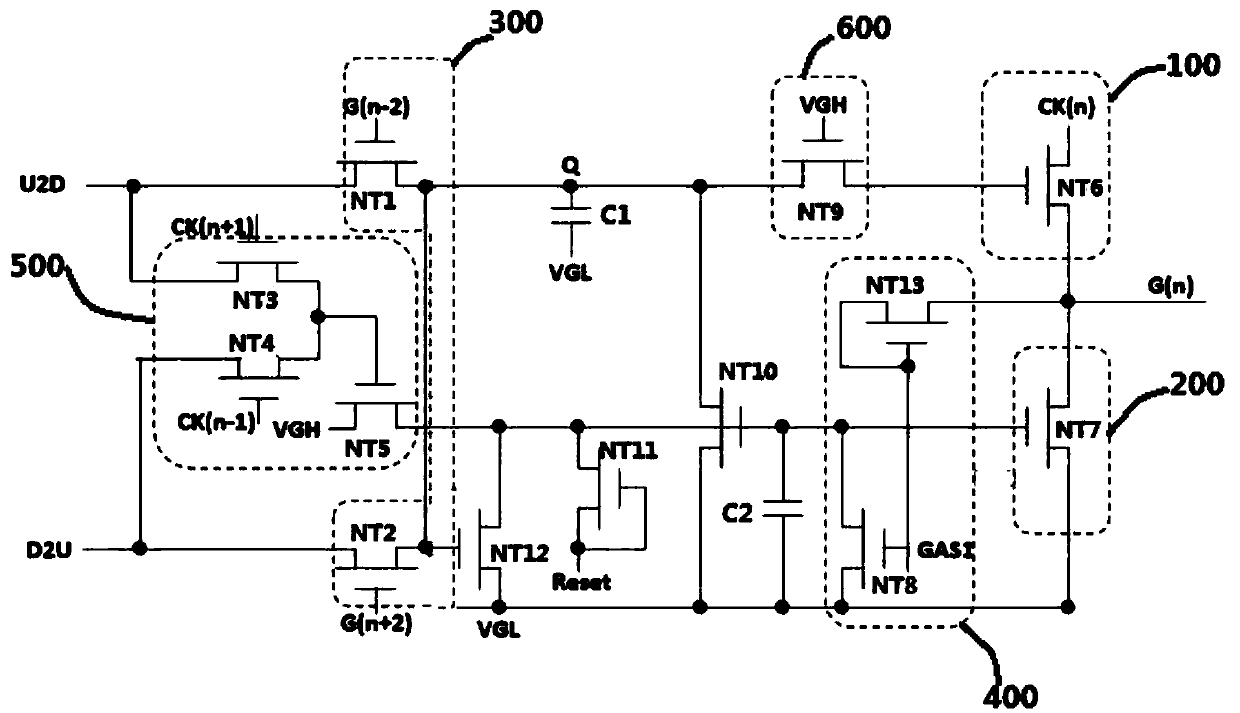

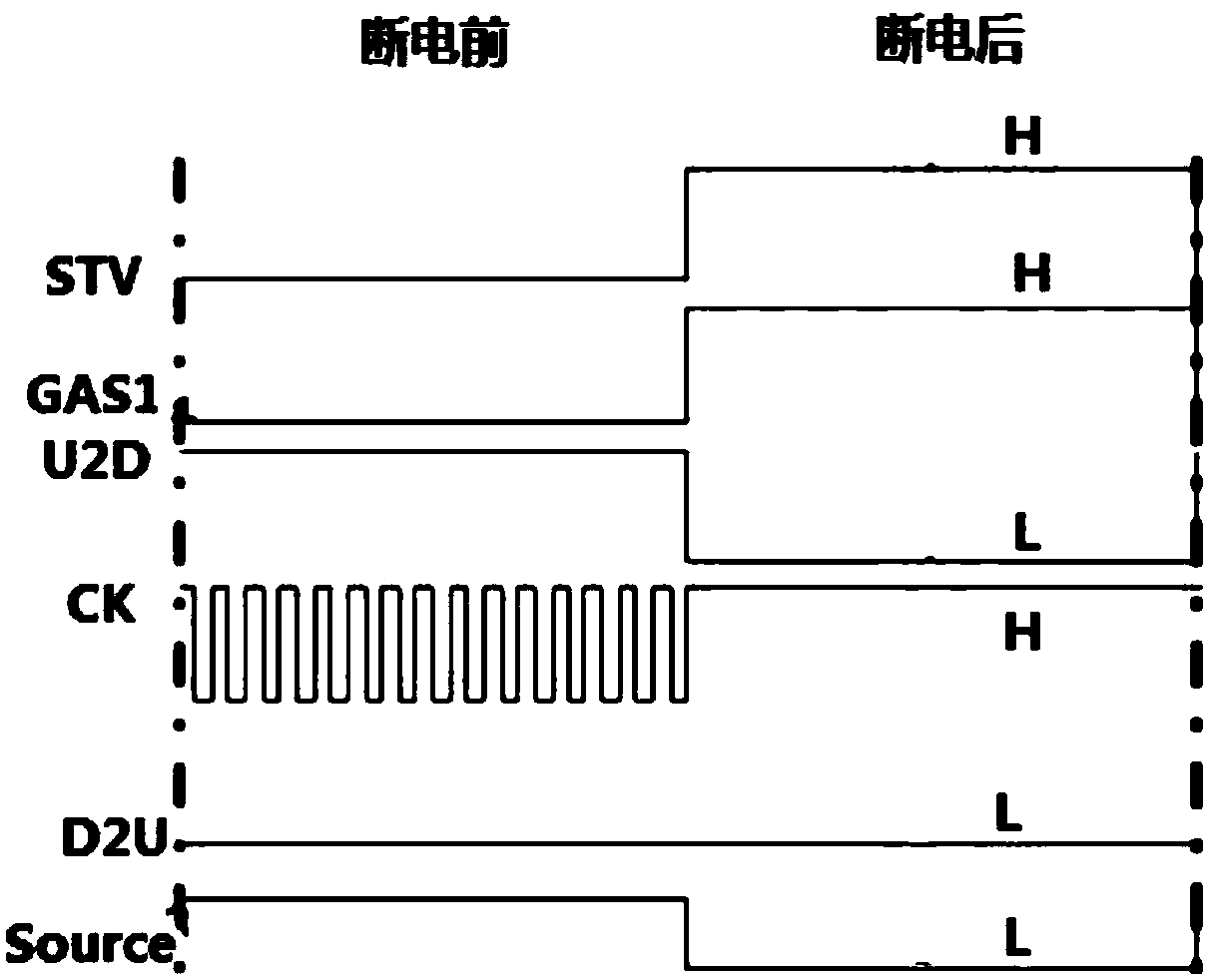

[0043] The present invention provides a GOA circuit, which is used in a liquid crystal display panel, and the GOA circuit includes m cascaded GOA units, such as figure 2 As shown, the nth level GOA unit includes: an output control module 100 , a forward and reverse scan control module 300 , a first pull-down circuit 200 , a second pull-down circuit 500 , and a pull-up circuit 400 , where m≥n≥1.

[0044] The forward and reverse scan control module 300 is used to control the GOA circuit to perform forward scan or reverse scan according to the forward scan control signal U2D or the reverse scan control signal D2U.

[0045] The output control module 100 is connected to the forward and reverse scan control module 300 , and is used to control the output of the nth-level gate drive signal G(n) during the forward scan or reverse scan period of the GOA circuit.

[0046] The first pull-down circuit 200 includes a seventh thin film transistor NT7, the first end of the seventh thin film ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More