Patents

Literature

93results about How to "Eliminate afterimage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

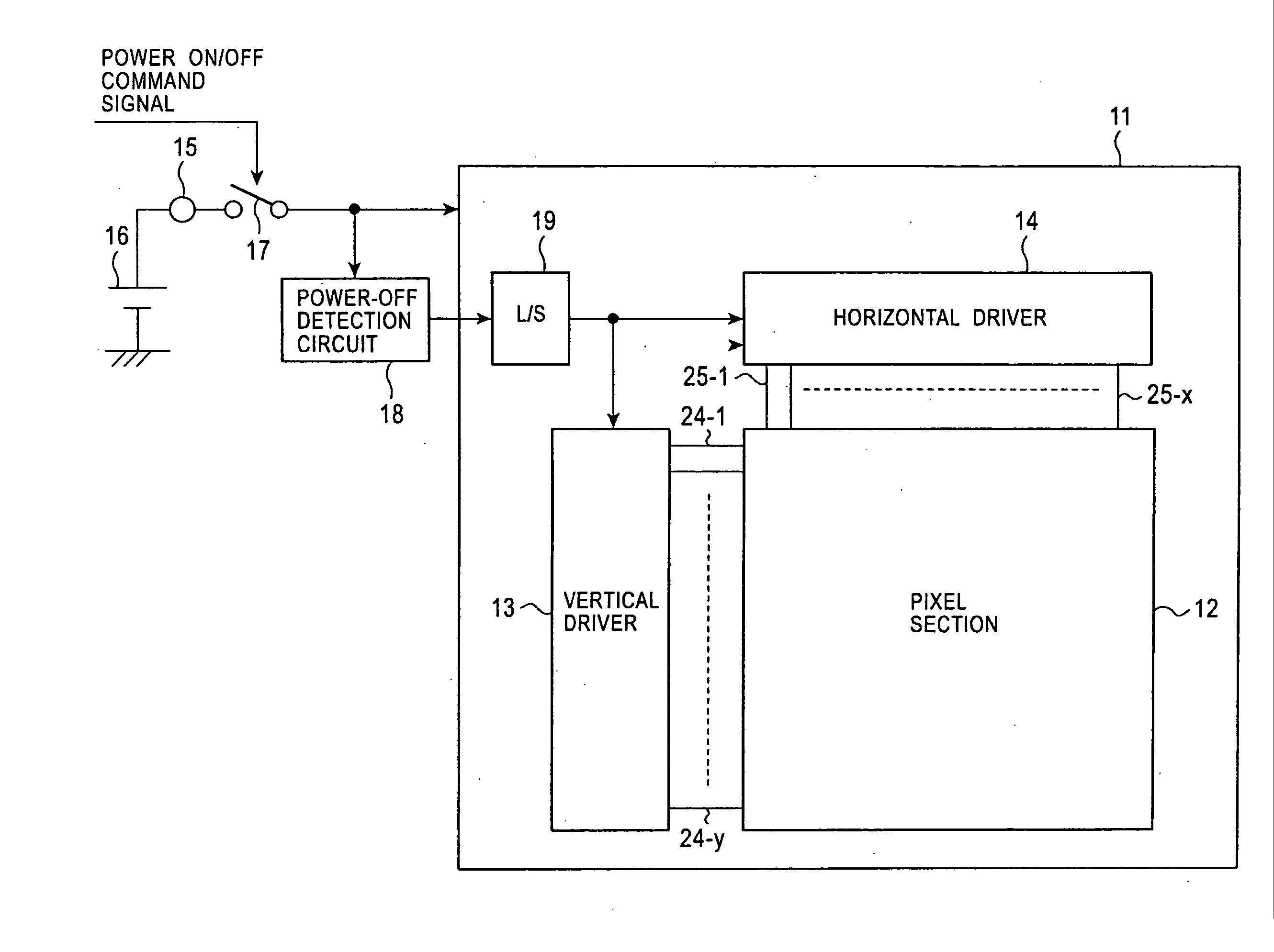

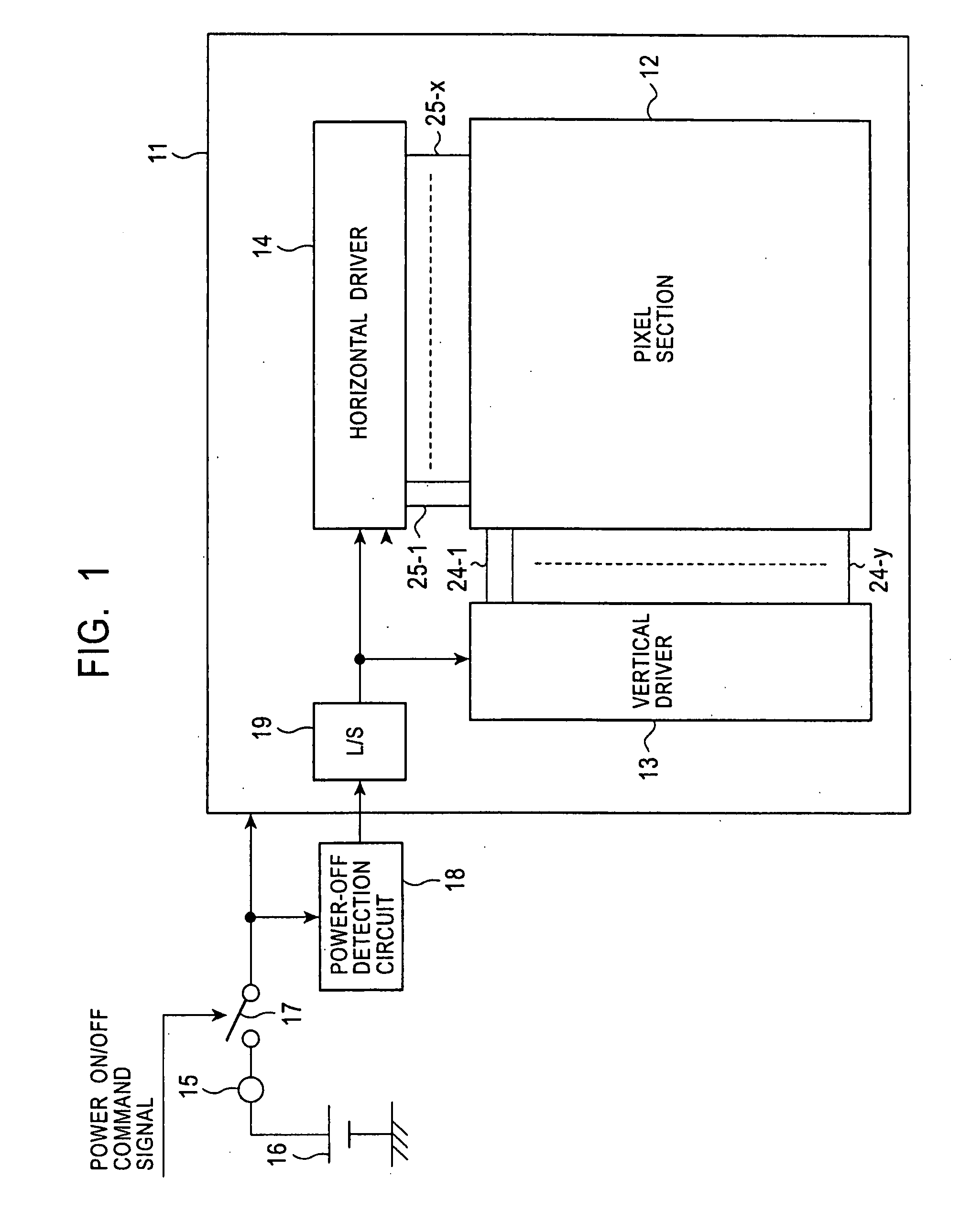

Liquid crystal display device, method for controlling the same, and portable terminal

InactiveUS7271801B2Avoid distortionEliminate afterimageCathode-ray tube indicatorsInput/output processes for data processingActive-matrix liquid-crystal displayLiquid-crystal display

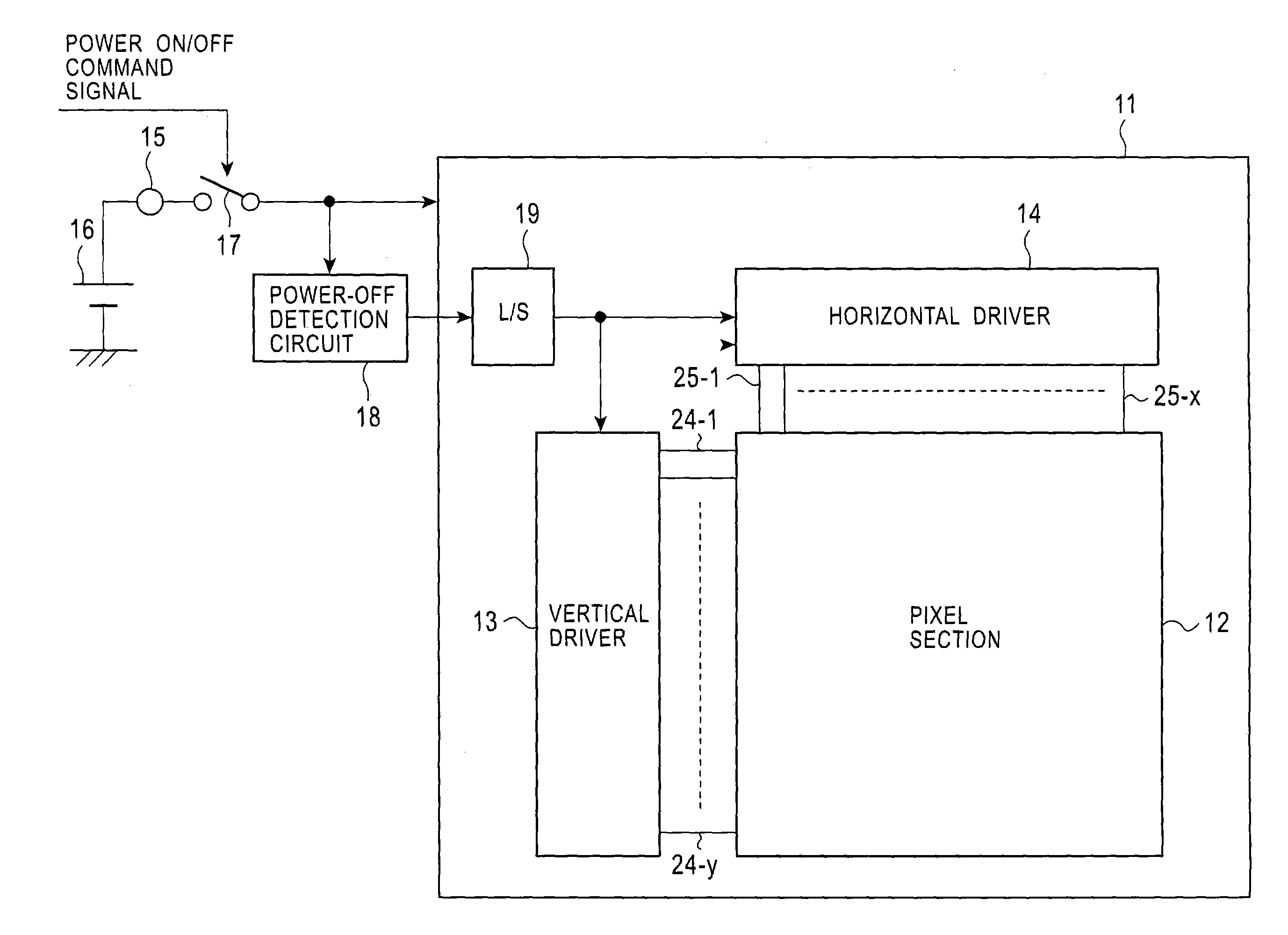

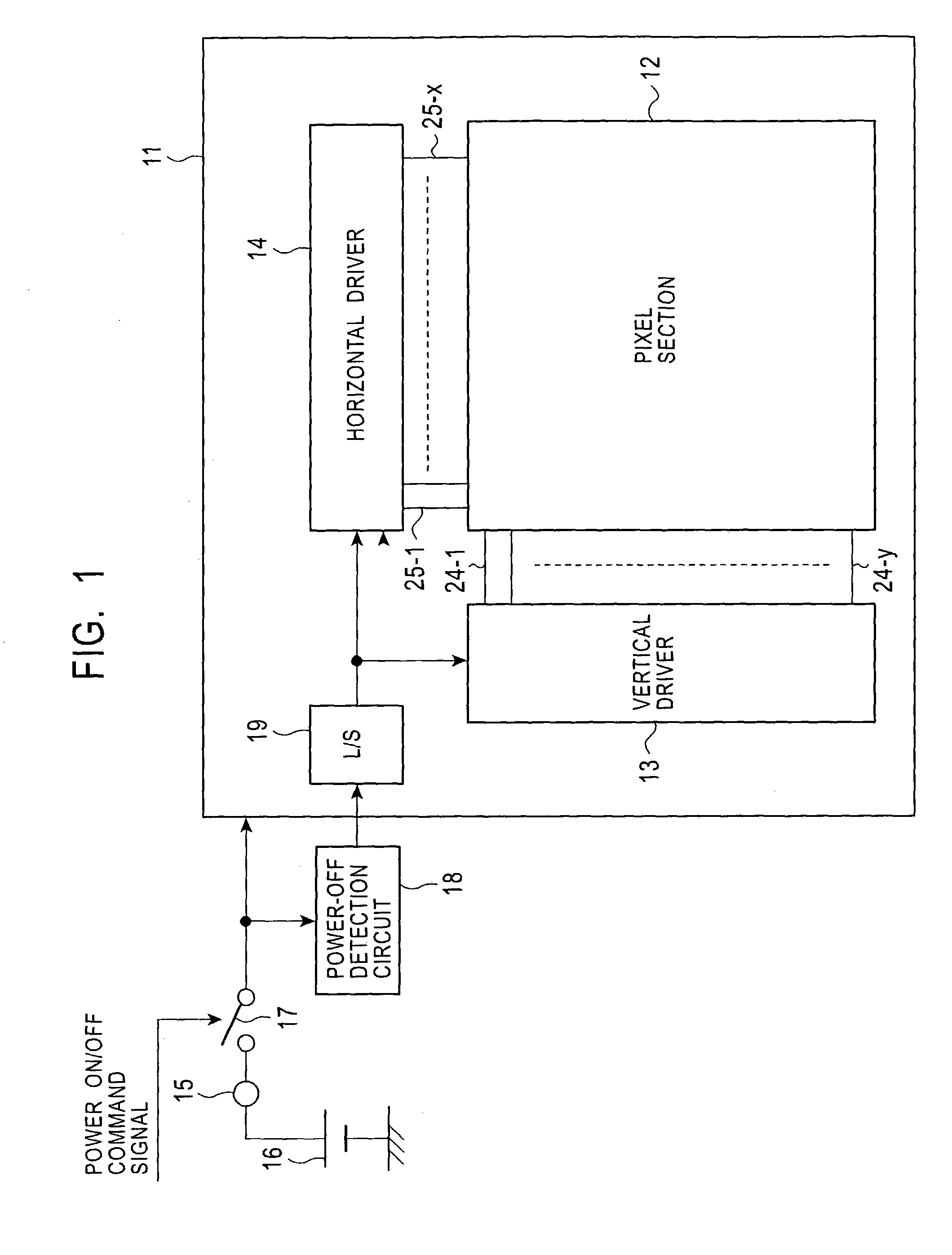

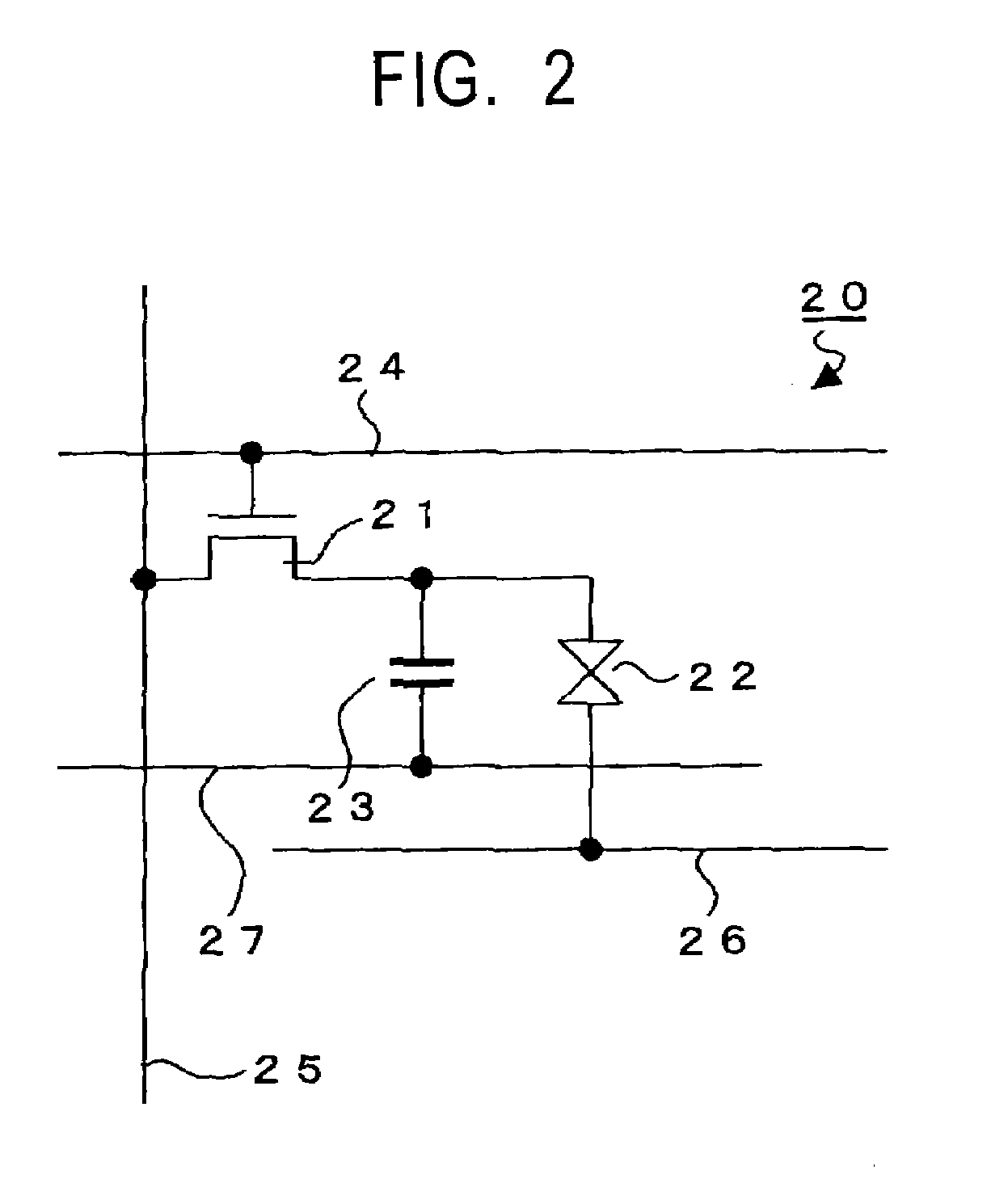

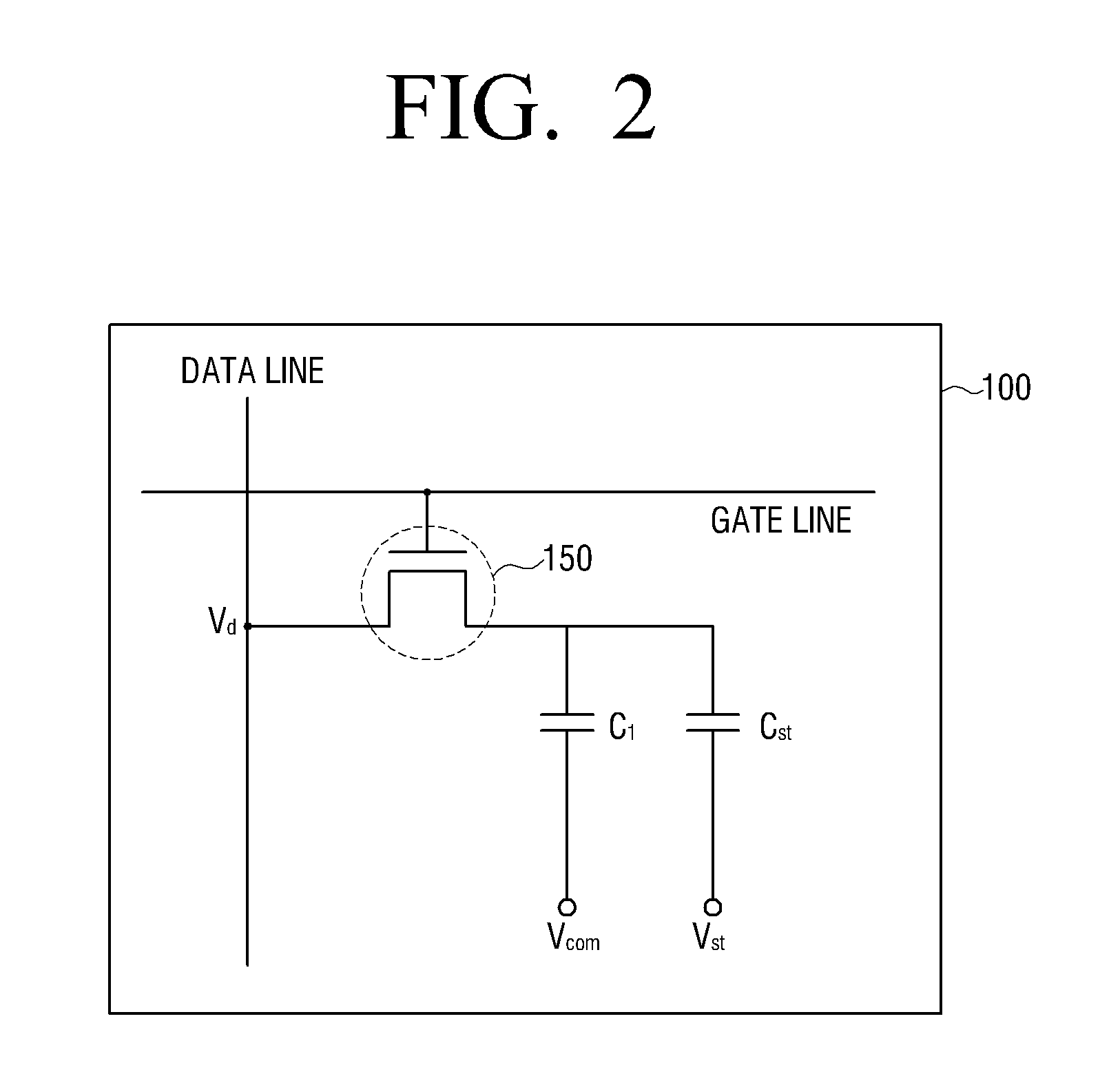

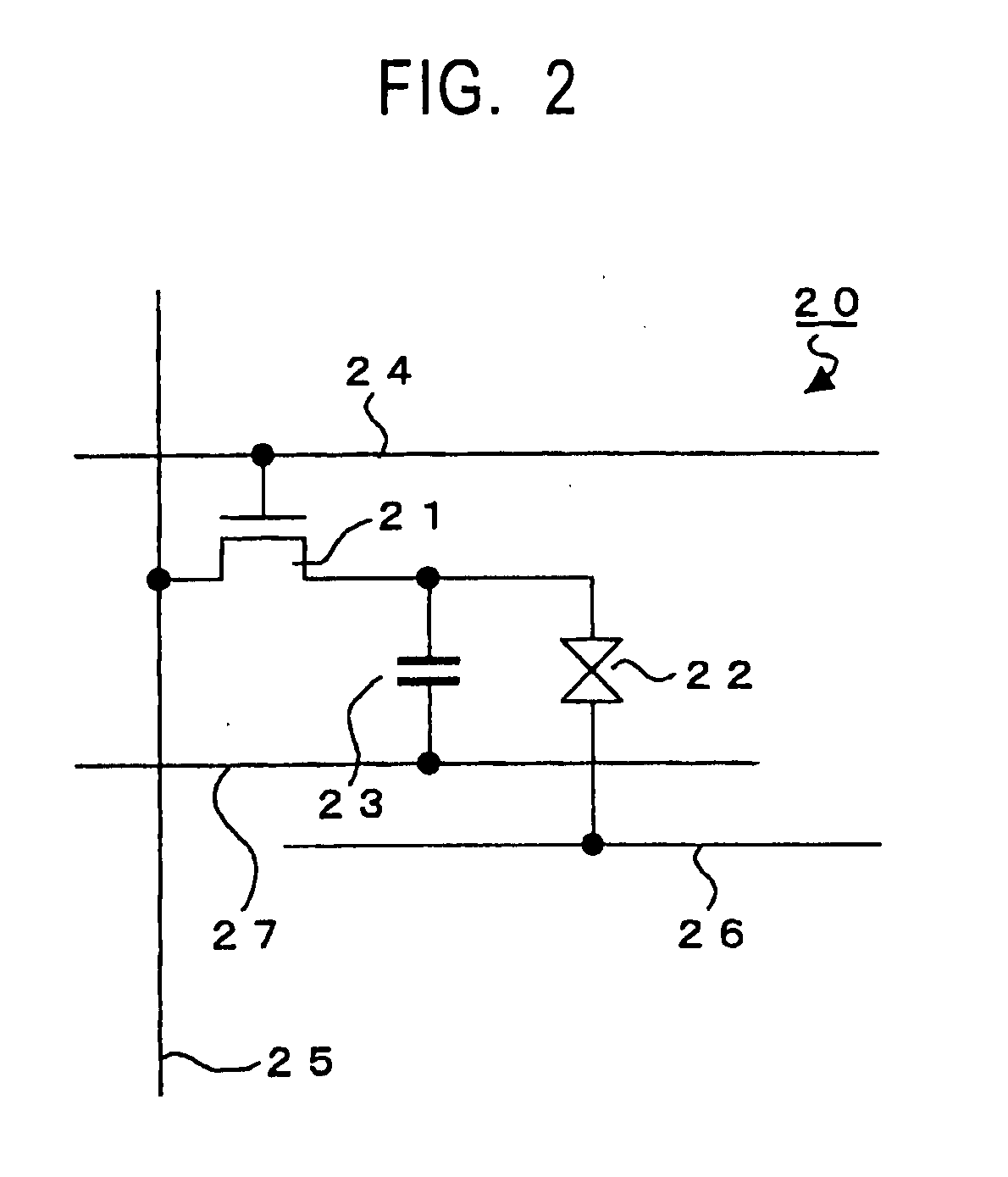

An active-matrix liquid crystal display device has pixels arranged in a matrix which each include a thin film transistor (TFT) as an active element. When the device is in a power-off state, TFTs in all the pixels are switched on, and all horizontal switches are turned on so that all data lines are supplied with a potential equal to the potential of common electrodes of the pixels. This forms a discharging path for discharging residual charge in all the pixels, and the discharging path can instantaneously discharge the residual charges.

Owner:JAPAN DISPLAY WEST

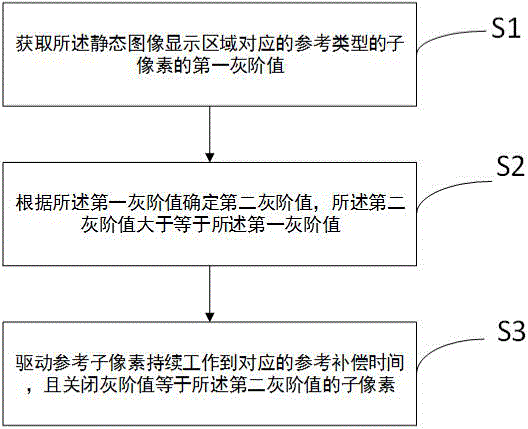

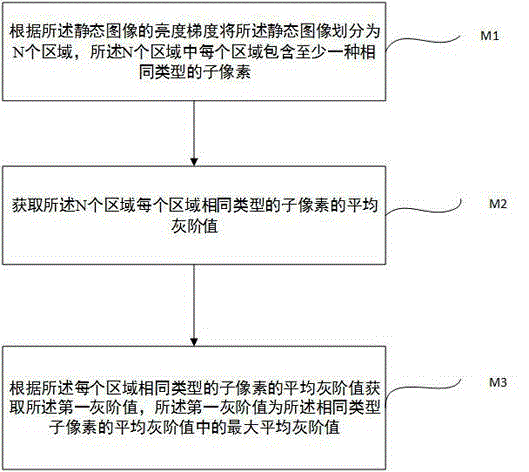

Method and system for eliminating afterimage defect of static-state image display area

ActiveCN104318893AReduced grayscale attenuation varianceEliminate afterimageStatic indicating devicesReference typeGray level

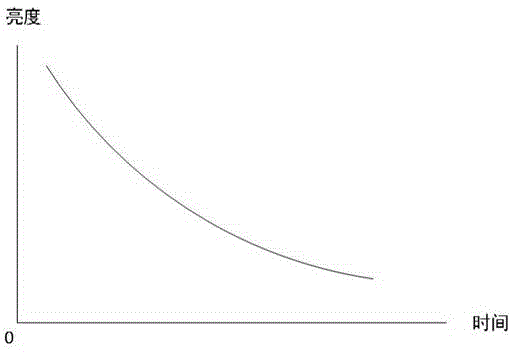

The invention discloses a method and system for eliminating an afterimage defect of a static-state image display area, and is applied to a self-luminous display apparatus. The static-state image display area comprises at least two sub pixels of the same type yet with different grayscale values. The method comprises: obtaining the first grayscale value of a sub pixel of a reference type corresponding to the static-state image display area, wherein the reference type is any one from RGB types, and the first grayscale value is the maximum grayscale value in the grayscale values of all the sub pixels of the reference type; according to the first grayscale value, determining a second grayscale value, the second grayscale value being greater than or equal to the first grayscale value; and driving a reference sub pixel to work continuously for corresponding reference compensation time, and closing a sub pixel whose grayscale value is equal to the second grayscale value, wherein the reference sub pixel is any one sub pixel of the reference type, whose grayscale value is smaller than the second grayscale value, and the reference compensation time is the continuous work time of the reference sub pixel. By using the technical scheme provided by the embodiments of the invention, once an image of the self-luminous display apparatus generates the afterimage defect problem, the problem can be rapidly eliminated.

Owner:HISENSE VISUAL TECH CO LTD

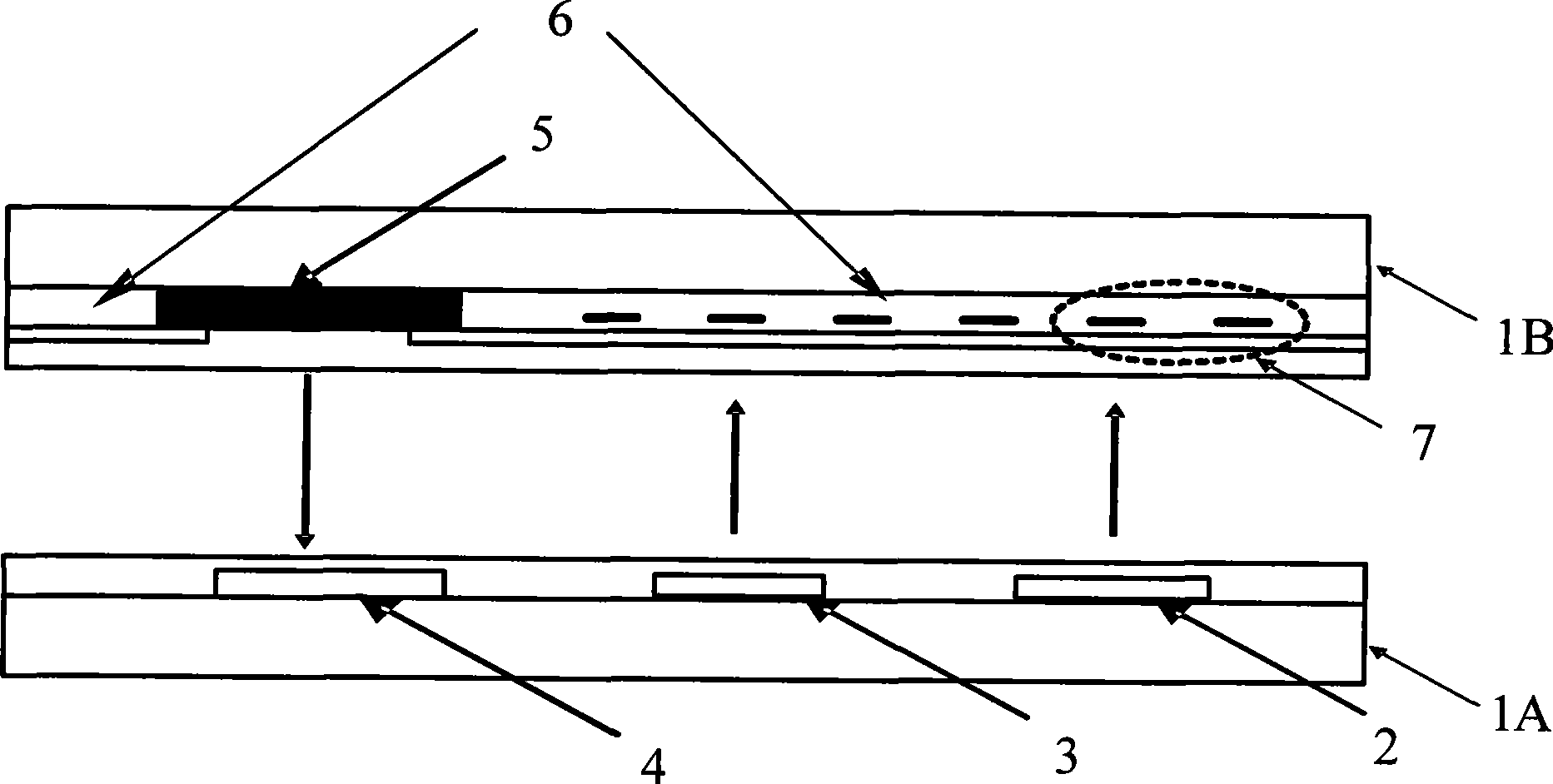

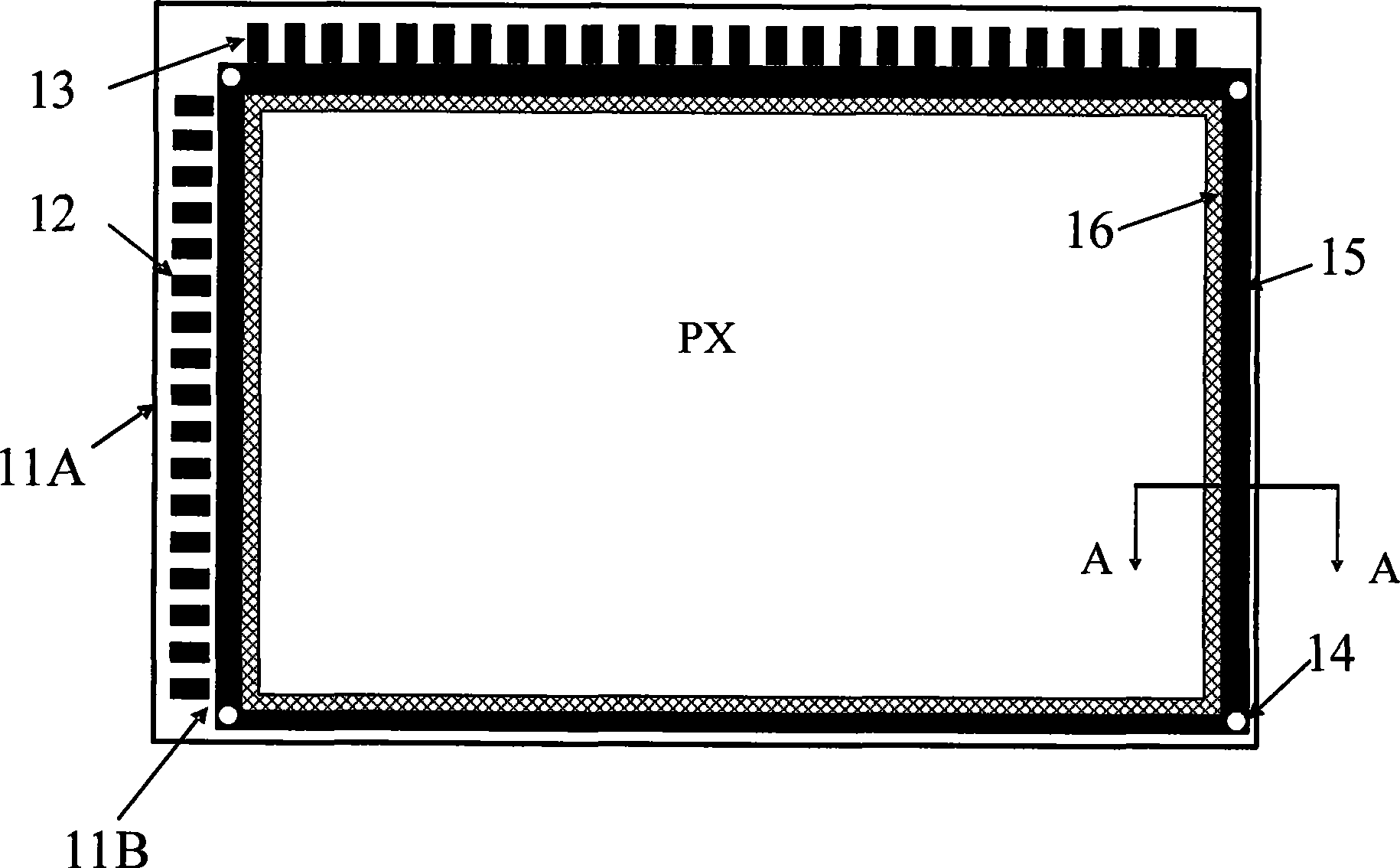

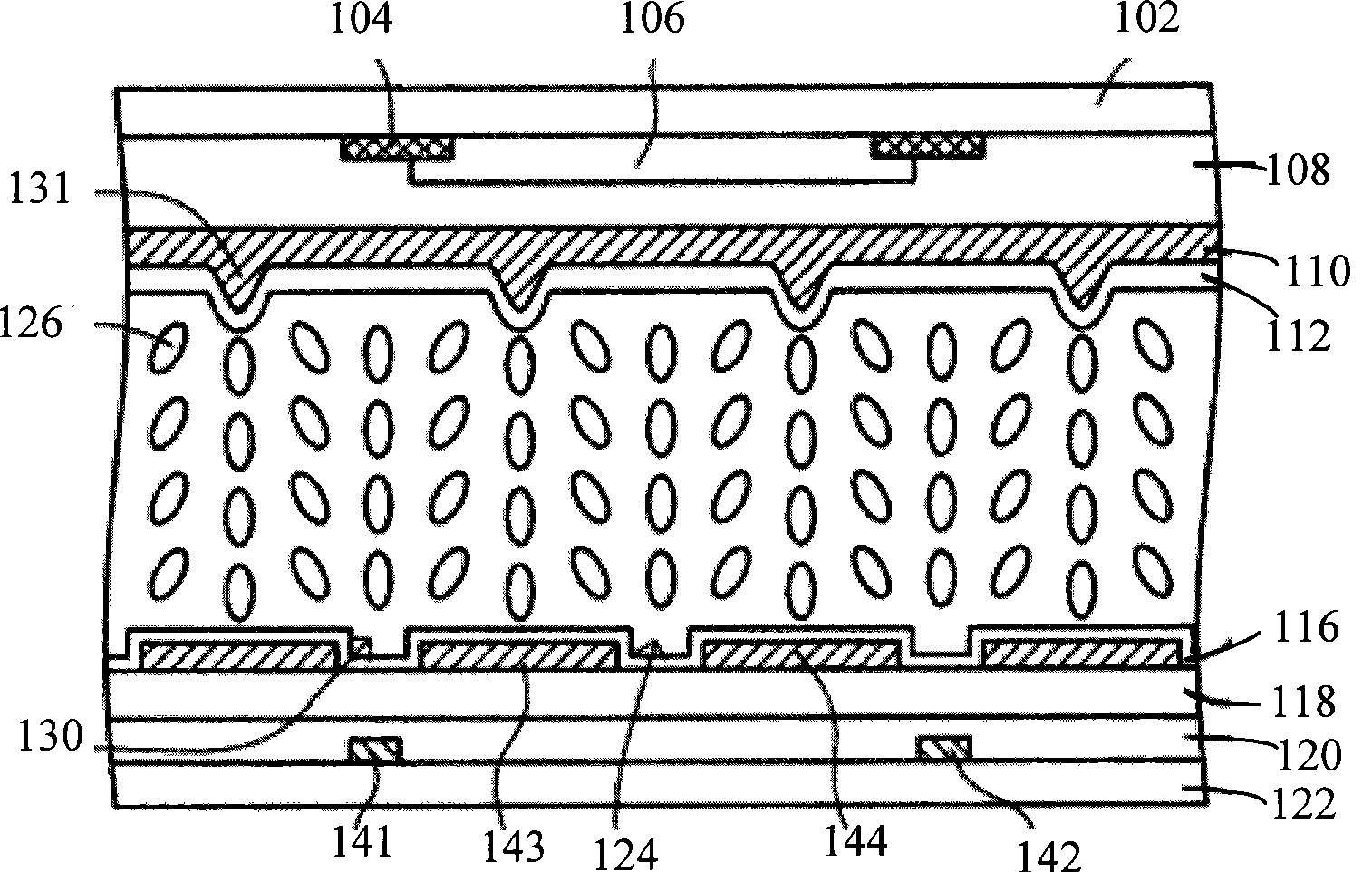

LCD device

InactiveCN101424839AEliminate afterimageImprove qualitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringAfterimage

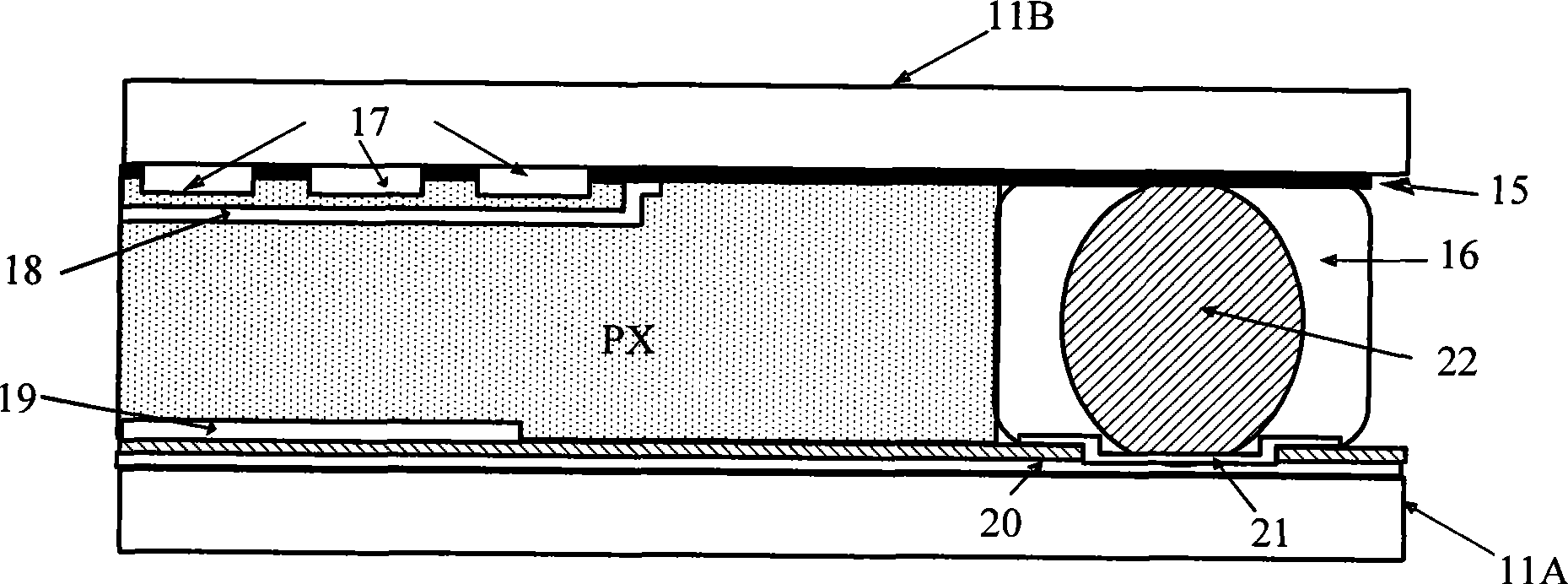

The invention relates to a liquid crystal display device which comprises an array base plate, a colored filter base plate arranged relatively to the array base plate, a metal layer with an earth potential, and a black matrix layer positioned at one side of the colored filter base plate, wherein the array base plate and the colored filter base plate are connected by a sealant; the metal layer with an earth potential is distributed at one side of the array base plate and a conducting layer is formed on the metal layer with an earth potential; and a conducting component is formed between the conducting layer and the black matrix layer and is connected with the conducting layer and the black matrix layer. The liquid crystal display device can prevent an opening part from forming a longitudinal direct current biasing electric field and ensure enough and stable earth potential on a black matrix, thereby eliminating an afterimage in an image and improving the quality of the liquid crystal display device.

Owner:SHANGHAI SVA LIQUID CRYSTAL DISPLAY

Planar display

InactiveCN101364390AEliminate afterimageIncrease working voltageStatic indicating devicesShift registerControl signal

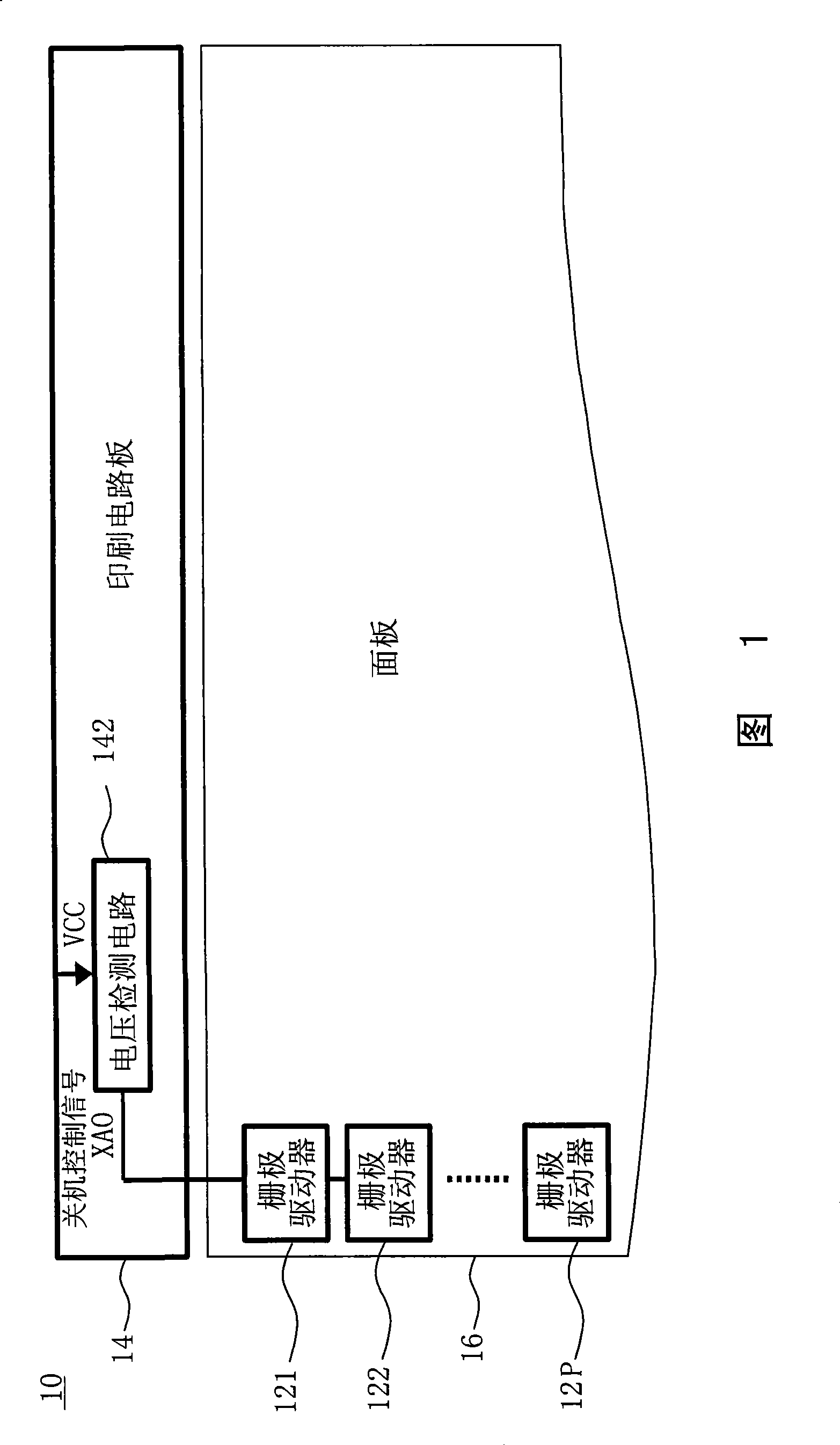

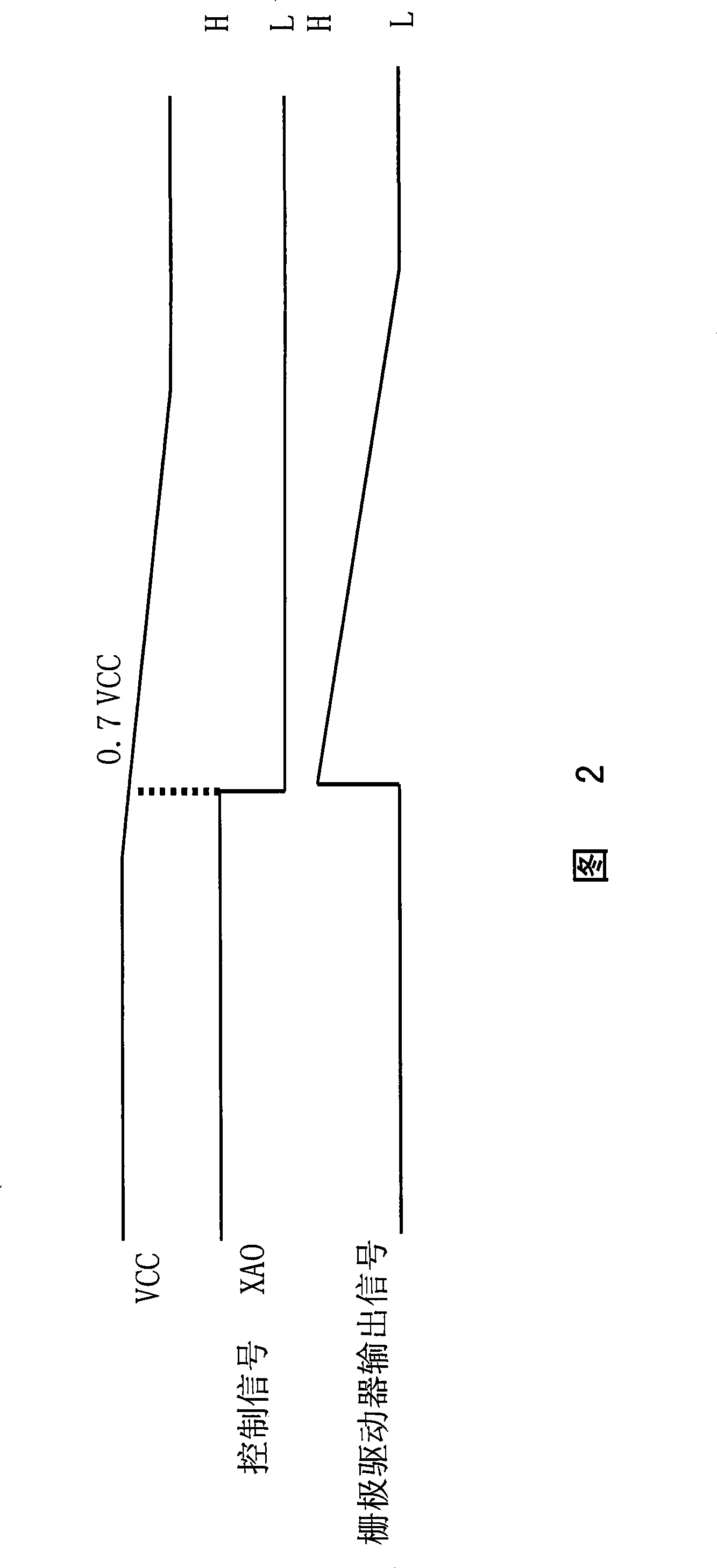

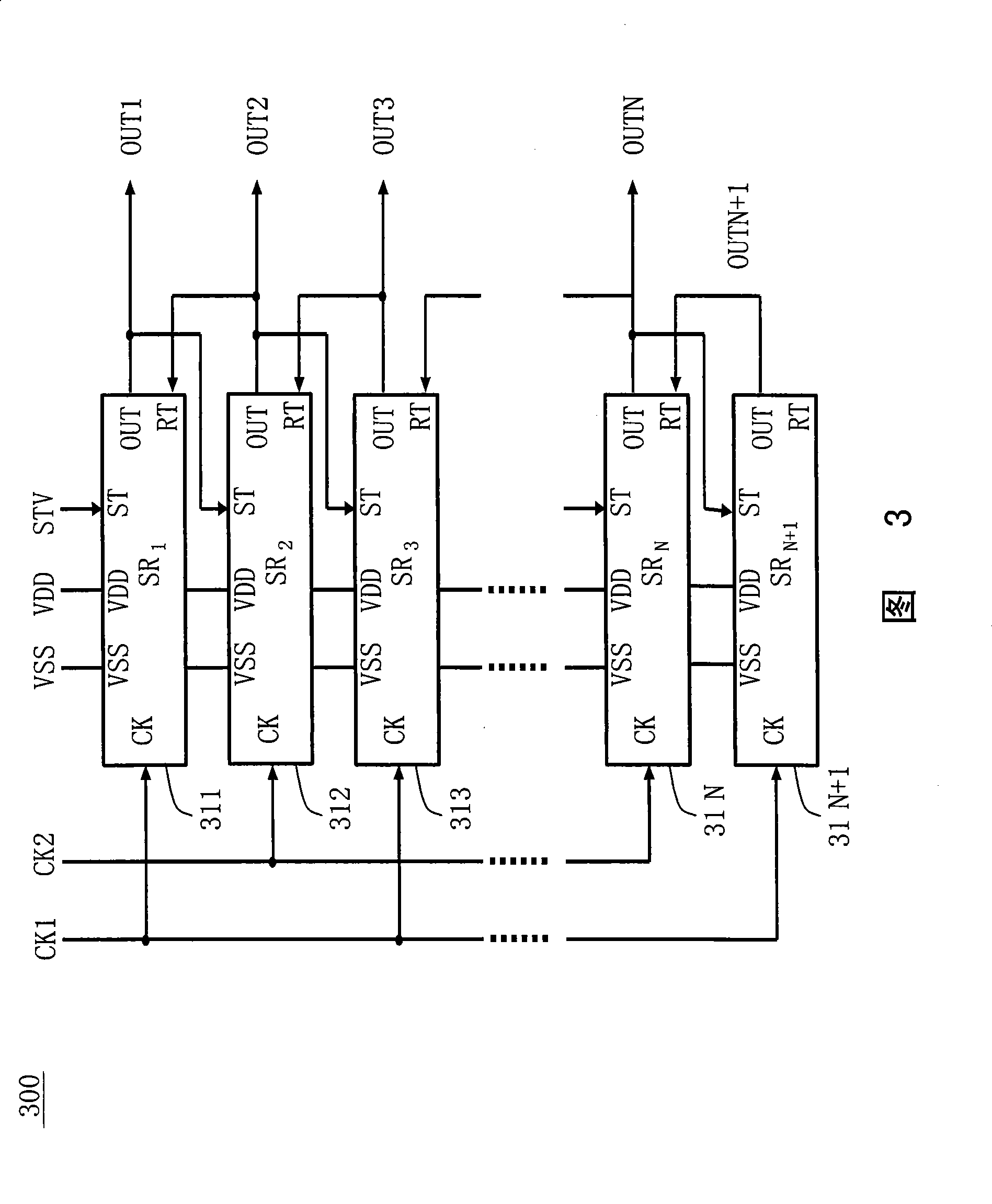

The invention discloses a flat panel display, which comprises a plurality of pixel electrodes, a first multiplexer, a second multiplexer, a third multiplexer and a gate driver. The gate driver is electronically connected with the pixel electrode, and provided with N plus 1 shift registers. The nth shift register comprises an SR trigger, a first transistor and a second transistor. When the flat panel display is turned off, a turning-off control signal is converted from a high potential voltage to a low potential voltage, so as to switch an input low power supply voltage outputted from the first multiplexer to a high operating voltage, switch a zeroth input time pulse signal outputted from the second multiplexer to a high operating voltage and switch a first input time pulse signal outputted from the third multiplexer to a high operating voltage, thereby resulting in conduction of the first transistor or the second transistor, and the nth output signal outputs the high operating voltage to allow the pixel electrodes to take discharge action. By using the turning-off control signal, all pixel electrodes can take discharge action, so as to eliminate afterimage during the turning-off.

Owner:INNOLUX CORP

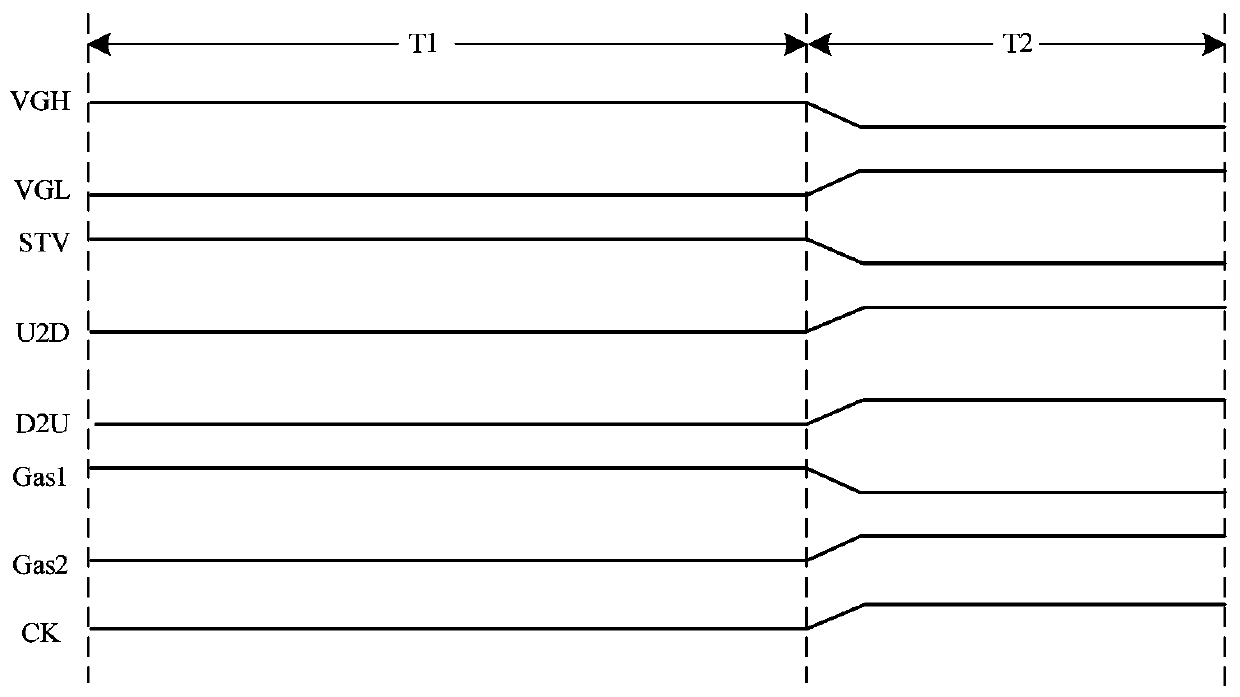

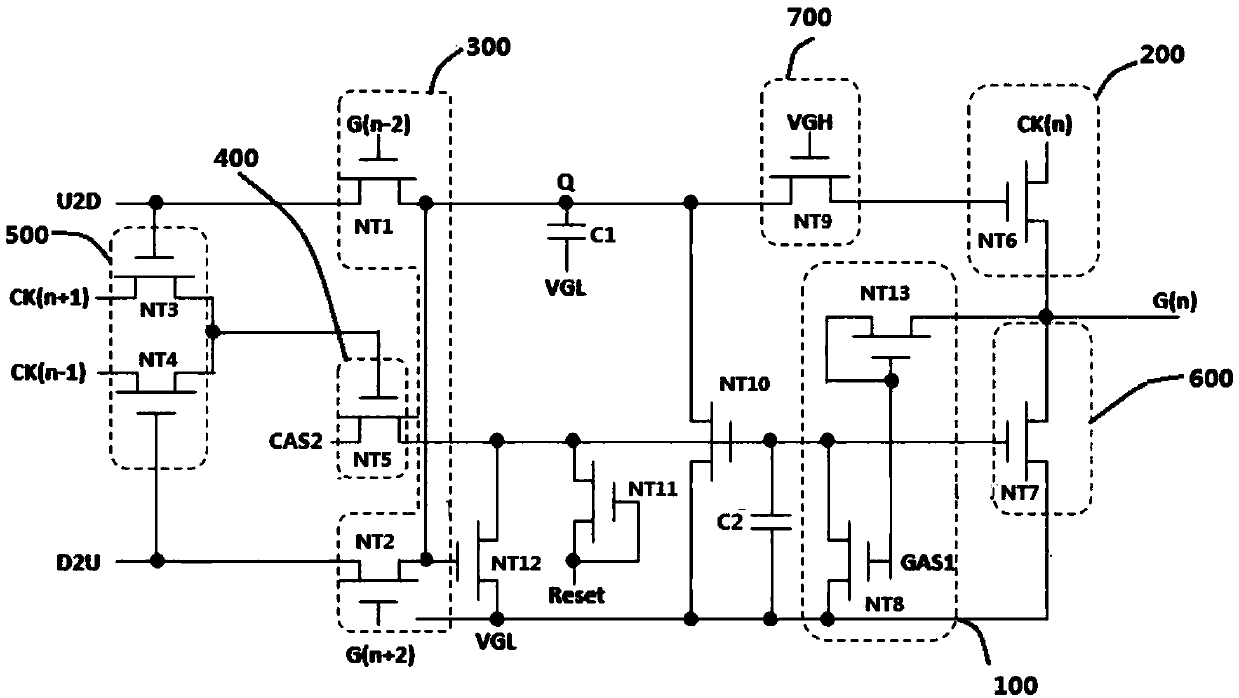

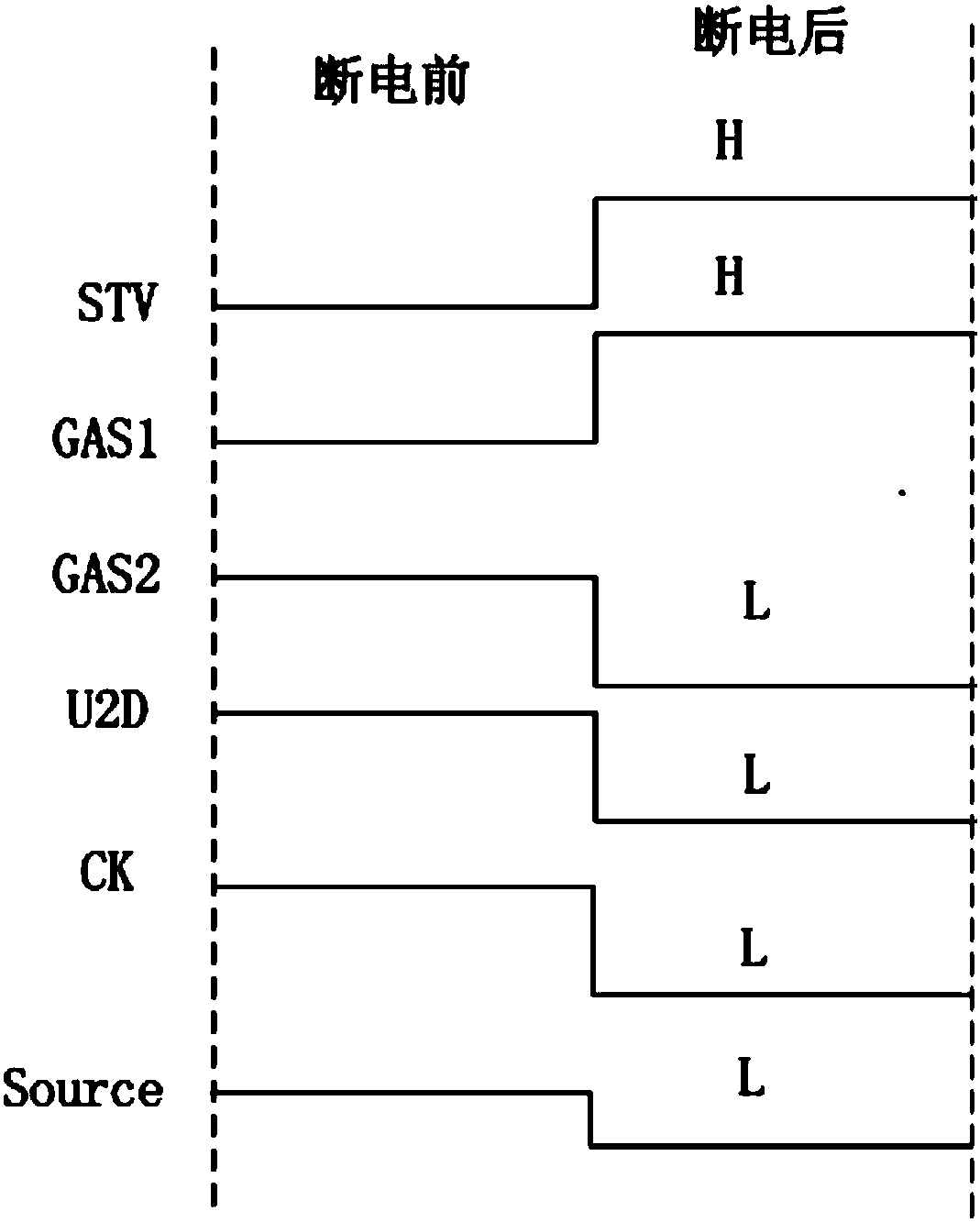

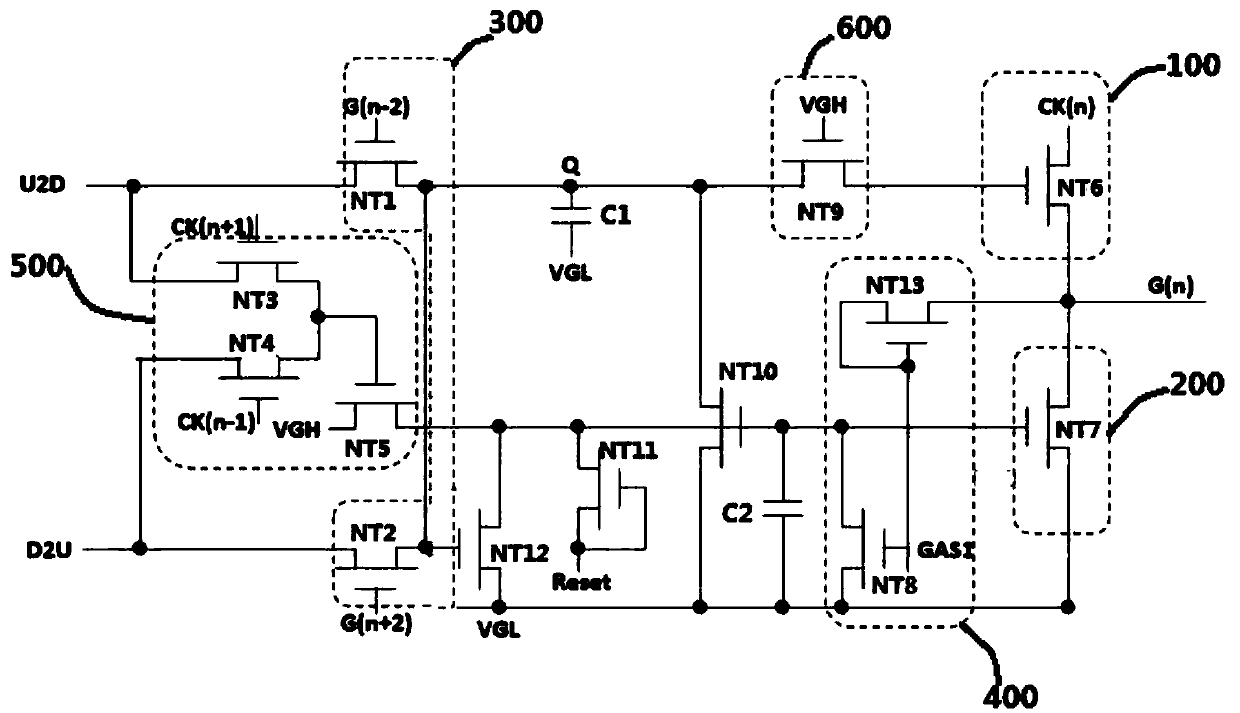

G0A circuit and display panel

InactiveCN110782855AEliminate afterimageImprove experienceStatic indicating devicesHemt circuitsControl theory

The invention provides a G0A circuit and a display panel. The G0A circuit comprises m cascaded GOA units, and the nth GOA unit comprises a forward and reverse scanning control module, a node signal control module, an output control module, a pull-up module, a first pull-down module and a potential control module. The node signal control module is used for controlling the GOA circuit to output a low-potential gate drive signal and comprises a first node, and the first node is a gate signal control node of the node signal control module; the pull-up module is used for controlling the GOA circuitto output a high-potential gate drive signal; the first pull-down module is used for pulling down the potential of the gate drive signal of the current stage and is connected with the node signal control module through a second node, and the second node is a gate signal control node of the first pull-down module; the potential control module is connected with the node signal control module through the first node and used for controlling the first node to be at a low potential when the display panel is powered off abnormally. According to the invention, ghosting of the display panel during power failure is eliminated.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

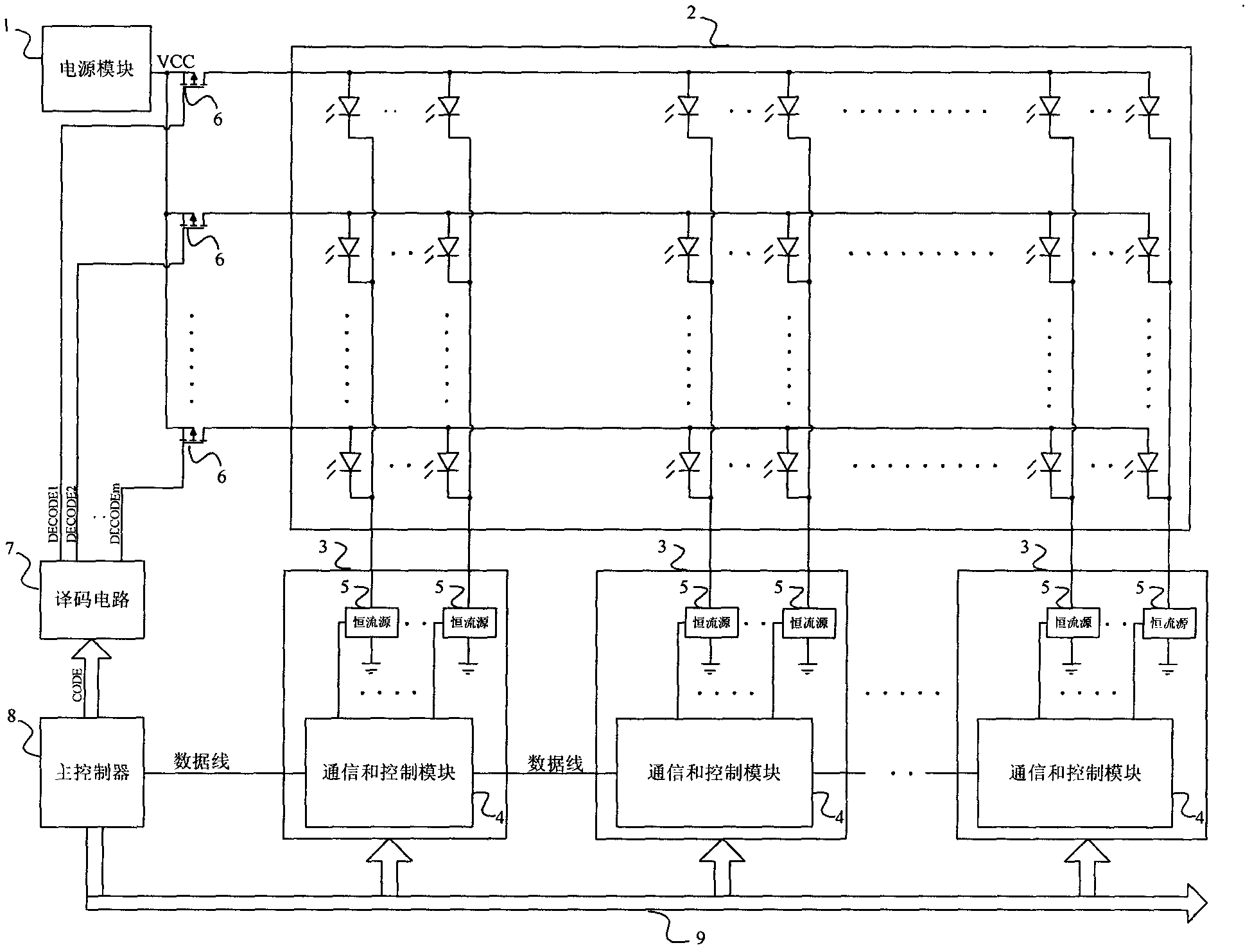

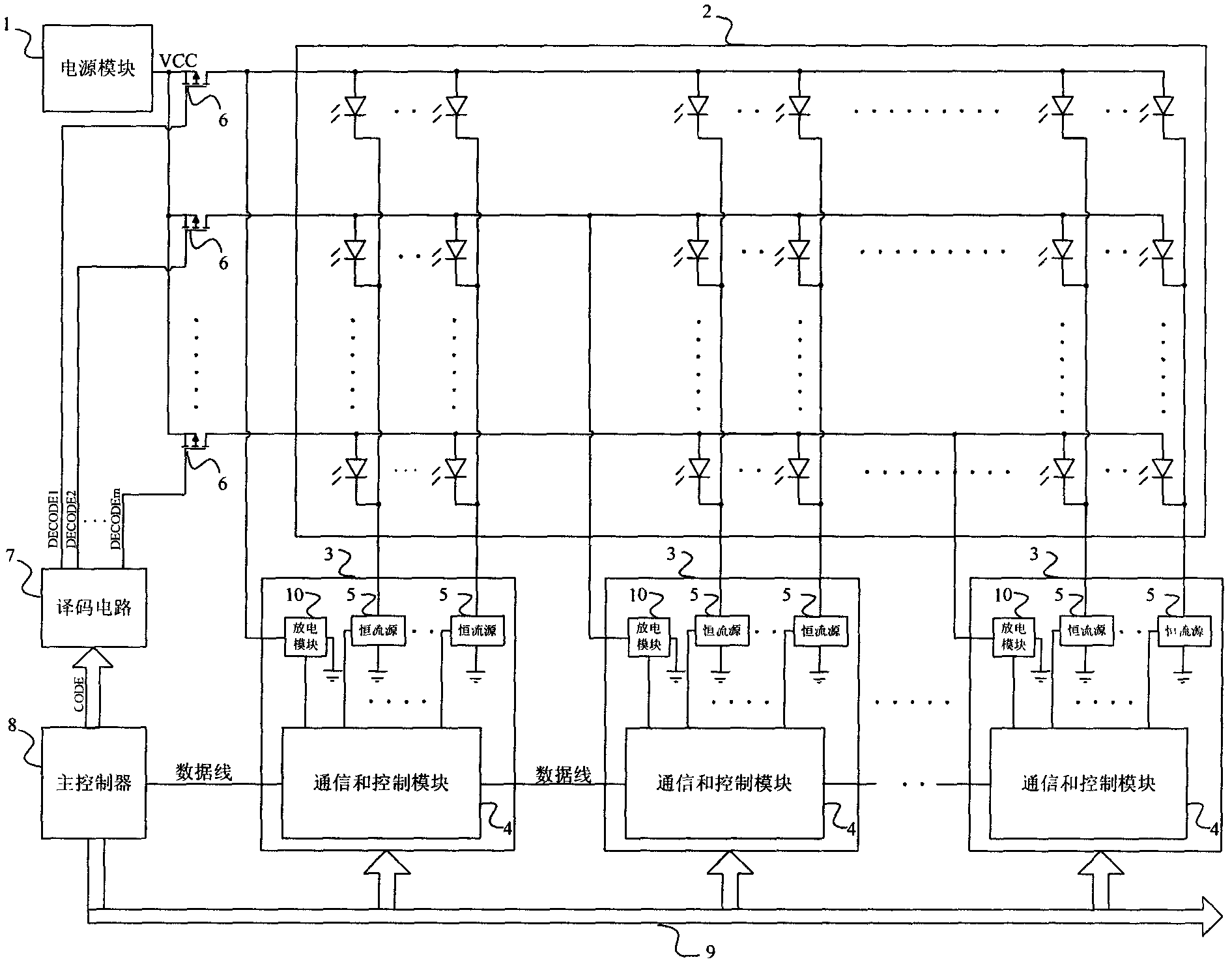

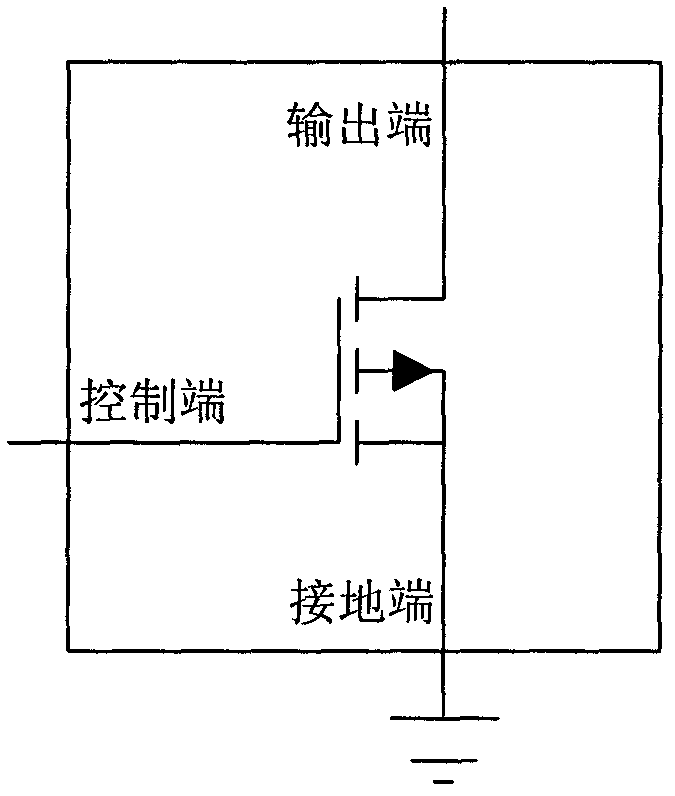

LED (light-emitted diode) display system capable of eliminating dynamic LED display ghost

The invention relates to an LED (light-emitted diode) display system capable of eliminating dynamic LED display ghost includes a power supply module, an LED array, M switch tubes, a decoding circuit, multiple constant-current driving circuits and a main controller, wherein each constant-current driving circuit is provided with a discharge module, the main controller sends discharge control signals to communication and control modules of all constant-current driving circuits through a control bus when LED lines are being switched in the LED array during the dynamic displaying time, and the discharge module of each constant-current driving circuit discharges a spurious charge at the second end of each cut-off PMOS switch tube from an output port of the discharge module to the system. Superior ghost removing effect can be realized only through a minor hardware modification in the traditional LED display system and the system of the invention has strong practicability.

Owner:杭州士兰控股有限公司

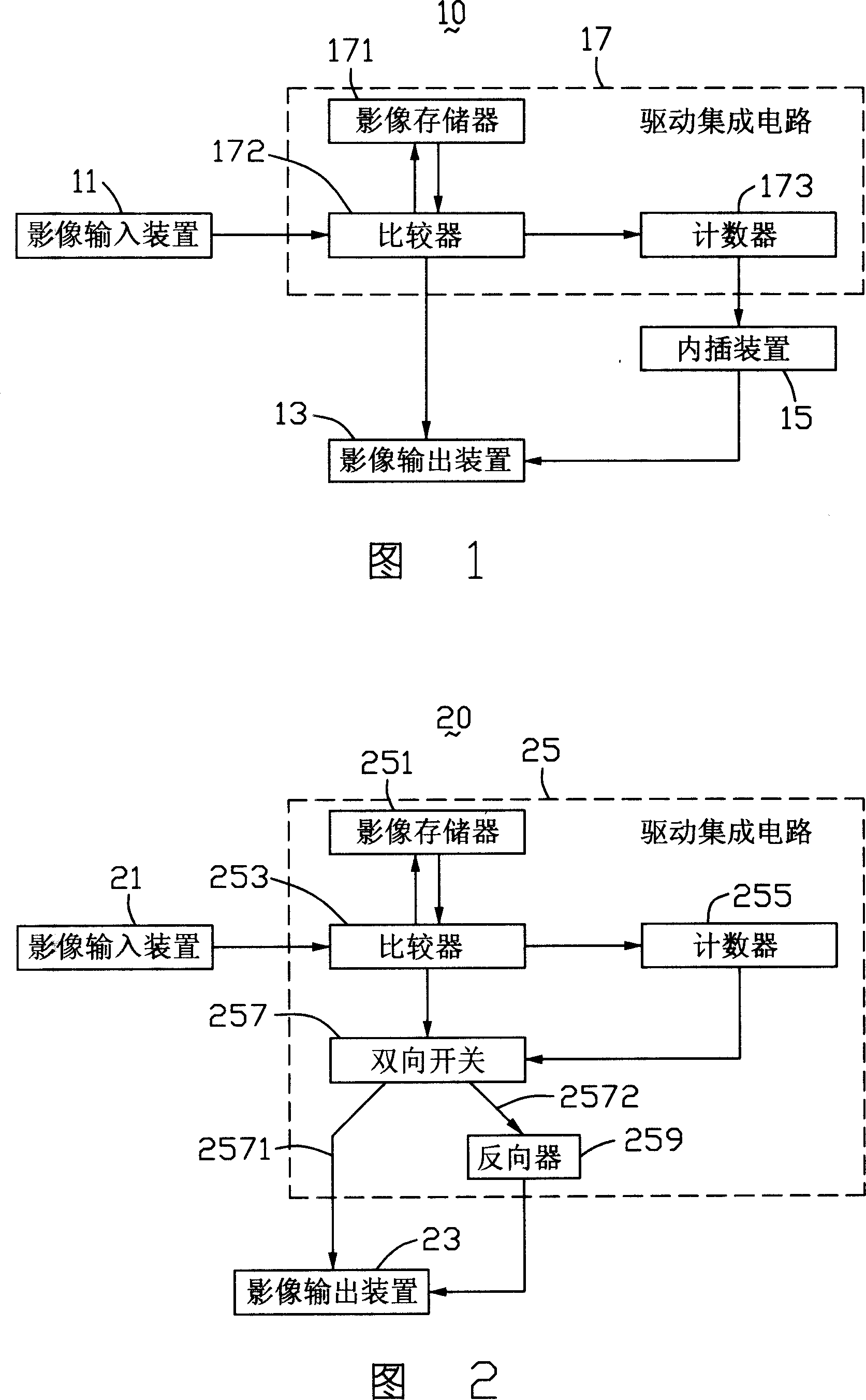

Liquid crystal panel driving device and its driving method

InactiveCN101071543ASimple circuit structureEliminate afterimageStatic indicating devicesVideo memoryLiquid-crystal display

The invention is a LCD panel driver, comprising a drive IC, where the drive IC comprises: a video memory to record the previous image frame displayed by LCD, a comparer, a reverser, a two-way switch and a counter, where the two-way switch comprises a first output end and a second output end, the first output end directly outputs image, and the second output end is connected to the reverser; the counter is used to determine whether the input image is a static image; the reverser reverses the current image frame and outputs an irregular image; the comparer compares the current image frame with the previous image frame and has two output channels, one directly outputting an image through the first output end and the other outputting an irregular image in turn through the counter, the second output end and the reverser. And its circuit structure is simpler and able to be used to eliminate the residual image existing on the LCD panel.

Owner:INNOCOM TECH SHENZHEN +1

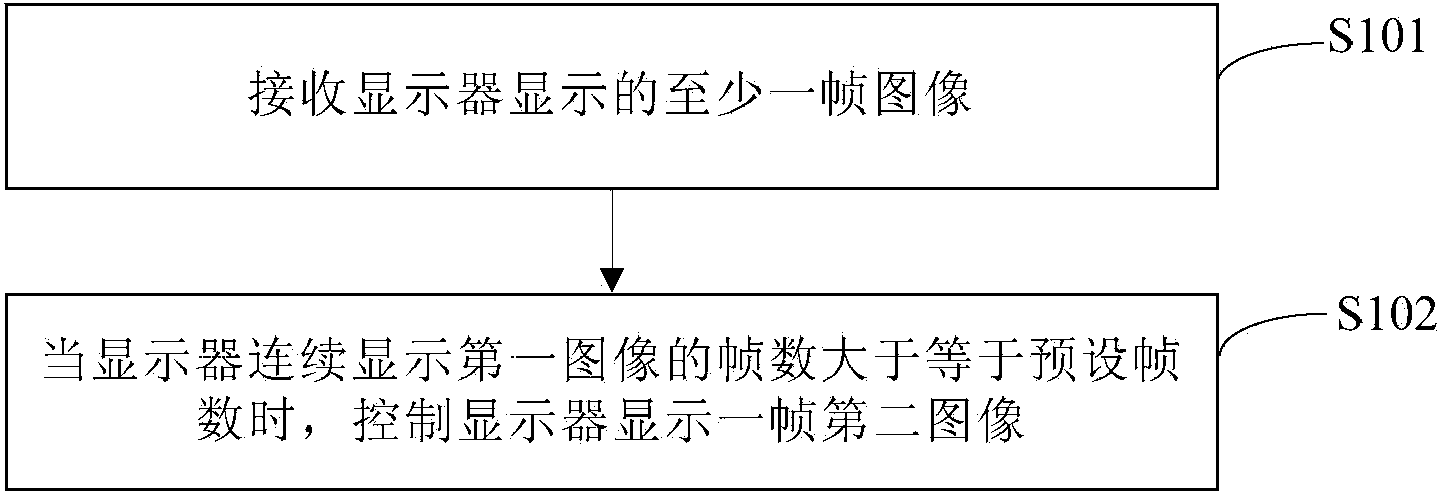

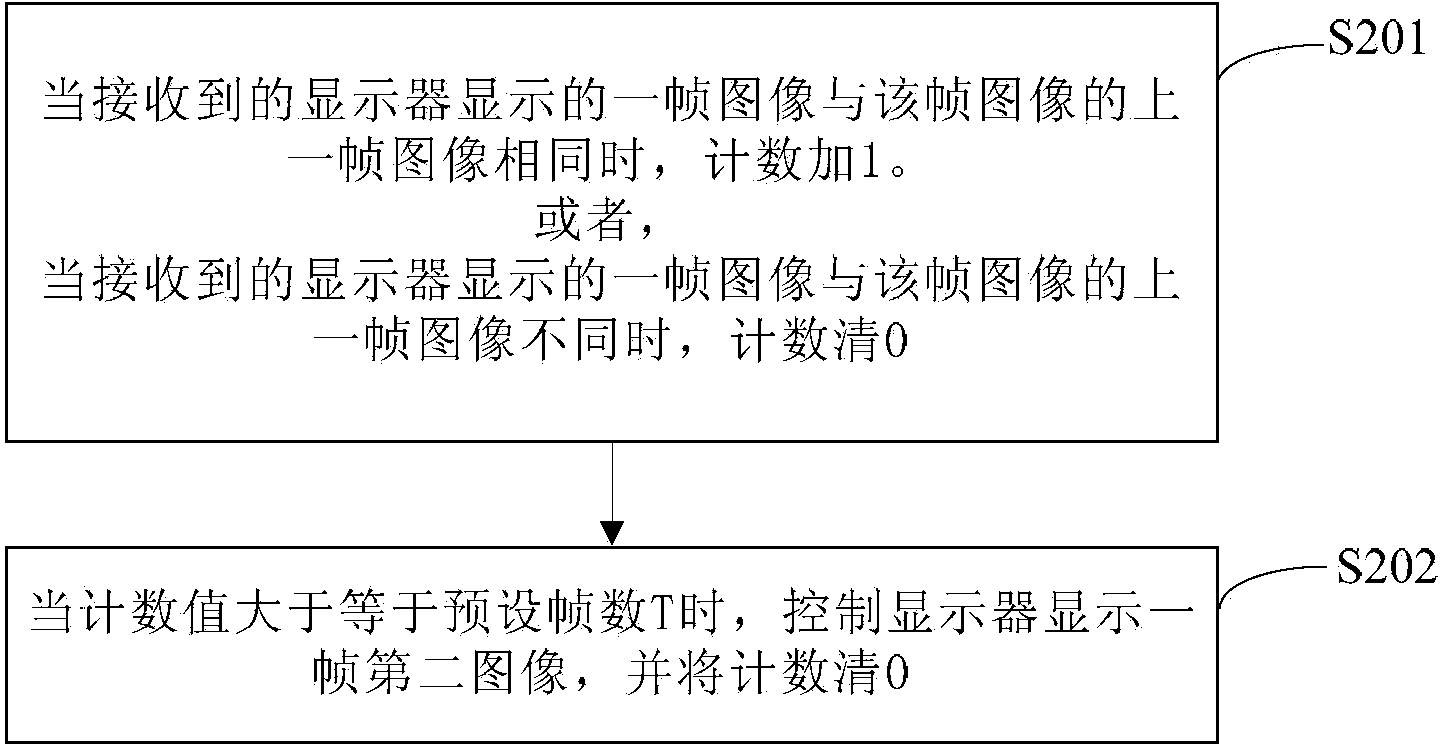

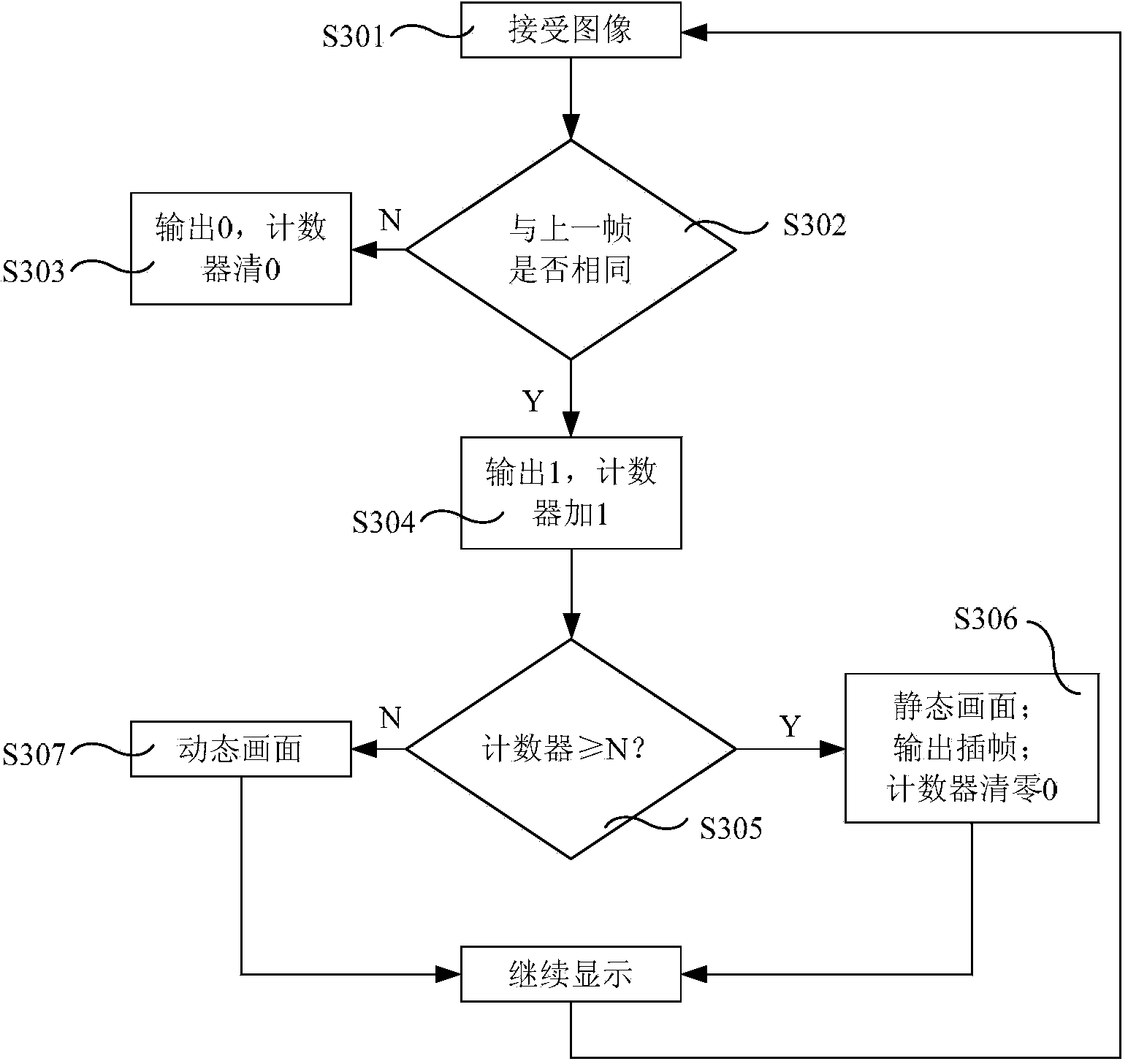

Image display control method and device

ActiveCN103778897AAvoid normal displayEliminate afterimageStatic indicating devicesLiquid-crystal displayComputer graphics (images)

The embodiment of the invention provides an image display control method and device, and relates to the technical field of displaying. It is avoided that a liquid crystal display displays still images for a long time, and therefore residual images are eliminated. The image display control method includes the steps that at least one frame of image displayed by the display is received; when the number of frames of a first image continuously displayed by the display is larger than or equal to the preset frame number, the display is controlled to display one frame of a second image in an interpolation mode. The first image is different from the second image.

Owner:BEIJING BOE DISPLAY TECH CO LTD +1

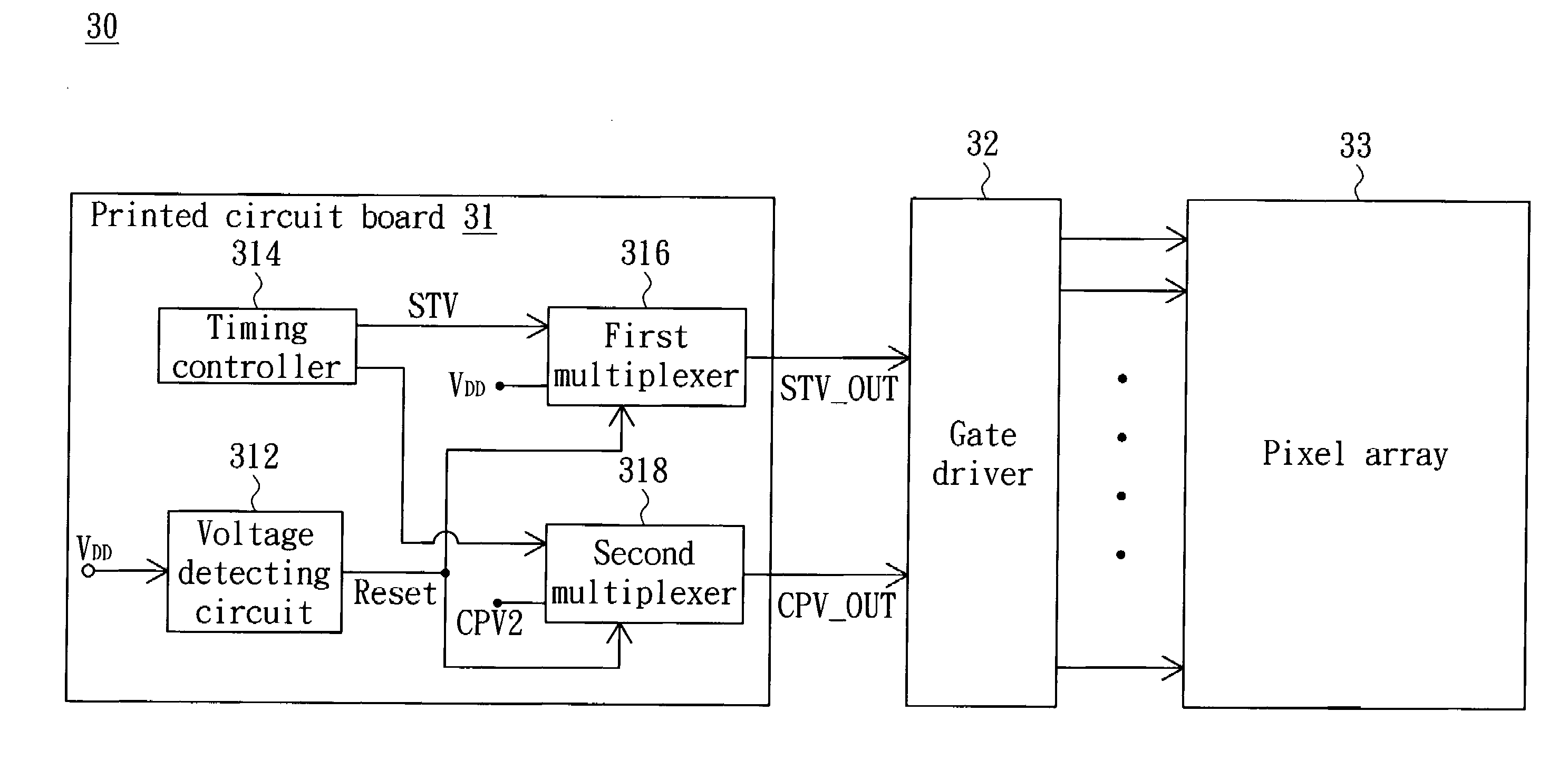

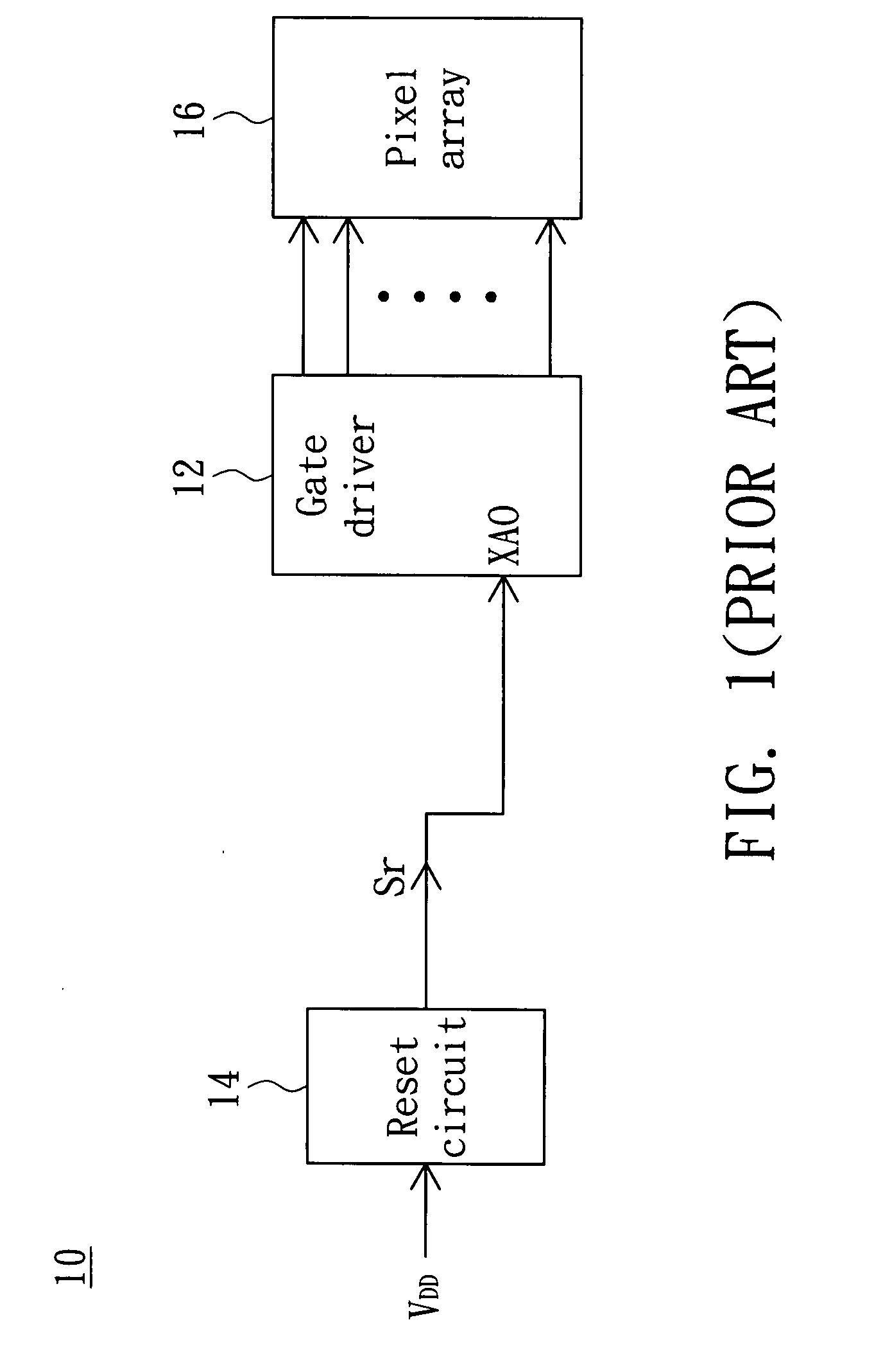

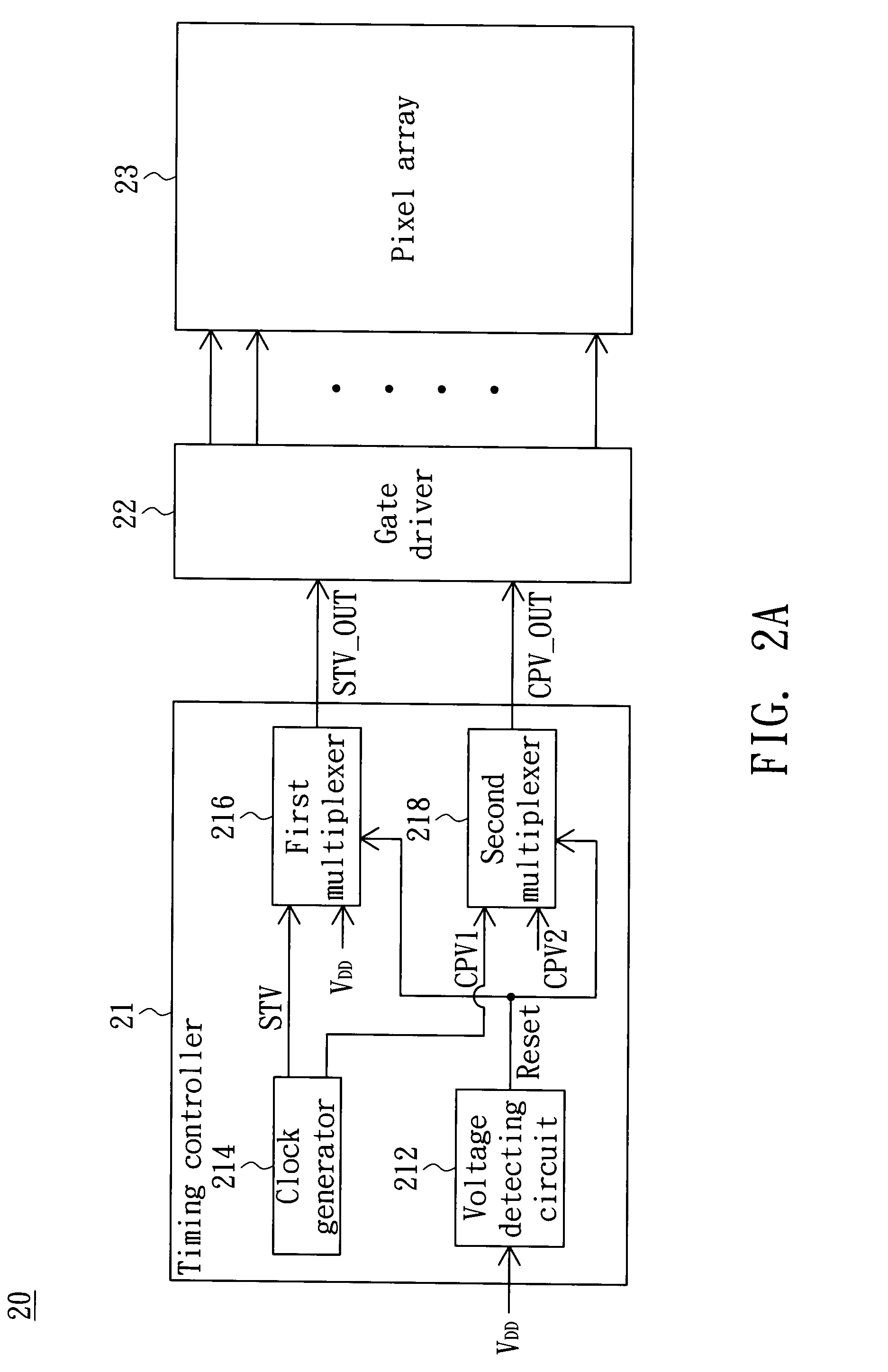

Flat display and timing controller thereof

A timing controller adapted to a flat display includes a voltage detecting circuit, a clock generator, a first multiplexer and a second multiplexer. The voltage detecting circuit detects a variation of an operating voltage and thus outputs a reset signal. The clock generator outputs a start signal and a first clock signal. The first multiplexer is controlled by the reset signal and coupled to the start signal and a constant voltage. The second multiplexer is controlled by the reset signal and coupled to the first clock signal and a second clock signal. A frequency of the second clock signal is obviously higher than a frequency of the first clock signal.

Owner:HIMAX TECH LTD

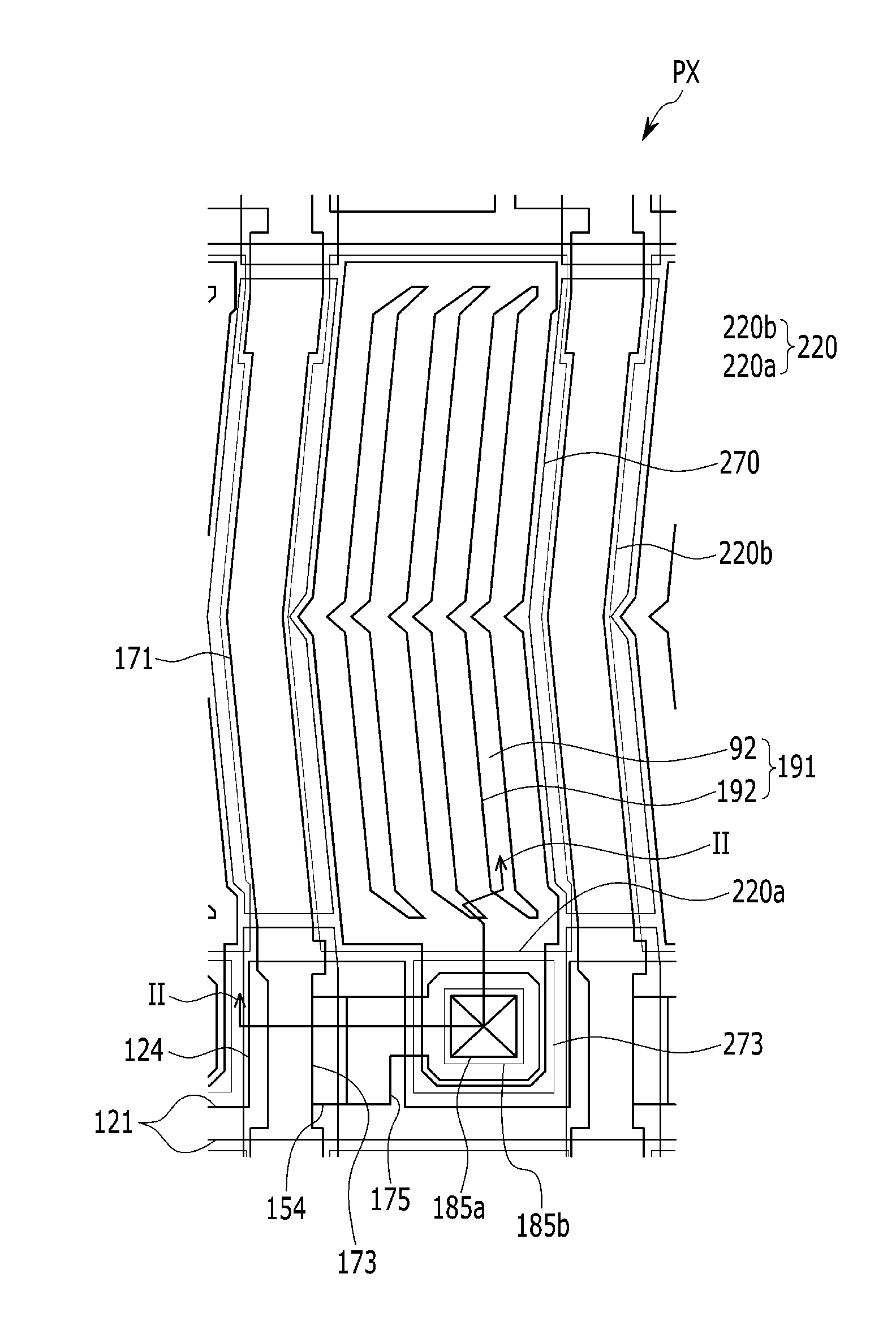

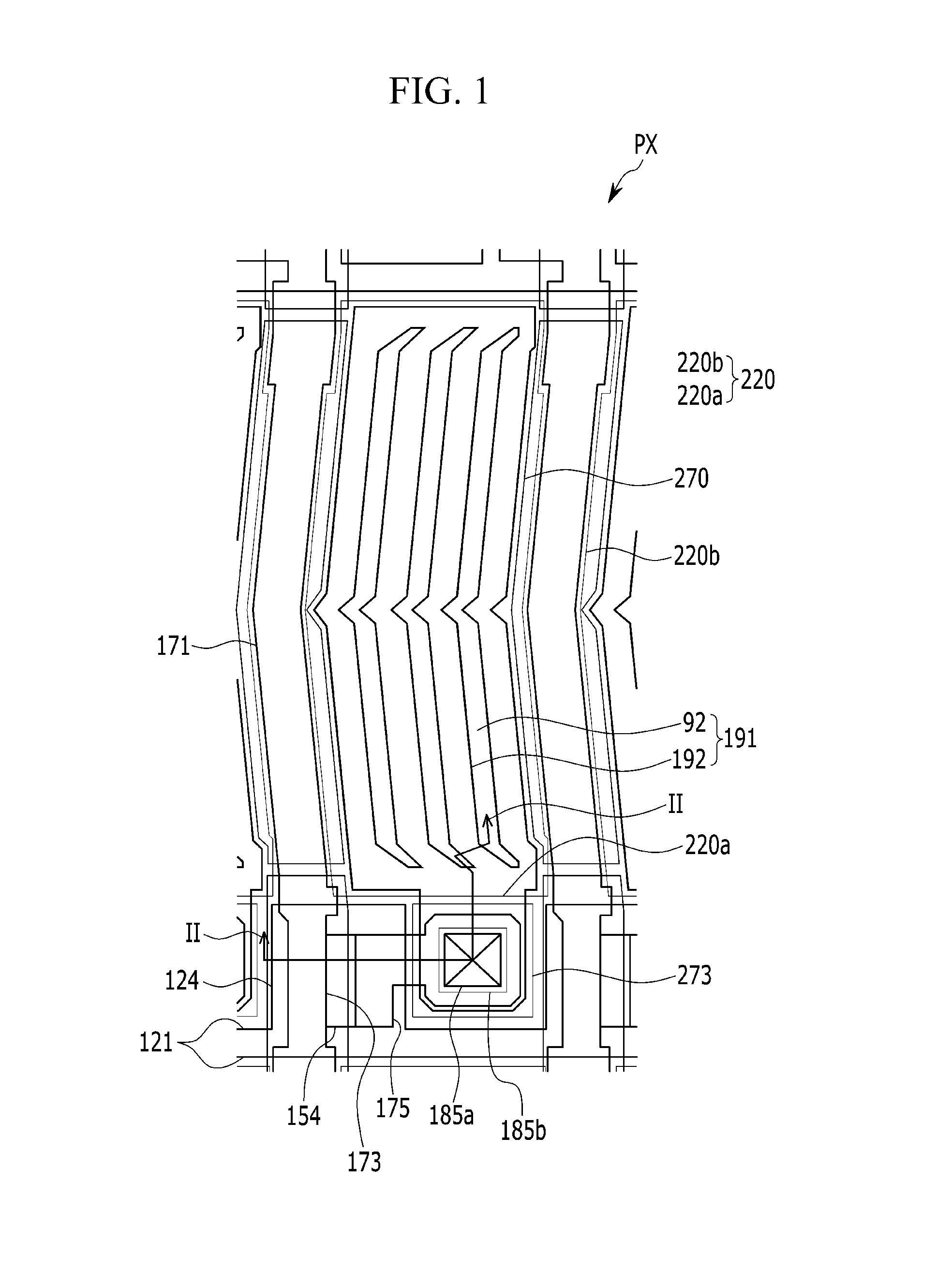

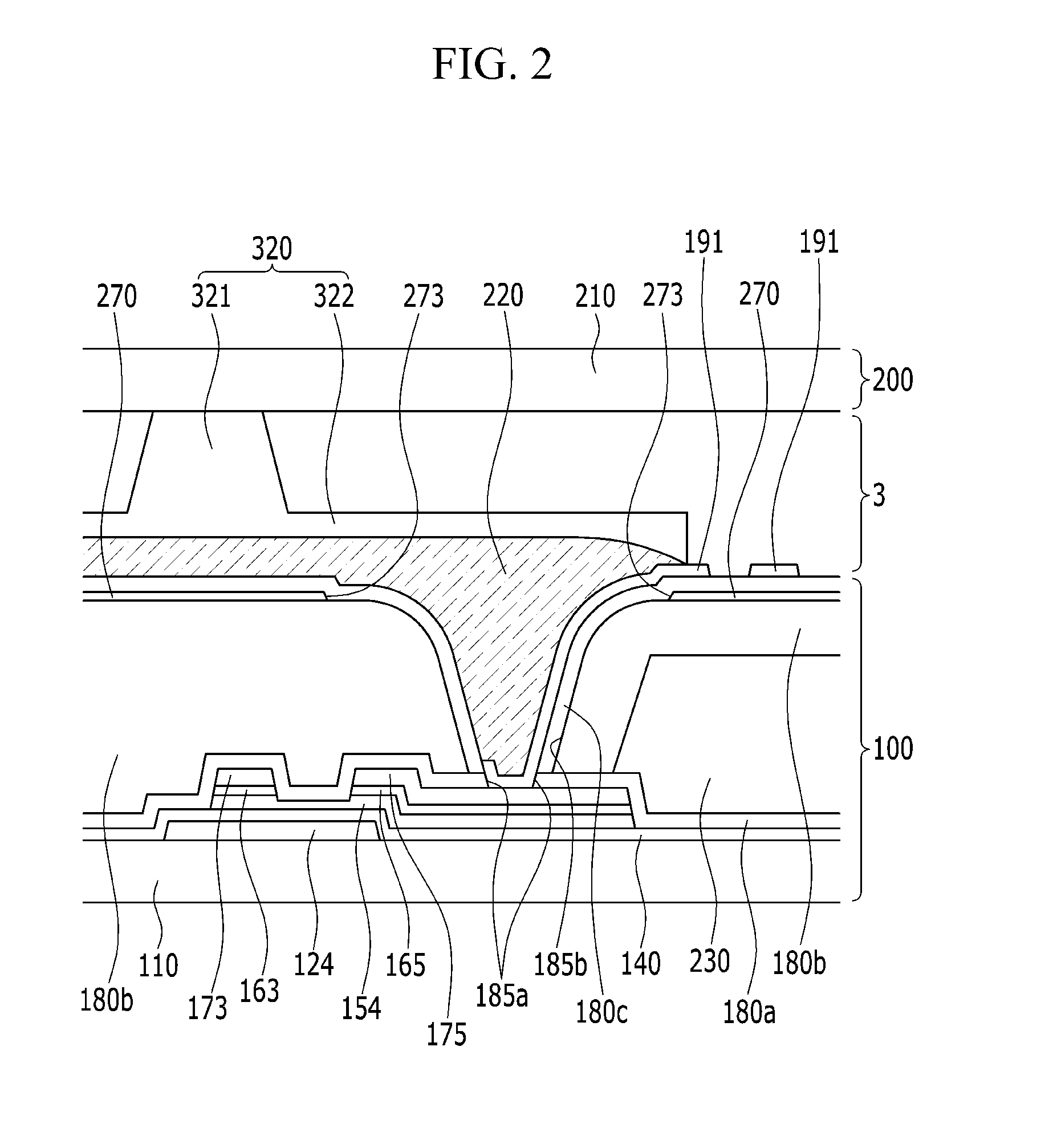

Liquid crystal display

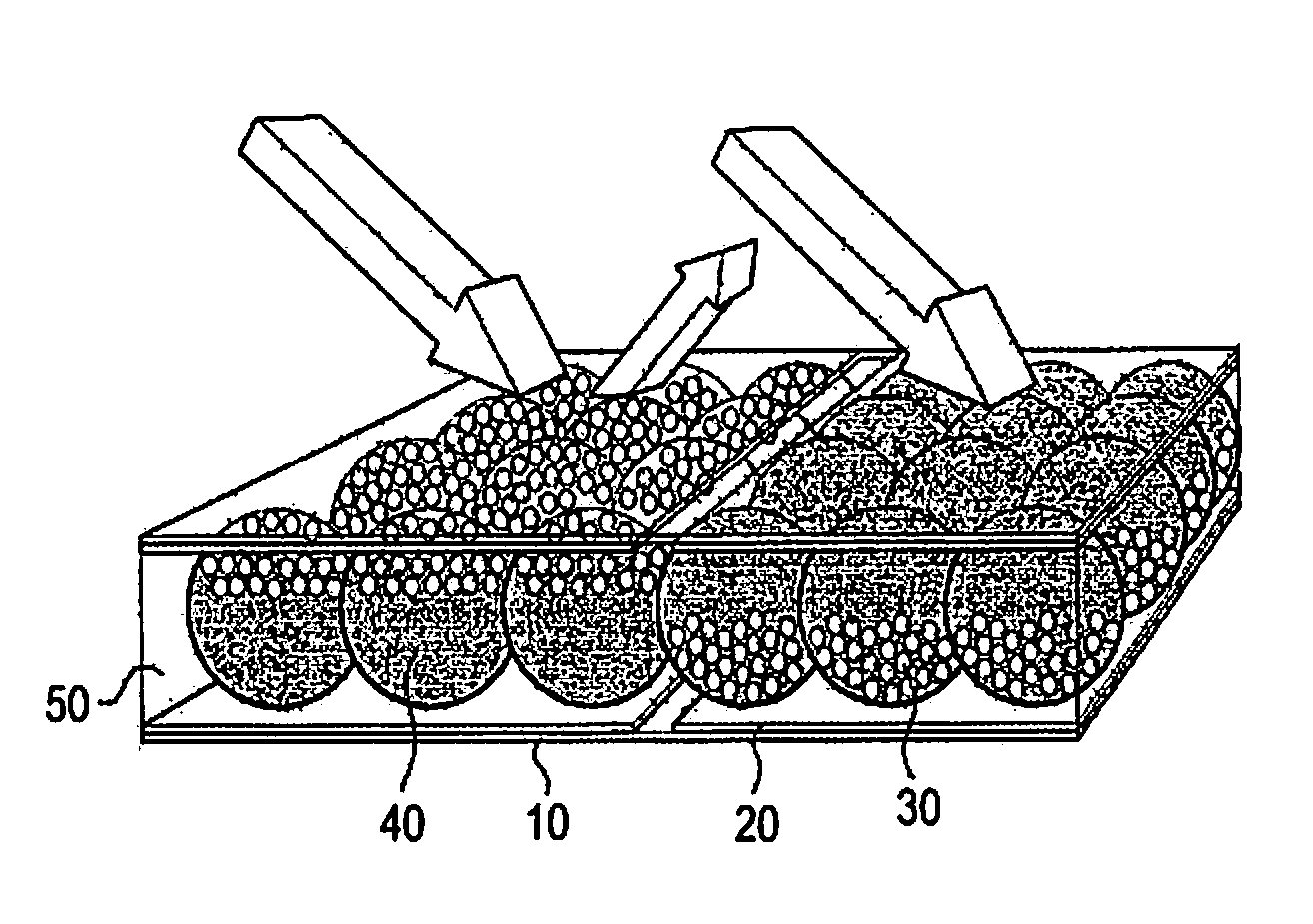

InactiveUS20150022766A1Improve reliabilityAvoid flowNon-linear opticsLiquid-crystal displayTransistor

A liquid crystal display includes a first substrate and a second substrate which face opposite to each other, a thin film transistor disposed on the first substrate, a pixel electrode connected to the thin film transistor, a first light blocking member disposed on the pixel electrode, and a cover layer disposed on the first light blocking member and covering the first light blocking member.

Owner:SAMSUNG DISPLAY CO LTD

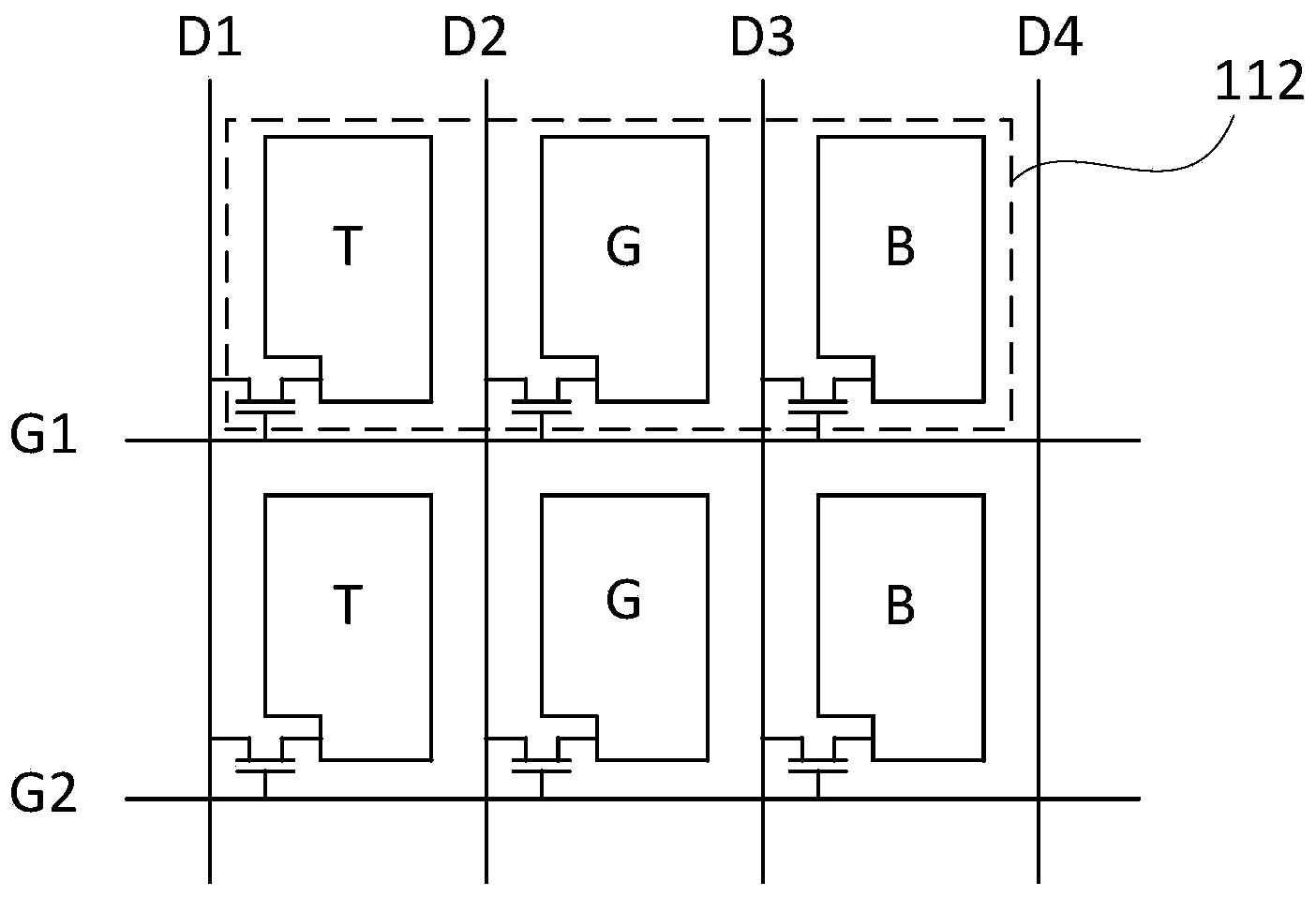

Lcd device and drive method thereof

ActiveCN101364021AImprove the display effectEliminate afterimageStatic indicating devicesNon-linear opticsLiquid-crystal displayScan line

The invention discloses an LCD (liquid crystal display) including scan lines, data lines arranged across the scan lines, and pixel electrodes and transistors arranged in pixel areas formed by mutual cross of the scan lines and the data lines. The pixel electrode in each pixel area includes a first sub-pixel electrode and a second sub-pixel electrode, and the transistor in each pixel area includes a first transistor connected with the first sub-pixel electrode and a second transistor connected with the second sub-pixel electrode, wherein the grid electrodes of the first transistor and the second transistor are respectively and electrically connected with two adjacent scan lines, and the active electrodes respectively and electrically connected with the same data line. The invention further discloses a corresponding method for driving the LCD. The common voltage Vcom can be conveniently adjusted, and the ghost problem in the prior LCD can be improved by adopting the LCD and the driving method thereof.

Owner:KUSN INFOVISION OPTOELECTRONICS

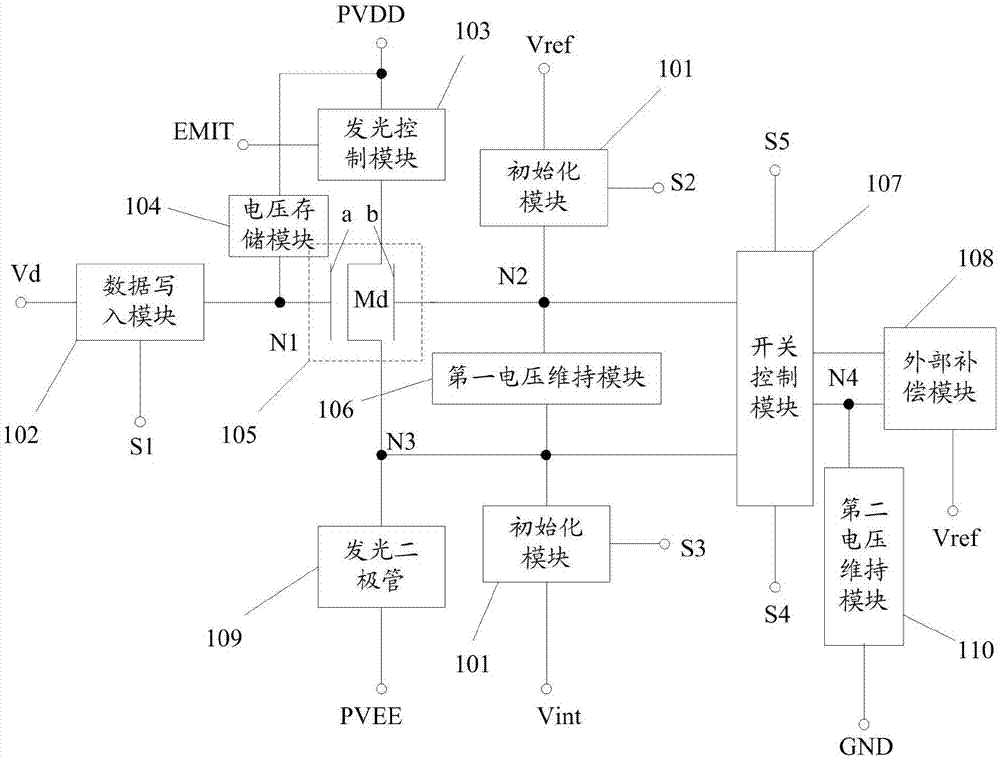

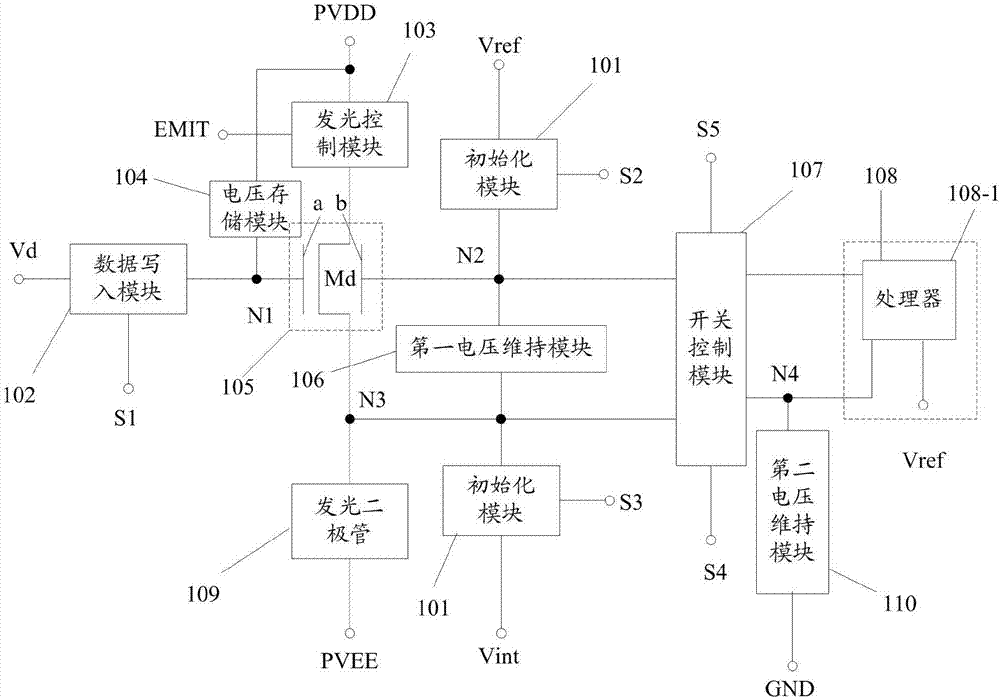

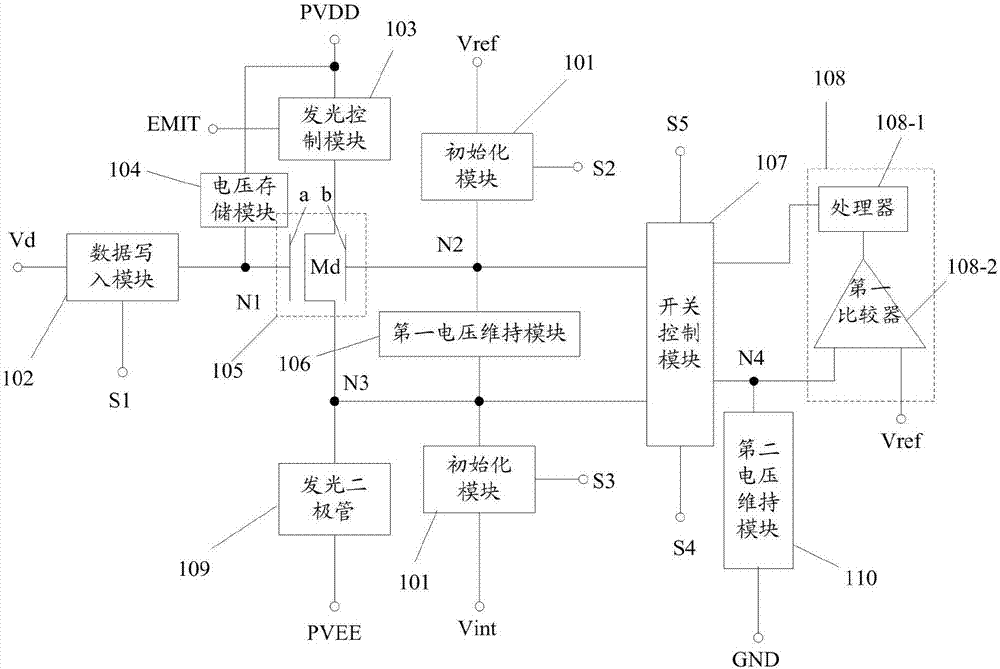

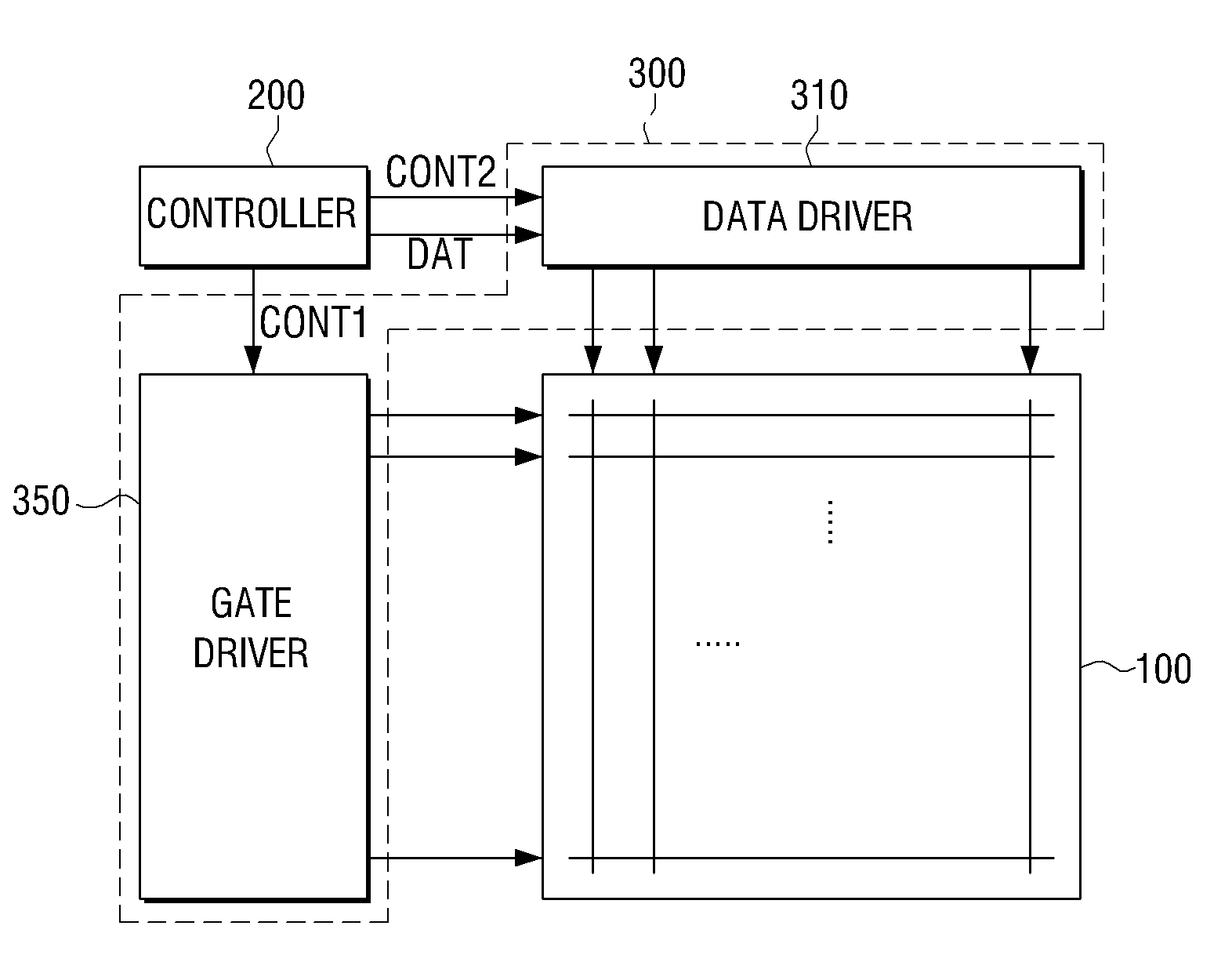

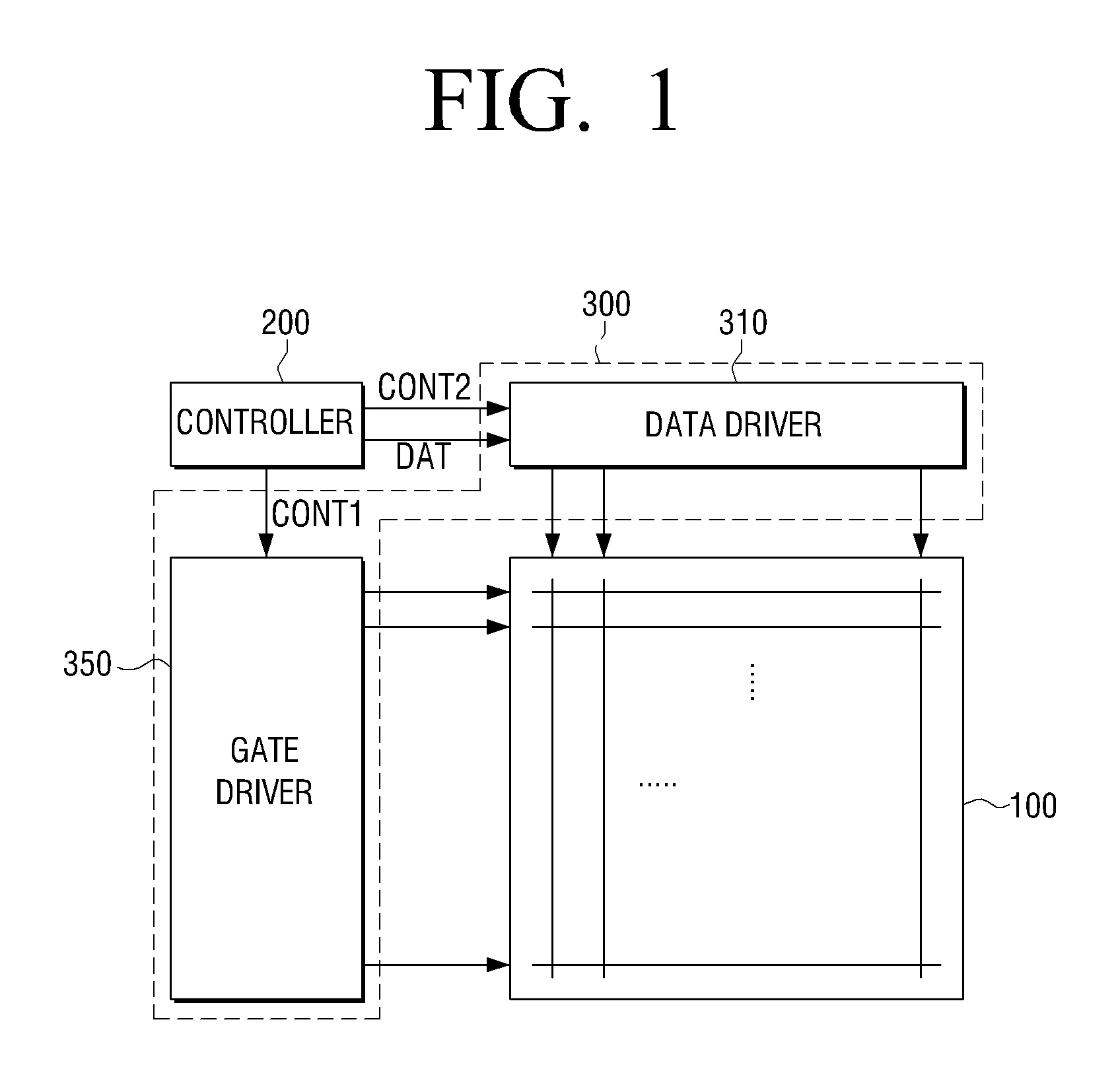

Pixel circuit and driving method thereof, electroluminescent display panel and display device

ActiveCN107358916AThreshold Voltage AdjustmentImpact sizeStatic indicating devicesSolid-state devicesDisplay deviceEngineering

The invention discloses a pixel circuit and a driving method thereof, an electroluminescent display panel and a display device. The pixel circuit comprises an initialization module, a data writing-in module, a light emitting control module, a voltage storage module, a driving transistor, a first voltage maintaining module, a switch control module, an external compensation module and a light-emitting diode. The driving transistor is a double-gate transistor; and a second gate of the double-gate transistor is electrically connected with the external compensation module through the switch control module. Under the control of the switch control module, the external compensation module collects the voltage of a third node and then provides a compensation voltage for a second node so as to realize adjustment of the threshold voltage of the dual-gate transistor, so that the threshold voltage of the dual-gate transistor is close to a standard threshold voltage and the current of the light-emitting diode during light emitting is be independent of the threshold voltage. Therefore, a phenomenon that the current is affected by the drift of the threshold voltage is avoided; and the residual image is eliminated to improve the quality of the displayed picture.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

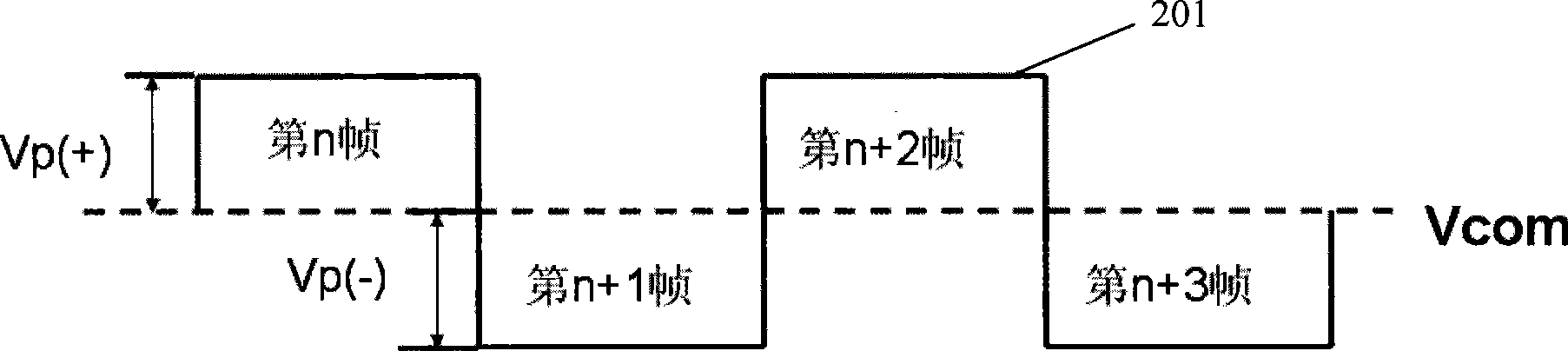

Liquid crystal display apparatus and driving method thereof

ActiveUS20110050753A1Eliminate afterimageEffectively eliminating a residual image phenomenonCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayElectrical polarity

A liquid crystal display (LCD) apparatus and a method of driving the LCD apparatus are provided. The LCD apparatus includes a panel unit including at least one pixel having a plurality of sub-pixels and a controller which inserts gray data into at least one pixel of the plurality of sub-pixels based on a frame period and a polarity of a liquid crystal of the at least one pixel.

Owner:SAMSUNG ELECTRONICS CO LTD

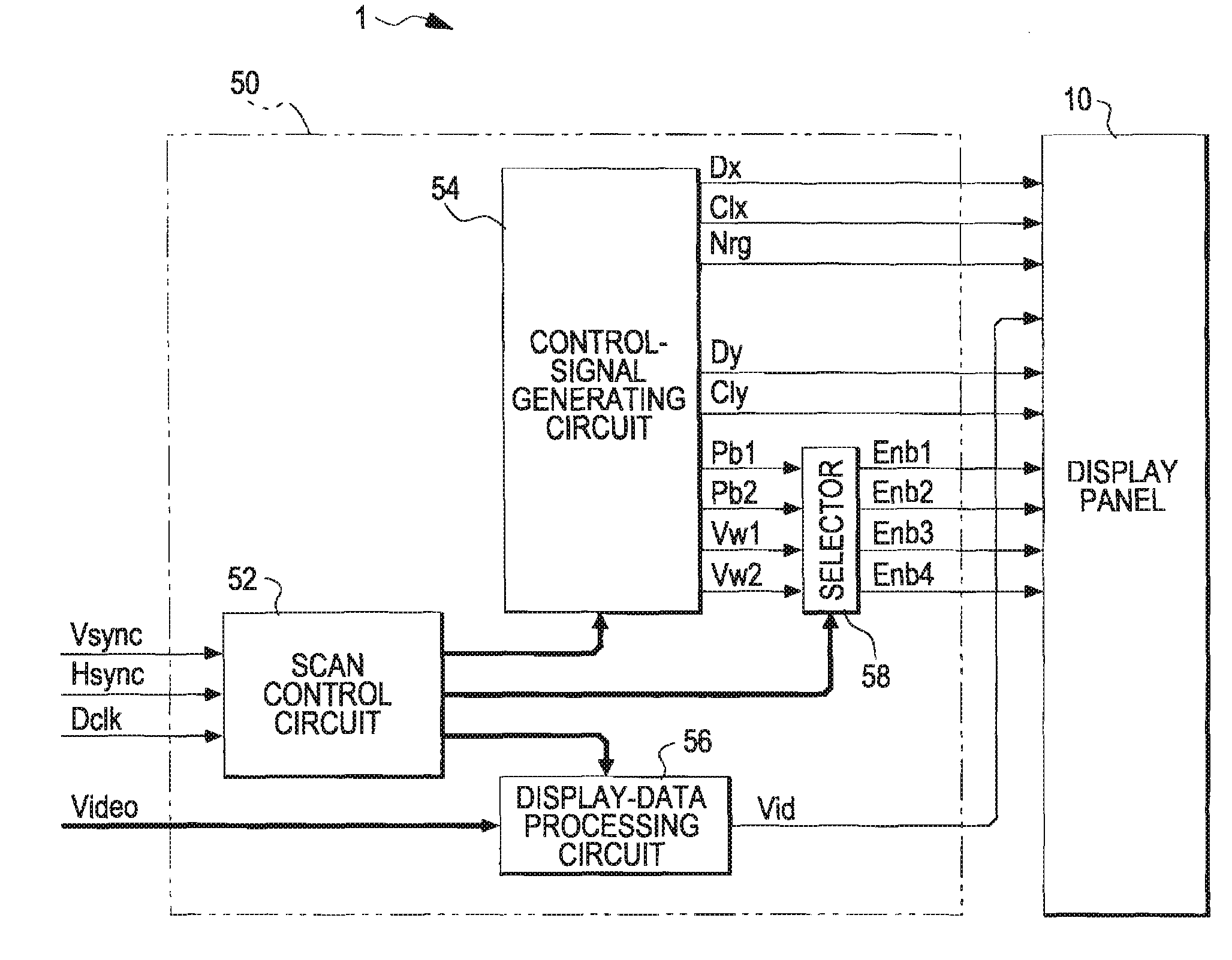

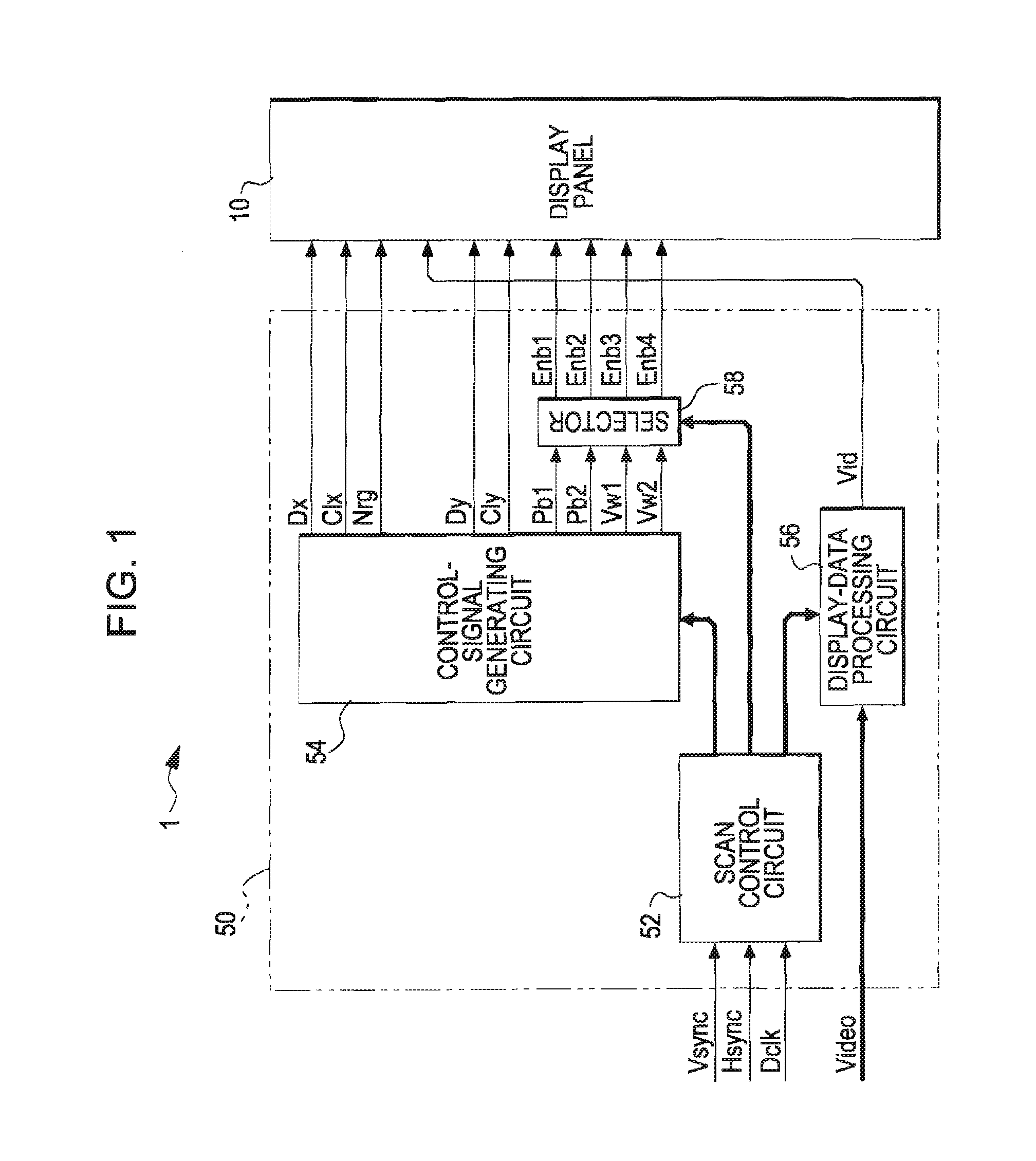

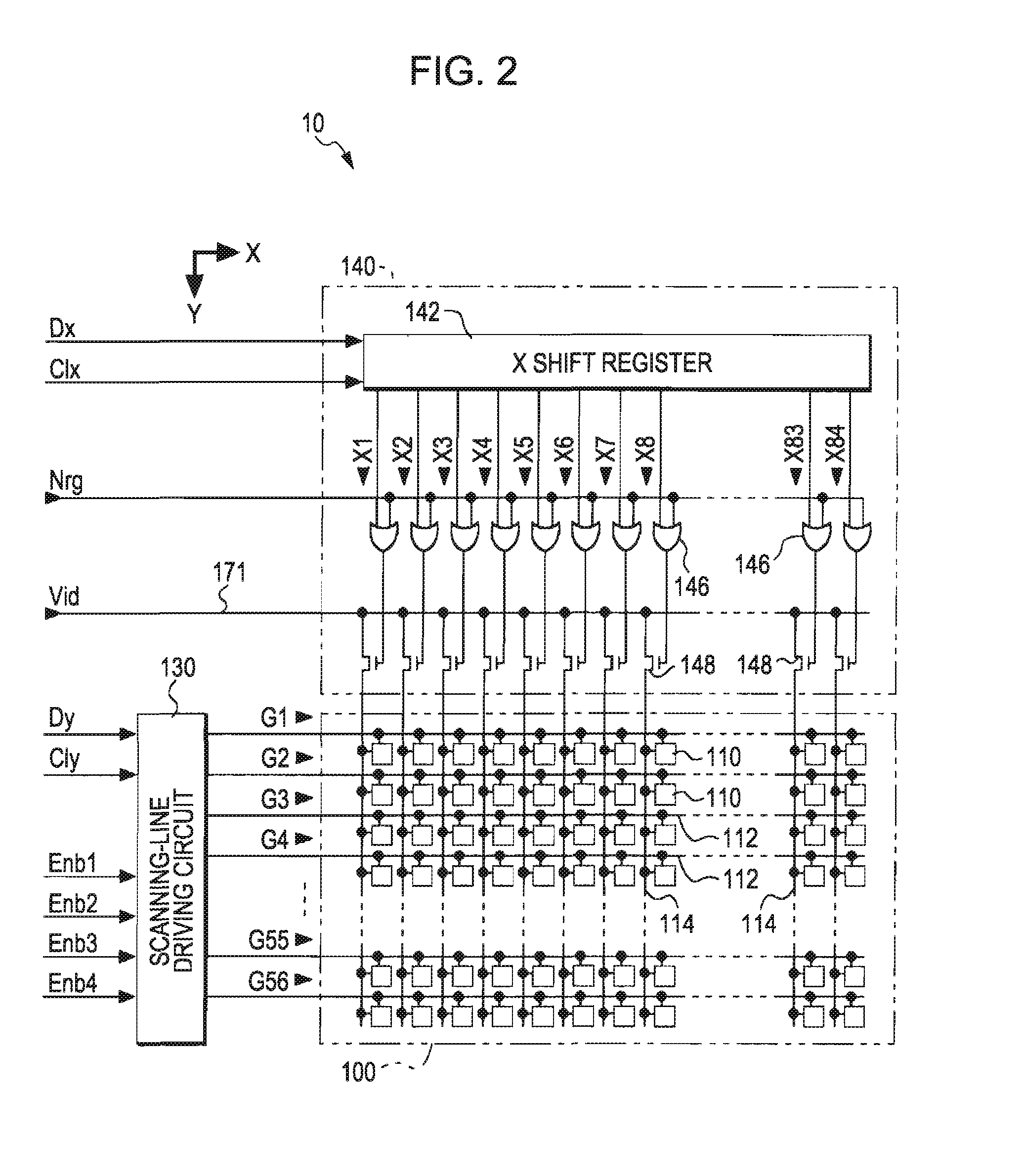

Electrooptic device, scanning-line driving circuit, method for driving the same, and electronic device

InactiveUS8063875B2Reduce the differenceShort timeColor television detailsCathode-ray tube indicatorsEngineeringElectron

Owner:SEIKO EPSON CORP

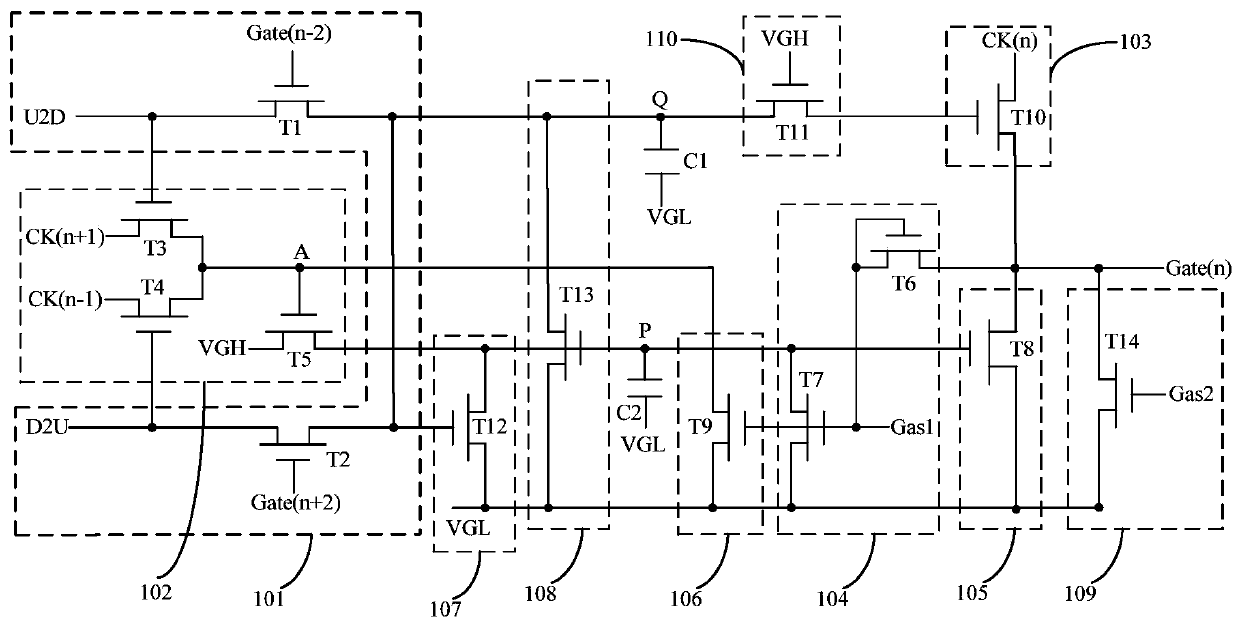

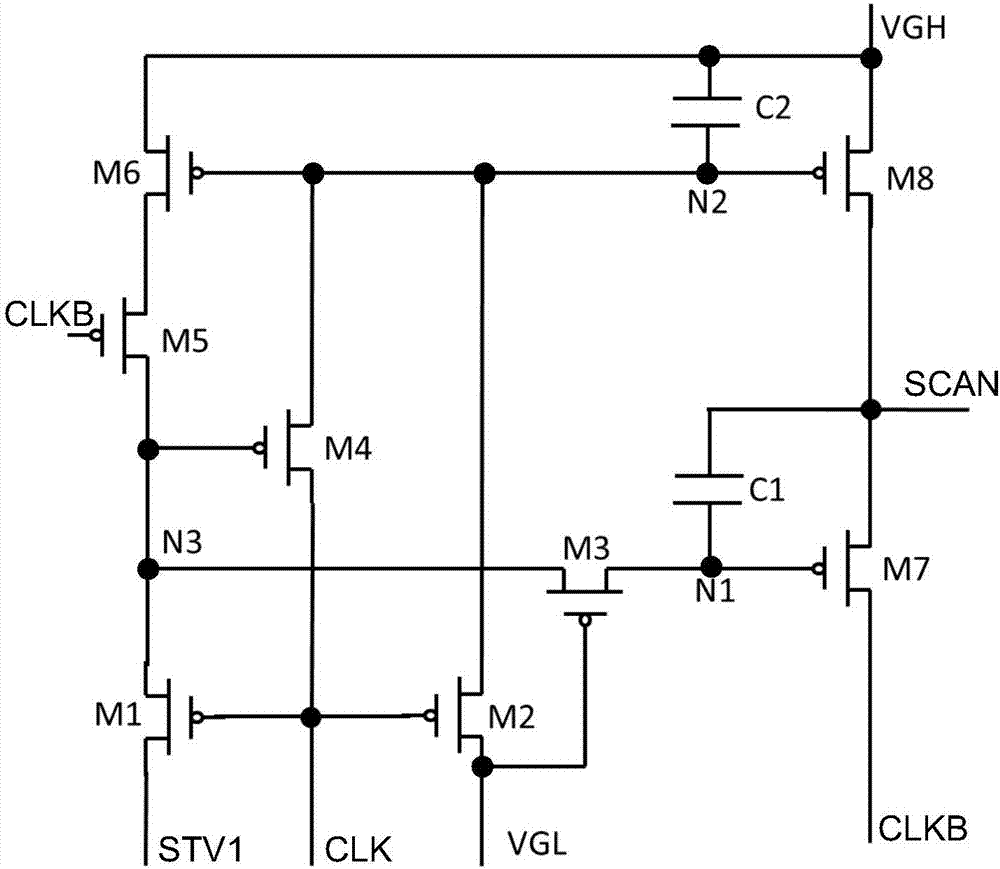

GOA circuit

InactiveCN107767834AAvoid under-openingPotential pull downStatic indicating devicesLiquid-crystal displayControl signal

The invention provides a GOA circuit including m cascaded GOA units. The n-th GOA unit includes: an output control module, a forward and reverse scan control module, a node signal control circuit, a second pull-down circuit, a first pull-down circuit, and a pull-up circuit. The forward and reverse scan control module controls the GOA circuit to perform forward scanning or reverse scanning. The output control module controls the outputting of the n-th gate drive signal. The first pull-down circuit includes a seventh TFT. The second pull-down circuit includes a fifth TFT. The node signal controlcircuit controls the on-off state of the fifth TFT. The pull-up circuit includes an eighth TFT. After a liquid crystal display panel is powered off, a first global control signal is a low-level signal. The GOA circuit can eliminate a residual image appearing during the abnormal power-off of the liquid crystal display panel and improves user experience.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

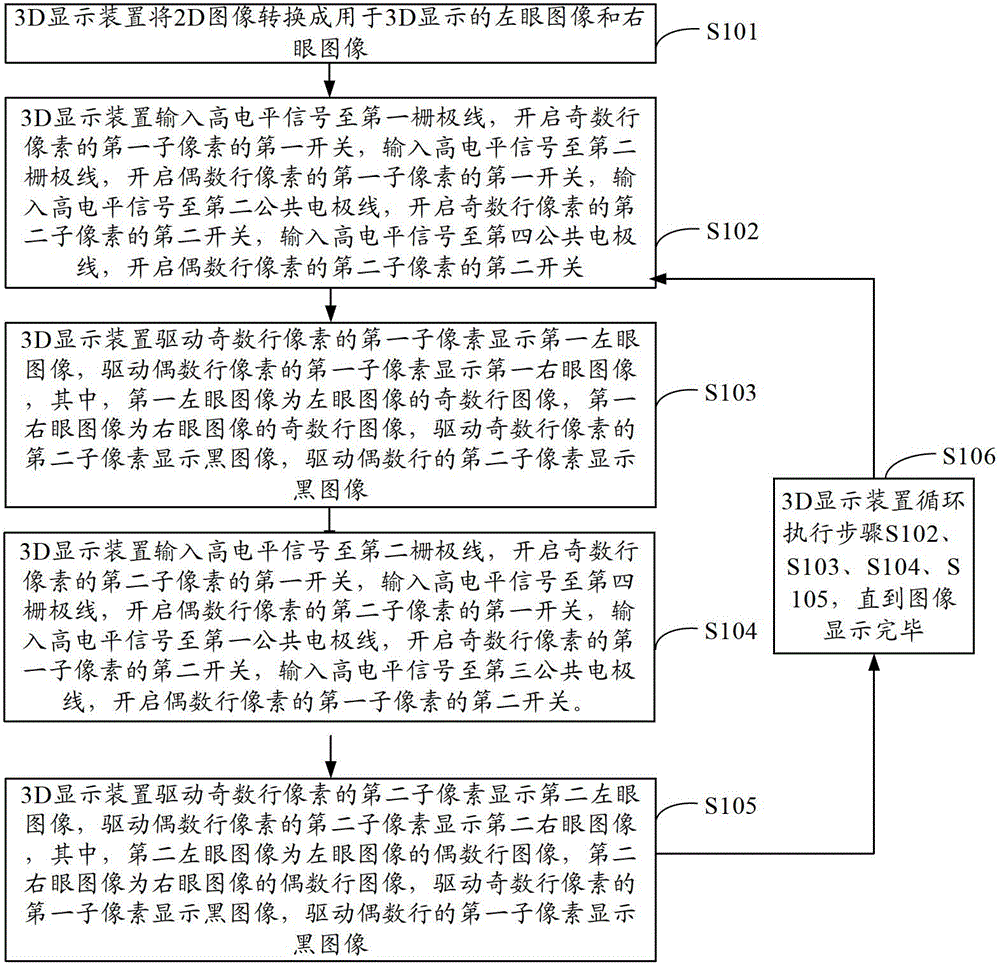

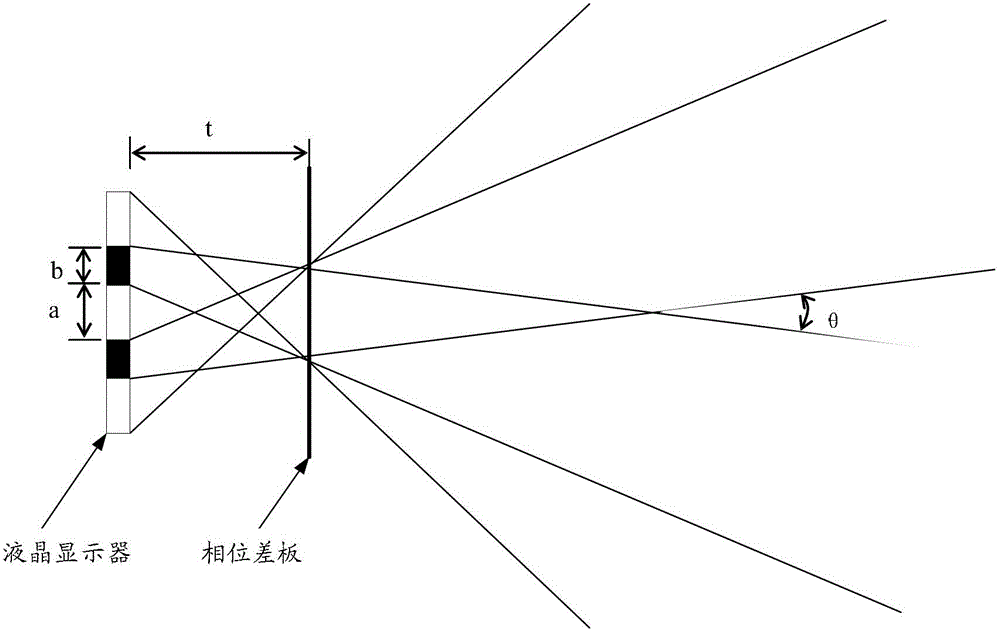

3D (Three-dimensional) display method and display device

InactiveCN102752617AReduce power consumptionLarge viewing angleStatic indicating devicesSteroscopic systems3 d displayDisplay device

The embodiment of the invention discloses a 3D (Three-dimensional) display method and a display device, relating to the technical field of 3D display and aiming at enlarging a visual angle of a 3D display panel in the vertical direction and reducing the power consumption. The method comprises the following steps: step a, driving a first sub-pixel of an odd-numbered line pixel to display a first left eye image, driving a first sub-pixel of an even-numbered line pixel to display a first right eye image, driving a second sub-pixel of the odd-numbered line pixel to display a second left eye image, and driving a second sub-pixel of the even-numbered line to display a dark image; and step b, driving a second sub-pixel of the odd-numbered line pixel to display a second left eye image, driving a second sub-pixel of the even-numbered line pixel to display a second right eye image, wherein the second left eye image is the even-number line image of the left eye image, the second right eye image is the even-numbered line image of the right eye image; driving the first sub-pixel of the odd-numbered line pixel to display the dark image; and driving the first sub-pixel of the even-numbered line to display the dark image; and executing the steps a and b circularly until the image is displayed completely.

Owner:BOE TECH GRP CO LTD

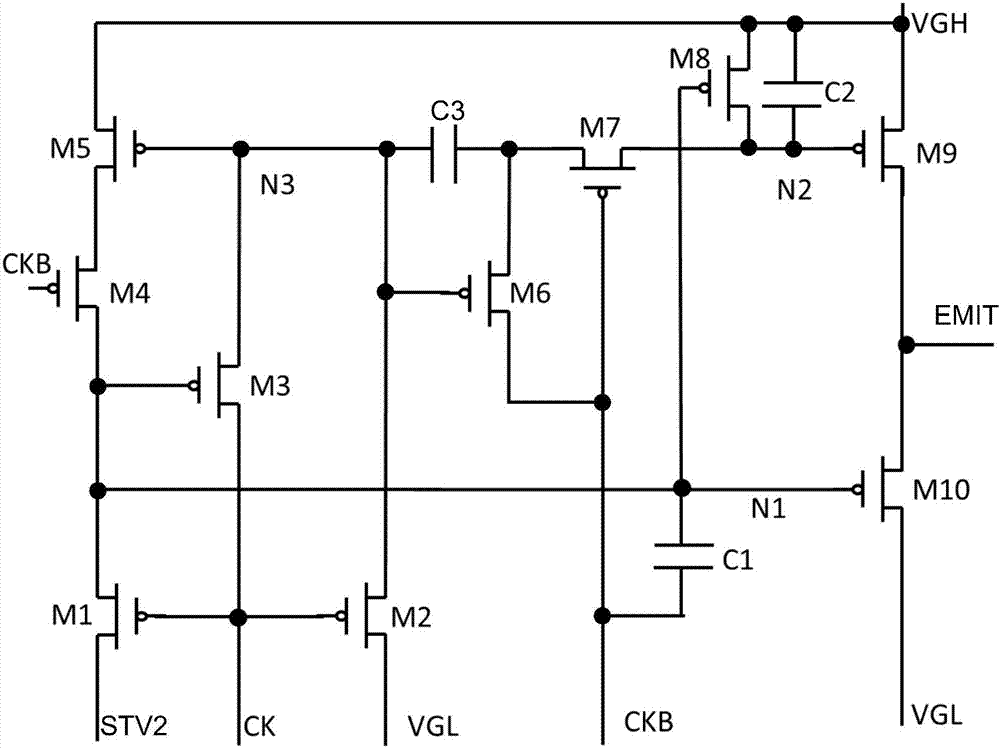

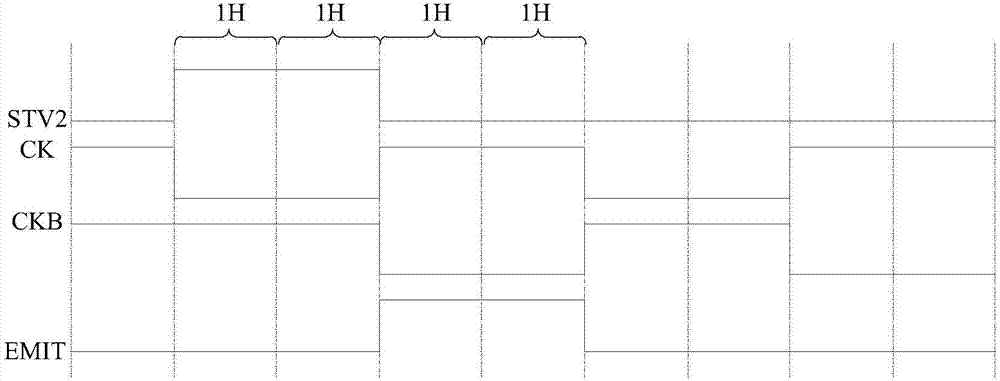

Organic electroluminescent display panel, driving method thereof and display device

ActiveCN107481667AEliminate afterimageFast response timeStatic indicating devicesDigital storagePorchOrganic electroluminescence

The invention discloses an organic electroluminescent display panel, a driving method thereof and a display device, driving in a dimming mode and dividing the scanning time for each frame into the display area scanning time and the front and back porch time. In the display area scanning time, the pixel circuits in the display area of the organic electroluminescent display panel can be scanned, and the driving circuit adjusts in the front and back porch time. By controlling the front and back porch time, and under the condition of guaranteeing the front and back porch time to be less than the display area scanning time, the front and rear porch time is guaranteed to be a common multiple of each clock signal period in the gating drive circuit of the organic electroluminescent display panel, so that the switching between the front and rear porch time and the display area scanning time does not cross the clock signal cycles to ensure the integrity of the clock signal cycles in different time periods. Therefore, the problem of inconsistencies in display brightness caused by the disorder of the generated driving signal caused by the incomplete clock signal cycles in different time periods can be prevented.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

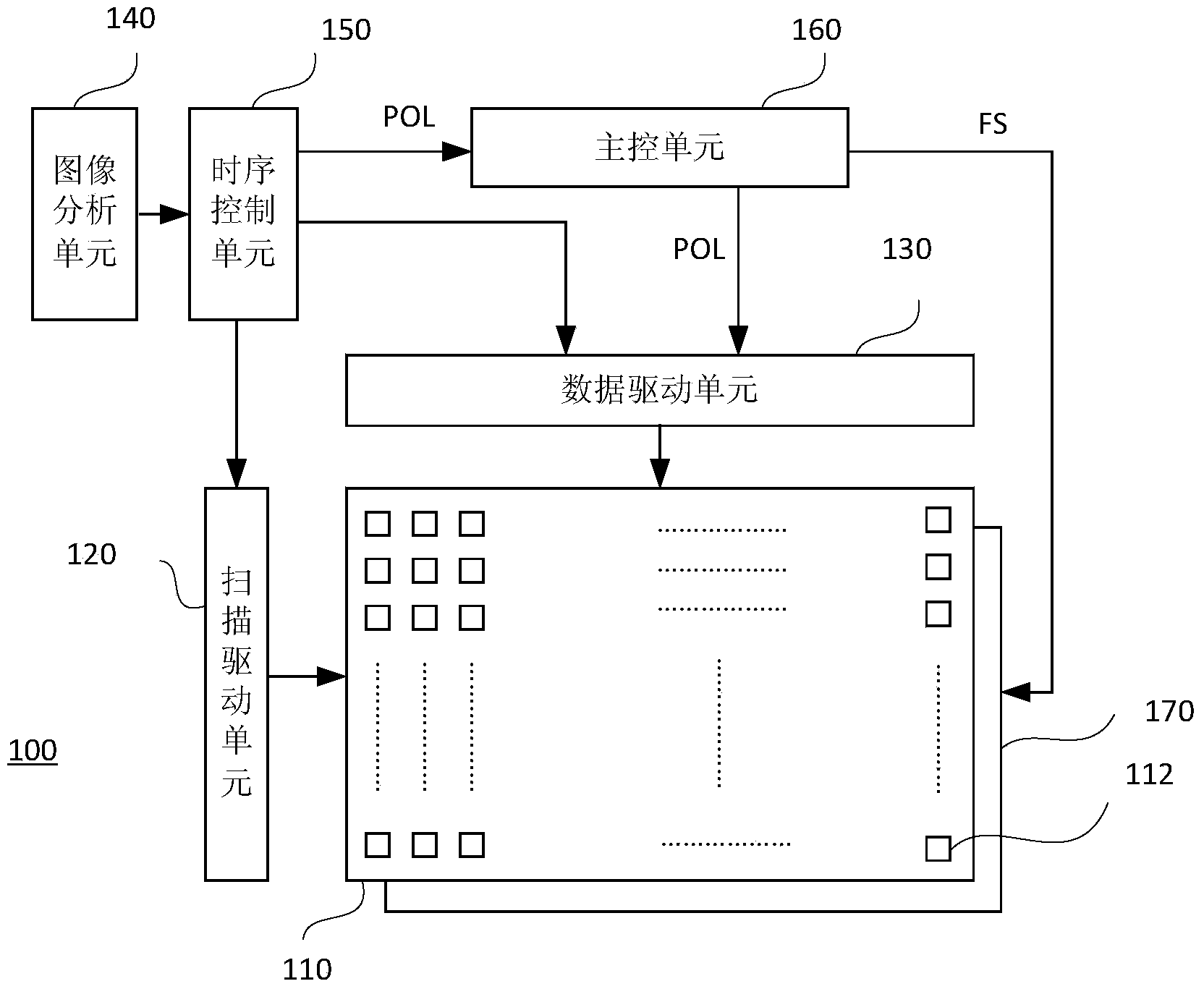

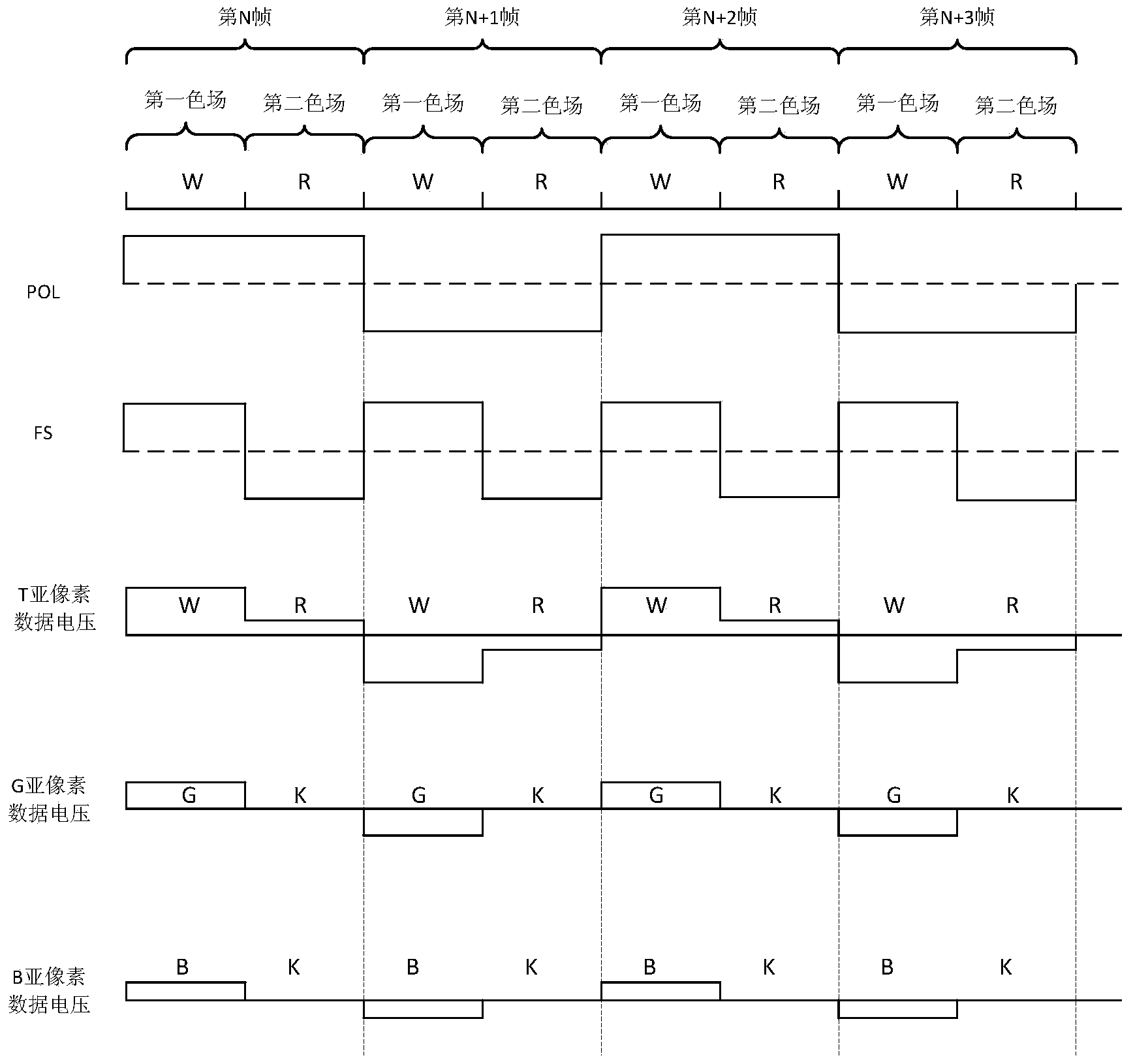

Field sequential liquid crystal display driving method and display device

The invention discloses a field sequential liquid crystal display driving method and a display device. The method comprises steps of providing a color field sequential signal to enable a backlight module to generate a plurality of color fields in one frame period respectively and providing a data driving signal to each sub-pixel unit of one pixel in the condition when each color field is effective respectively so as to open the sub-pixel unit corresponding to the color field, wherein polarity of the data driving signal is reversely rotated periodically to enable the voltage waveform to be symmetrical in relative to common reference voltage.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

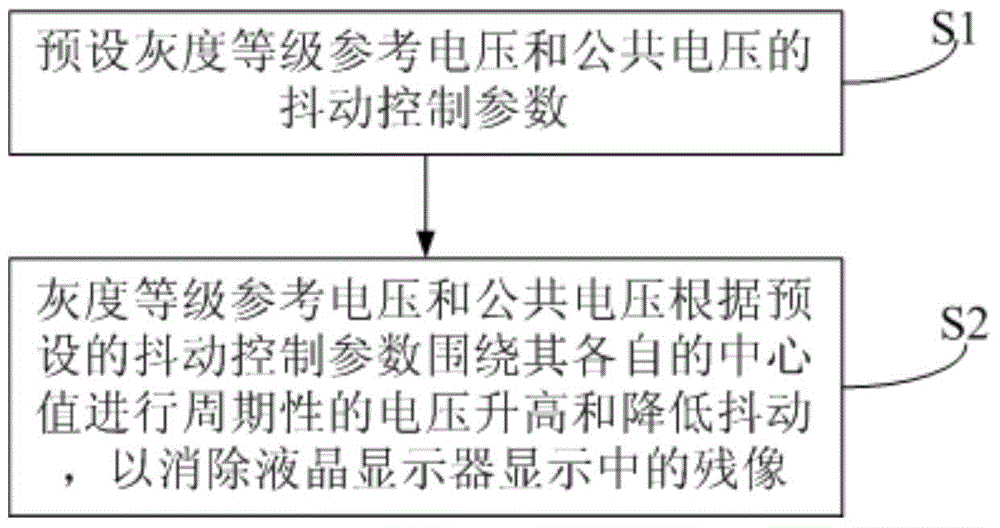

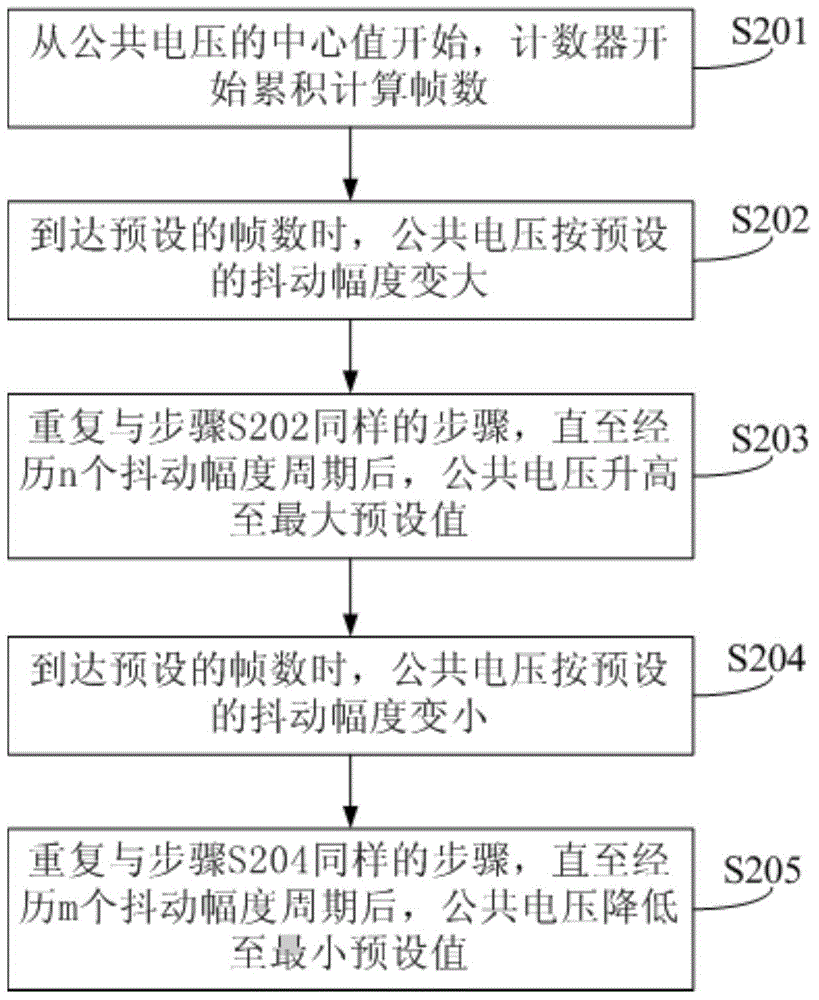

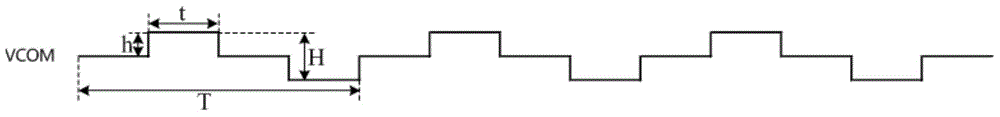

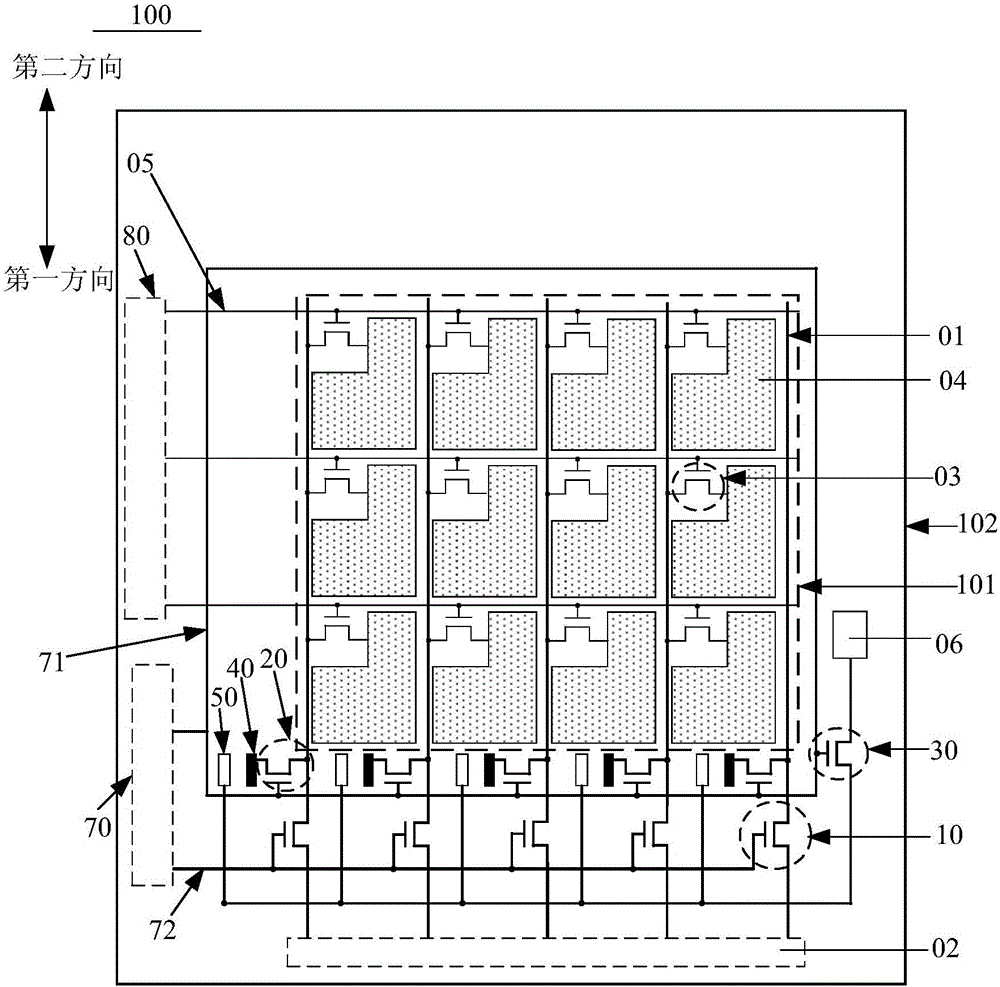

Residual image elimination method, drive system and display device

InactiveCN105096894AImprove elimination effectJitter Control PreciseStatic indicating devicesLiquid-crystal displayDisplay device

The invention provides a residual image elimination method, a drive system and a display device. The residual image elimination method comprises the steps that gray scale level reference voltage and / or common voltage or gray scale voltage jitter control parameters are preset; and voltage boosting and / or jitter reducing are / is performed on gray scale level reference voltage and / or common voltage or gray scale voltage according to the preset jitter control parameters so that residual images displayed in a liquid crystal display can be eliminated. According to the residual image elimination method, jitter control of gray scale level reference voltage and / or common voltage or gray scale voltage is enabled to be more accurate so that the residual images displayed in the liquid crystal display can be eliminated, and the elimination effect of the residual images is enabled to be better. Normal display of the liquid crystal display is not influenced by the residual image elimination method.

Owner:BOE TECH GRP CO LTD +1

Display panel, display device and control method of display panel

ActiveCN106019735AEliminate the internal electric fieldEliminate afterimageStatic indicating devicesNon-linear opticsElectricityData lines

The embodiment of the invention provides a display panel, a display device and a control method of the display panel, and relates to the technical field of display. The problem of direct-current residual images in an LCD panel can be solved. The display panel comprises an array substrate and a cassette substrate, the array substrate comprises multiple data lines, and the array substrate or the cassette substrate comprises a public electrode. The data lines extend to a non-display area from a display area of the array substrate, and the data lines extending to the non-display area are electrically connected with a data drive circuit through turned-on first transistors. The array substrate further comprises multiple second transistors, multiple first conductive structures, at least one third transistor and multiple conductive structures in the non-display area. The first conductive structures and the second conductive structures are grounded, when the second transistors are turned on, the data lines are connected with the first conductive structures, and when the third transistors are turned on, the public electrode is connected with the second conductive structures. The control method is used for manufacturing the display panel.

Owner:BOE TECH GRP CO LTD +1

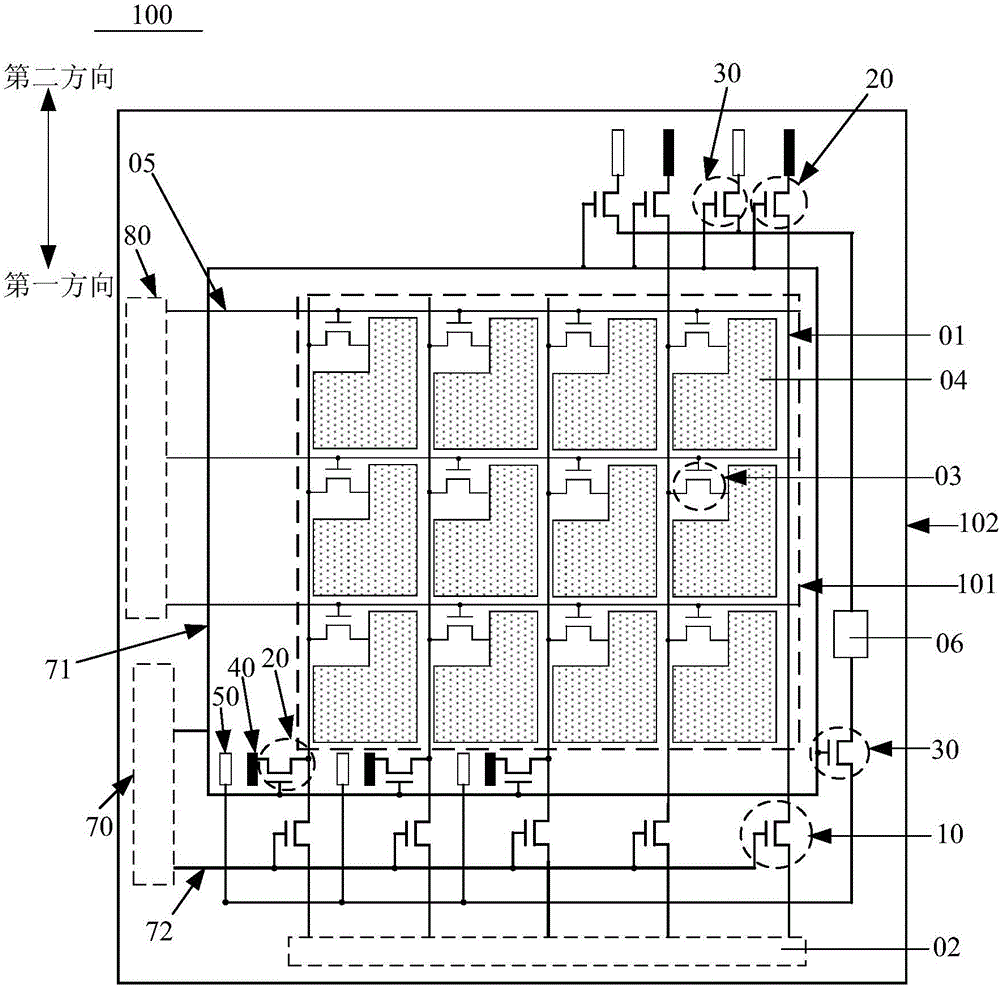

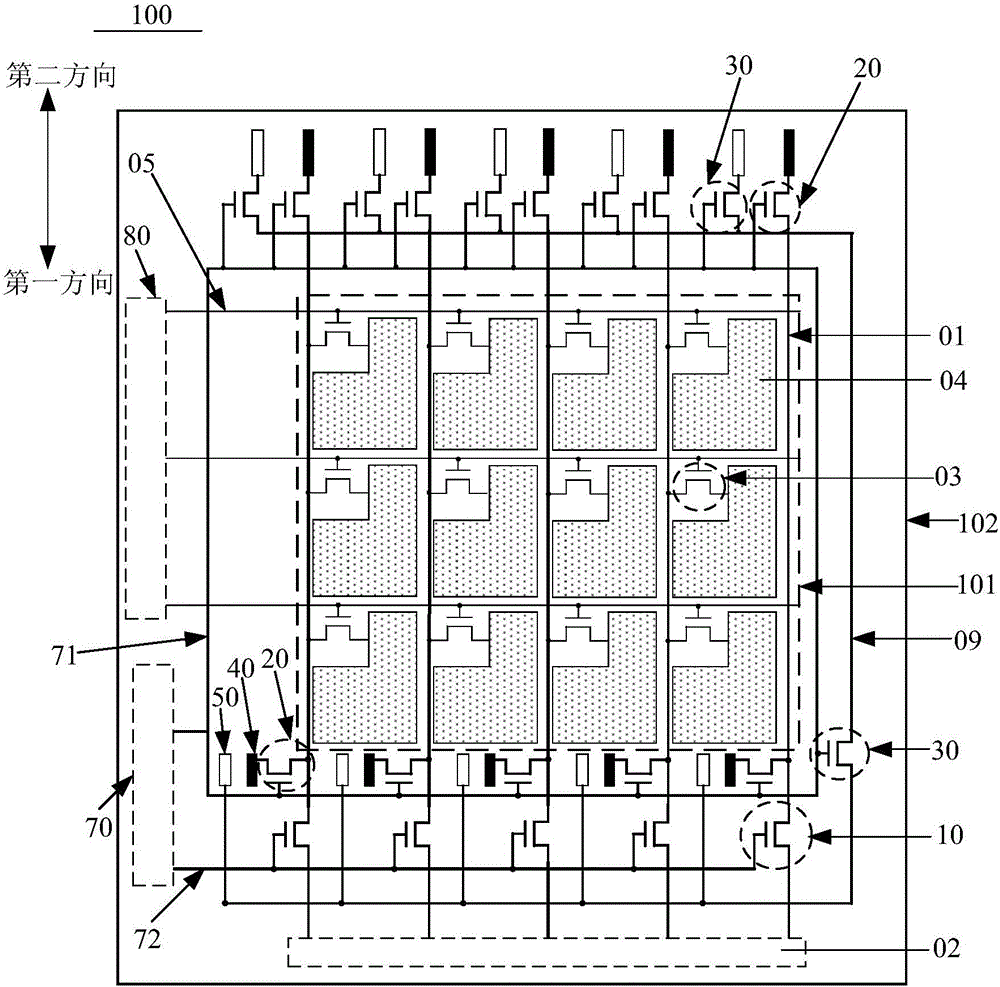

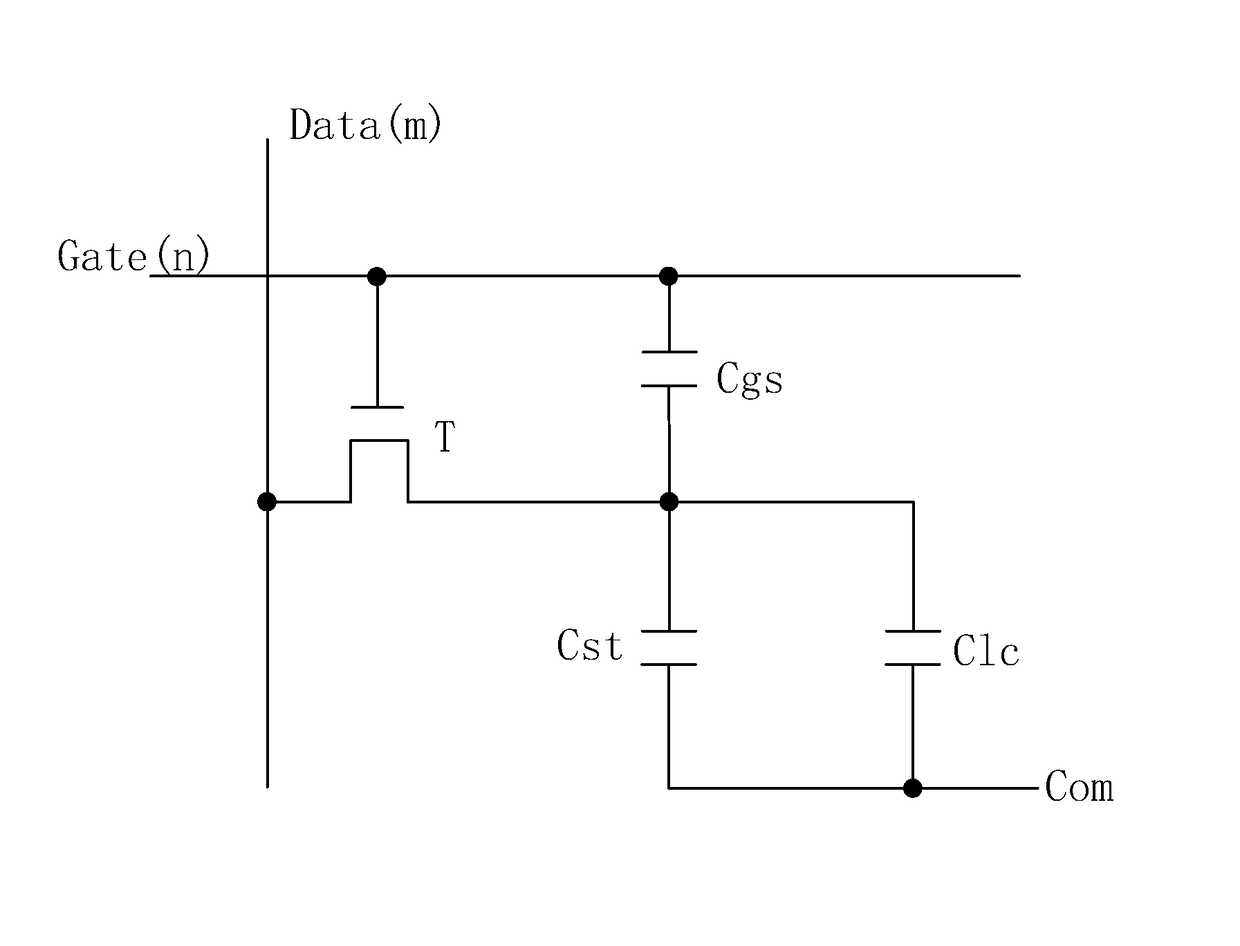

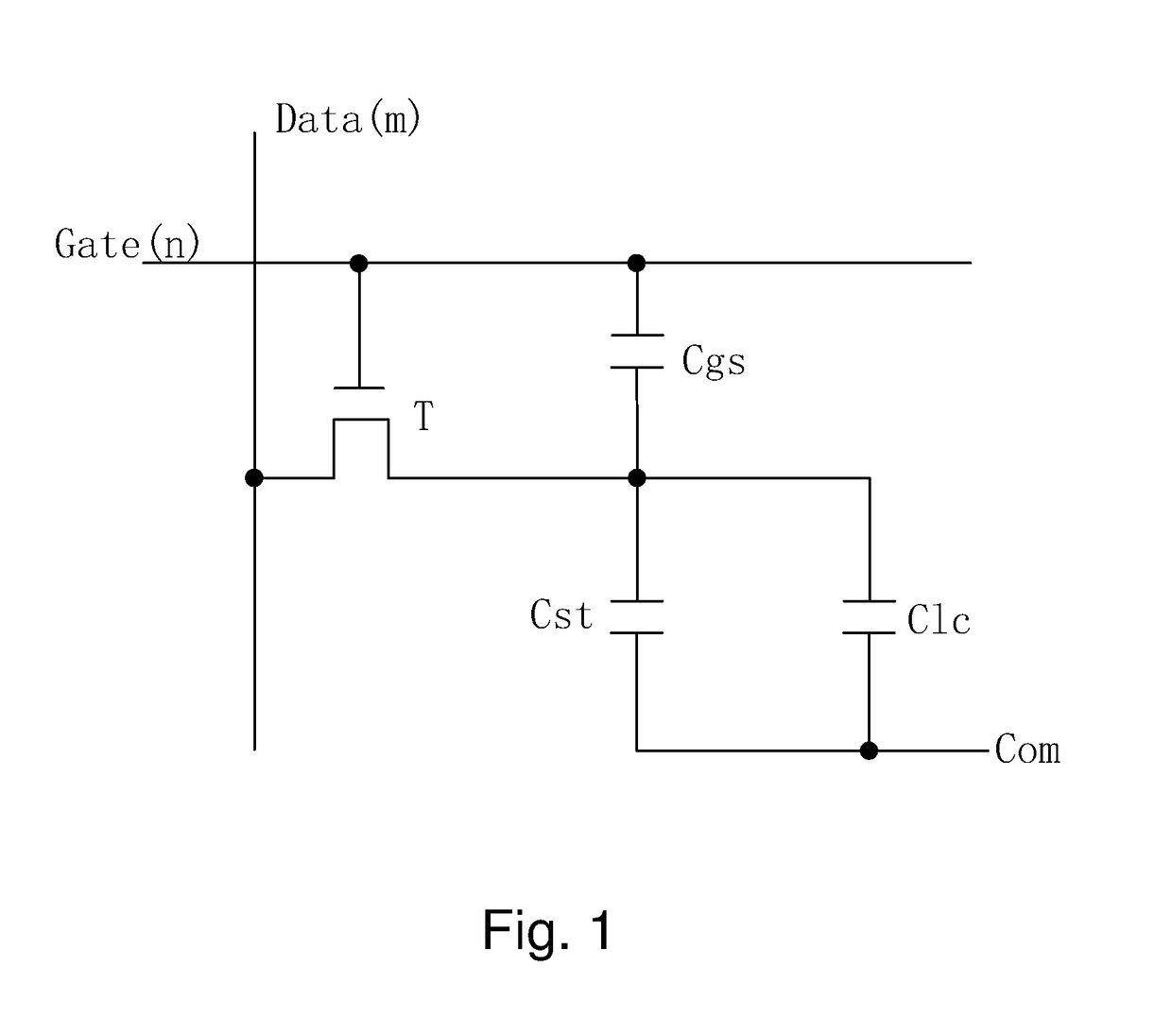

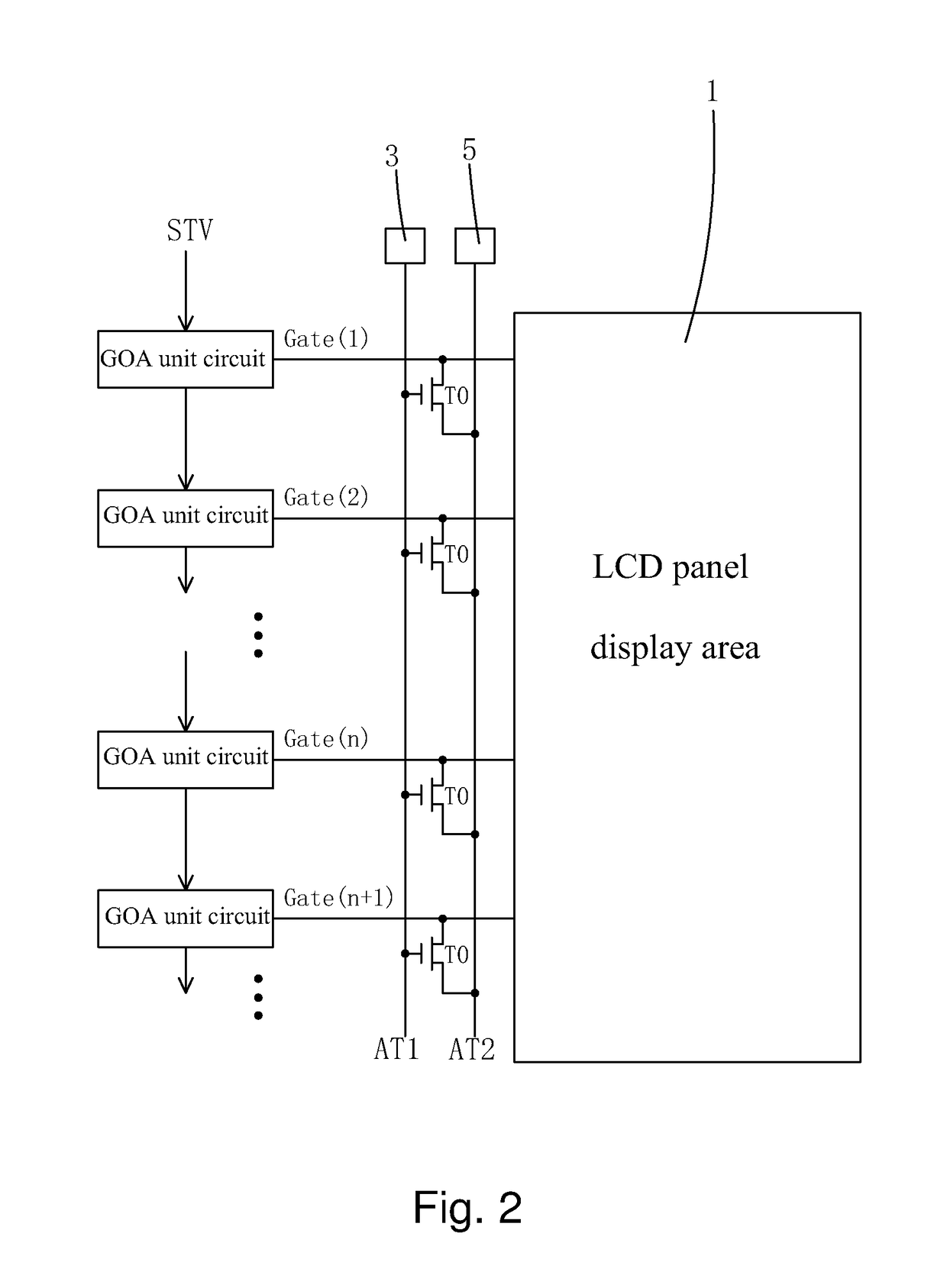

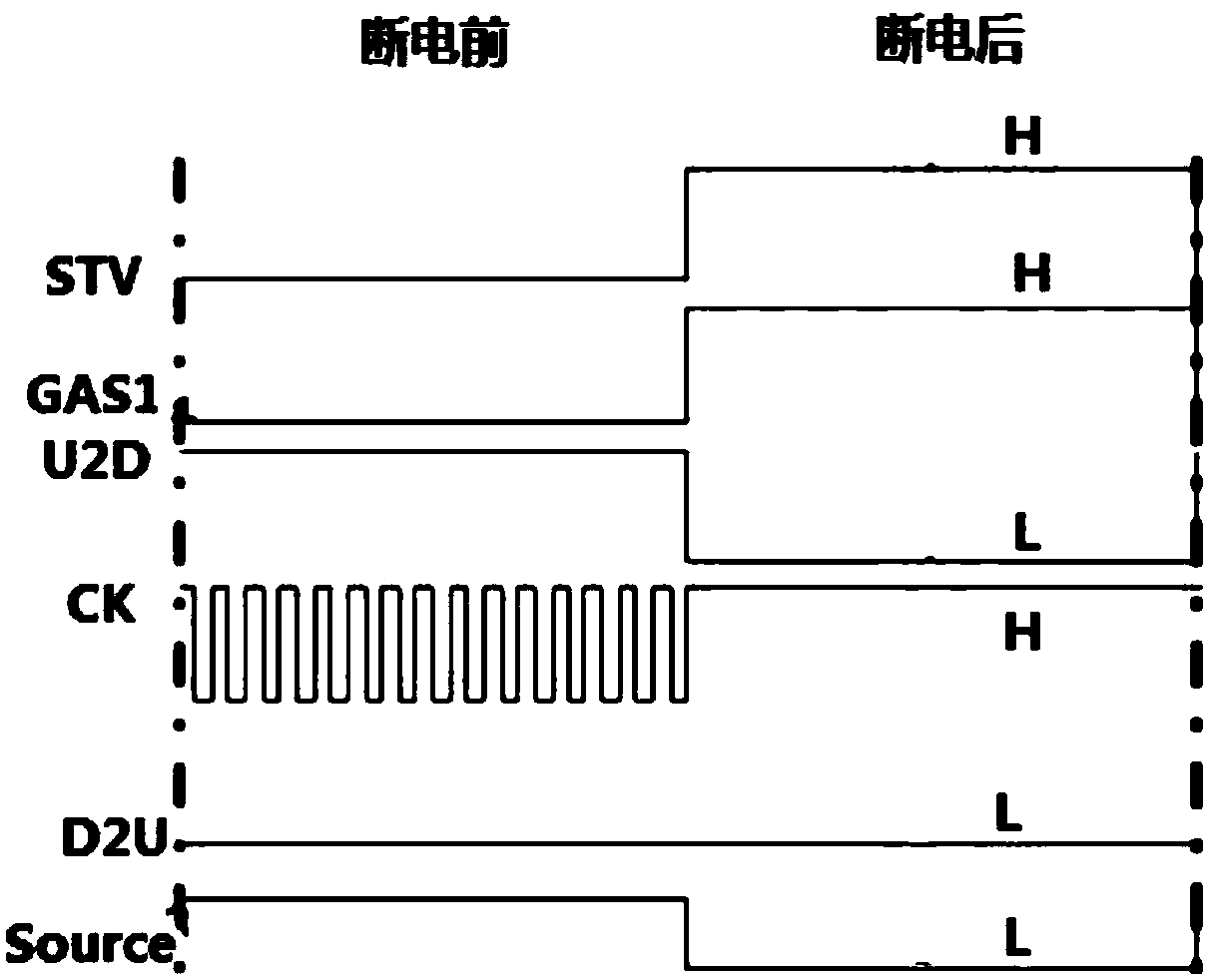

Common circuit for goa test and eliminating power-off residual images

The invention discloses a common circuit for GOA test and eliminating power-off residual images, including a first test end (3), a test signal line (AT1) connected to the first test end (3), a second test end (5), a feedback signal line (AT2) connected to the second test end (5), and the same number of test TFTs (T0) as cascade GOA unit circuits. By connecting the gate of each test TFT (T0) to test signal line (AT1), the source to feedback signal line (AT2) and the drain to the output end of corresponding GOA unit circuit and gate scan line, the invention can test the output signal of any stage GOA unit circuit to determine the location of a malfunctioning GOA unit circuit, and releasing the residual charges of the liquid crystal capacitor and storage capacitor at the display area of LCD panel when powering off to eliminate residual images.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

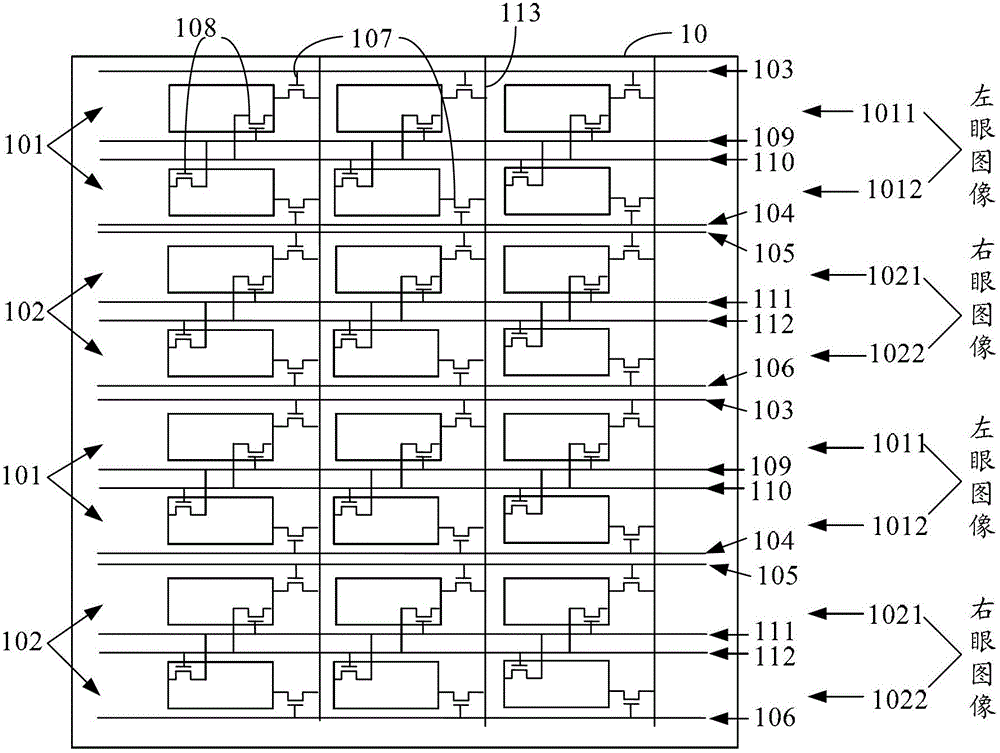

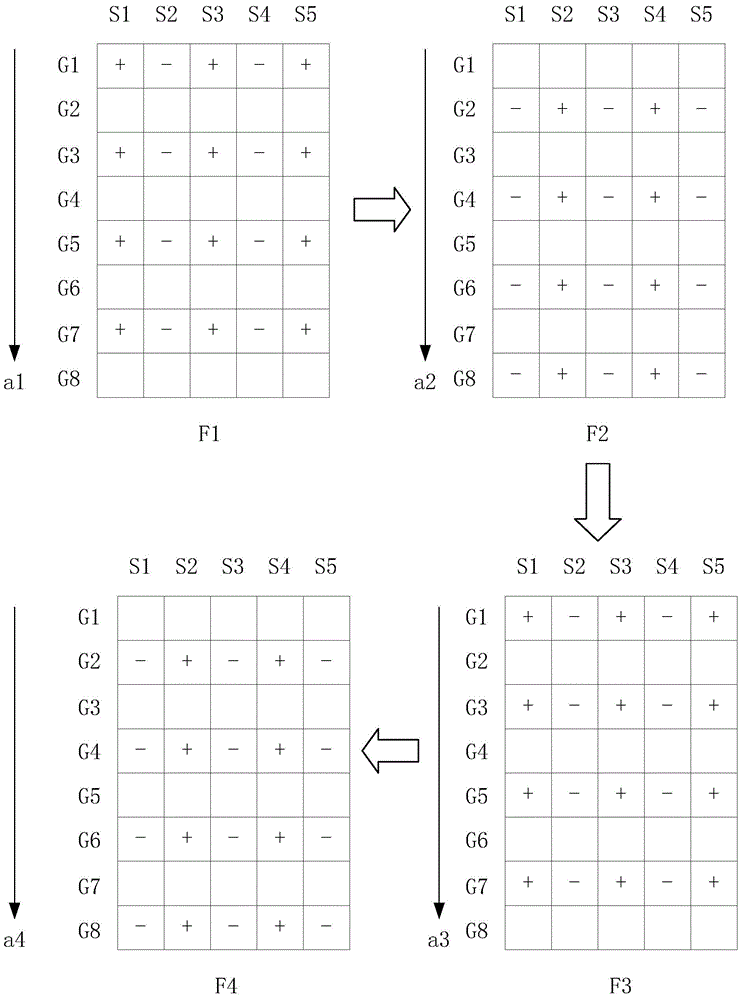

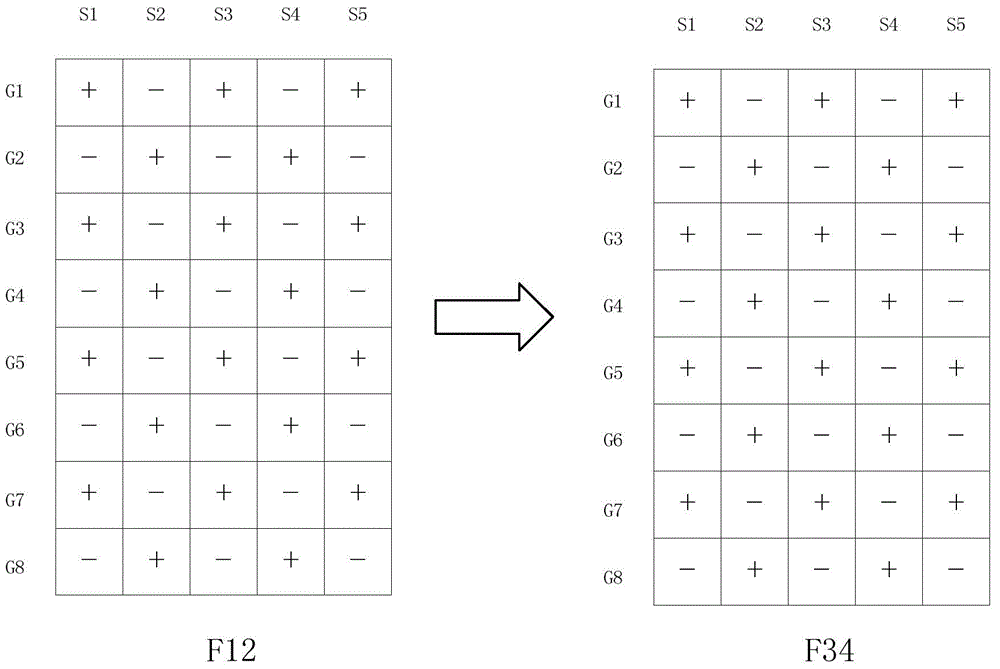

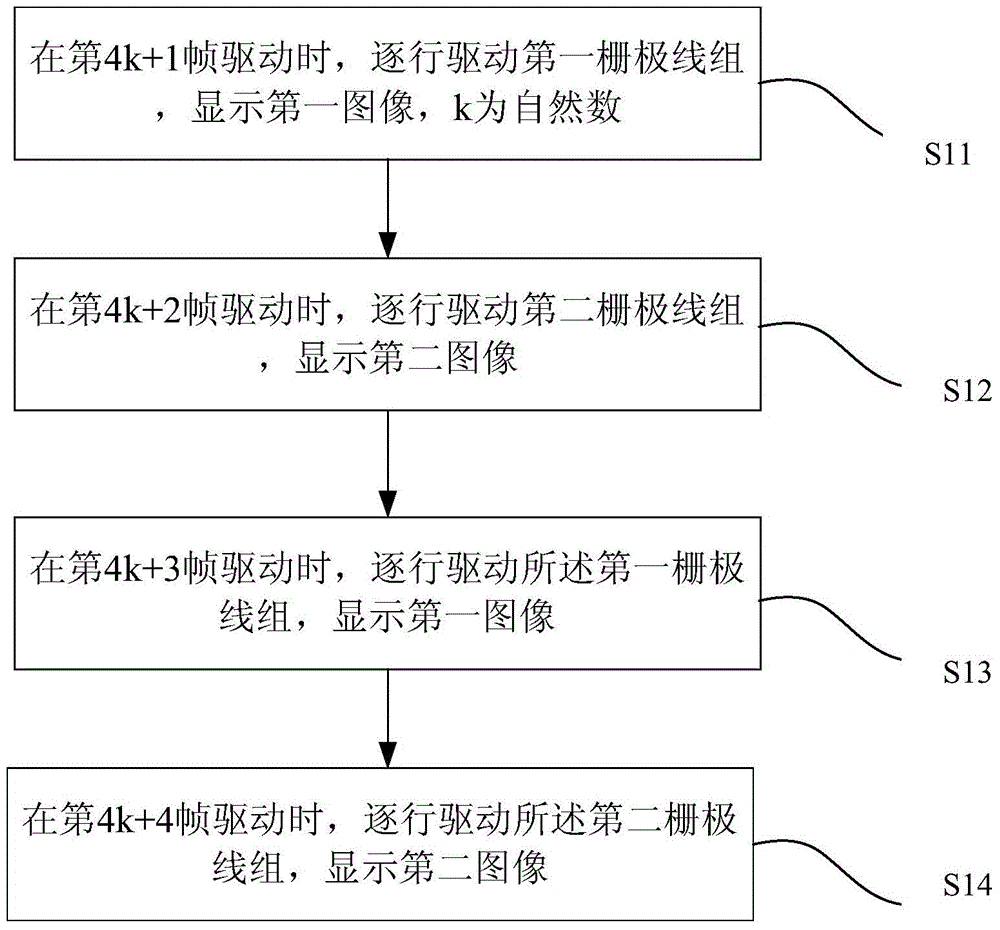

3D panel, driving method of 3D panel and electronic equipment

ActiveCN104410854AFlipEliminate afterimageStatic indicating devicesSteroscopic systems3d imageElectrical polarity

The invention discloses a 3D panel, a driving method of the 3D panel and electronic equipment. The driving method comprises steps as follows: during driving of a (4k+1) frame, a first grid line group is driven line by line, a first image is displayed, and k is a natural number; during driving of a (4k+2) frame, a second grid line group is driven line by line, and a second image is displayed; during driving of a (4k+3) frame, the first grid line group is driven line by line, and the first image is displayed; during driving of a (4k+4) frame, the second grid line group is driven line by line, and the second image is displayed; one of the first image and the second image is a left eye image, and the other is a right eye image; grid lines of the first grid line group and grid lines of the second grid line group are arranged alternately; scanning directions of the (4k+1) frame and the (4k+3) frame are opposite; and scanning directions of the (4k+2) frame and the (4k+4) frame are opposite. With the adoption of the driving method, charge polarities of pixel units of every two adjacent 3D images are turned, and the problem of ghost images is solved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

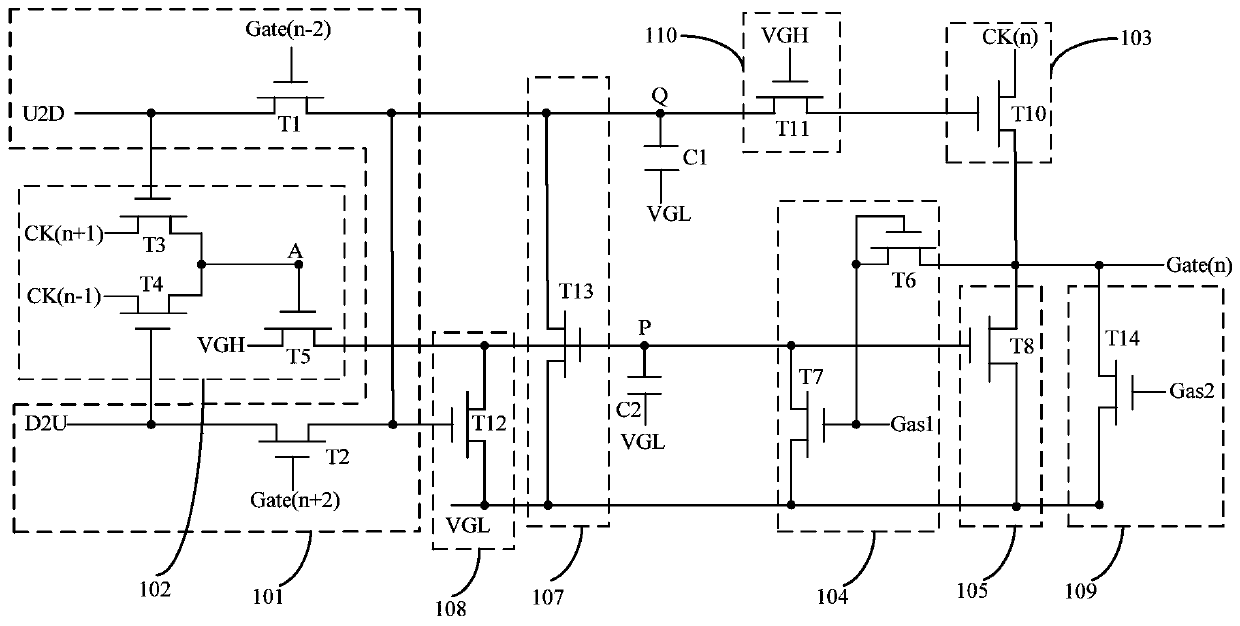

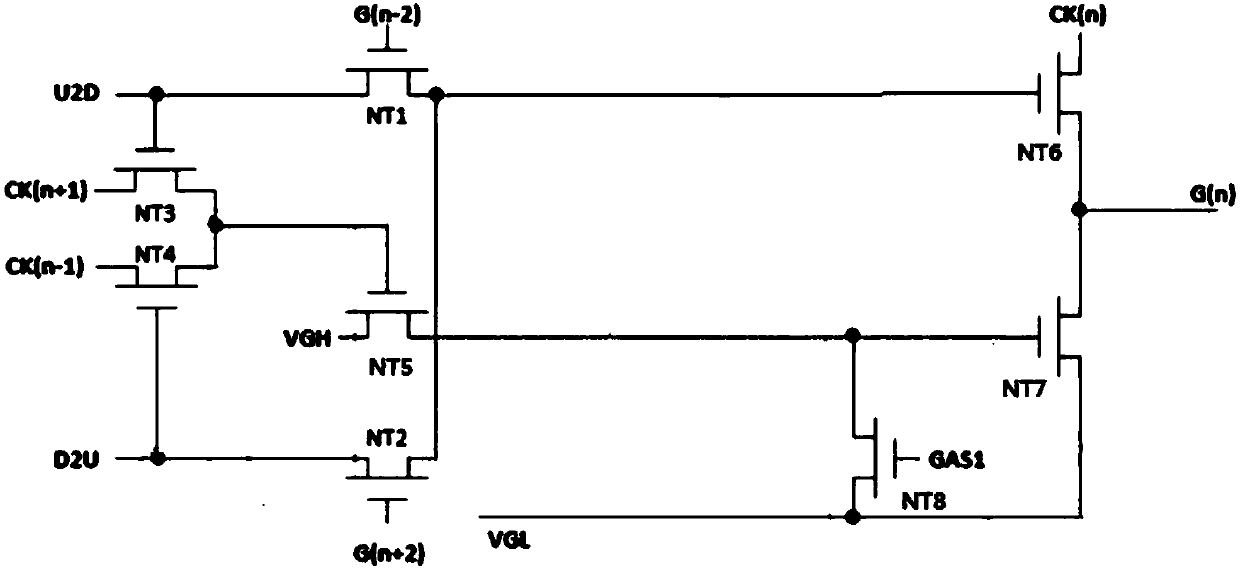

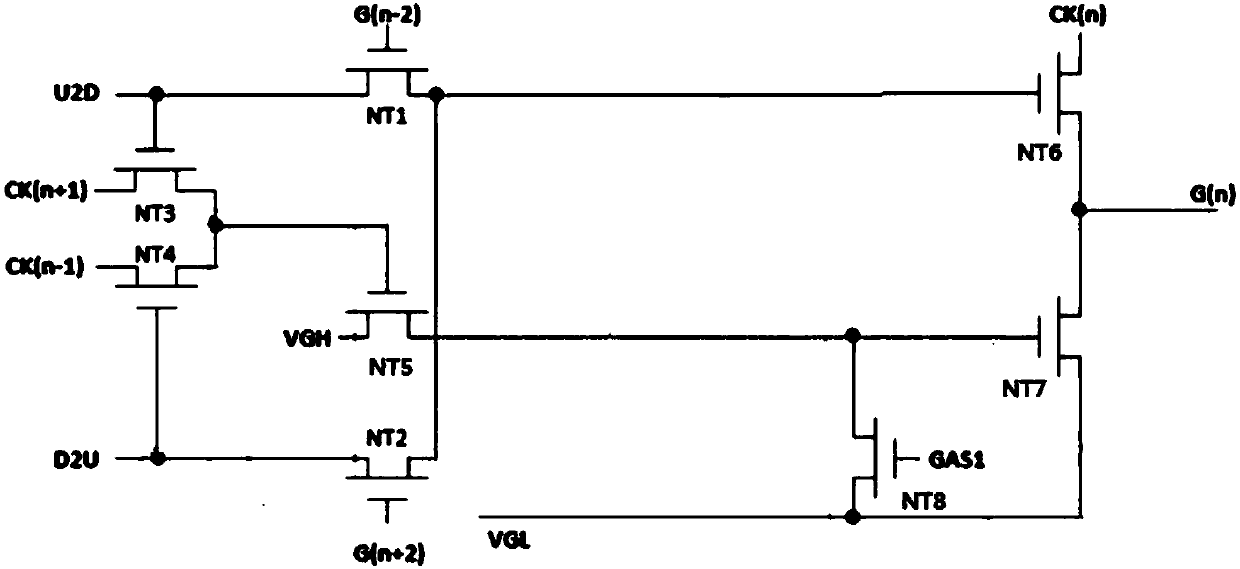

GOA circuit

InactiveCN107767833AEliminate afterimageImprove experienceStatic indicating devicesLiquid-crystal displayControl signal

The invention provides a GOA circuit including m cascaded GOA units. The n-th GOA unit includes: an output control module, a forward and reverse scan control module, a first pull-down circuit, a second pull-down circuit, and a pull-up circuit. The forward and reverse scan control module controls the GOA circuit to perform forward scanning or reverse scanning. The output control module controls theoutputting of the n-th gate drive signal. The first pull-down circuit includes a seventh TFT. The second pull-down circuit includes a third TFT, a fourth TFT, and a fifth TFT. The pull-up circuit includes an eighth TFT and a thirteenth TFT. After a liquid crystal display panel is powered off, the superimposed signal of the forward scan control signal and the reverse scan control signal switches off the fifth TFT and a first global control signal is a high-level signal. The GOA circuit can eliminate a residual image appearing during the abnormal power-off of the liquid crystal display panel and improves the user experience.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

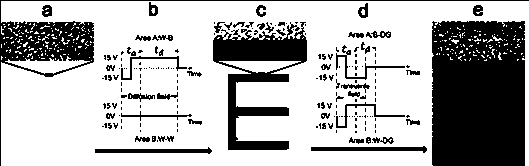

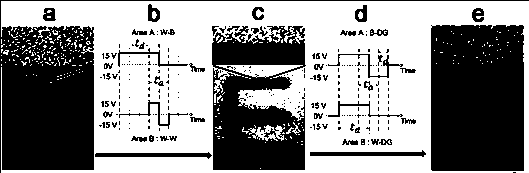

Method for eliminating edge ghost of electrophoretic electronic paper

ActiveCN108962153AEven by forceEvenly distributedStatic indicating devicesElectrophoresisElectronic paper

The invention discloses a method for eliminating edge ghost of electrophoretic electronic paper, which comprises the steps of (1) defining an area used for displaying an image on an electronic paper display screen as an area A, and further defining an area used for serving as the image background of the electronic paper display screen as an area B; (2) applying voltage for activating the image tothe area A and the area B; and (3) applying voltage for erasing the image and generating dark gray background to the area A and the area B. The method realizes optimization for the driving voltage waveform through applying different voltage, and enables particles to be stressed in a balanced manner in a dispersant of a microcapsule, thereby ensuring the particles to be uniformly distributed, and successfully eliminating the edge ghost of the electronic paper without changing the equipment structure and materials.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA ZHONGSHAN INST +1

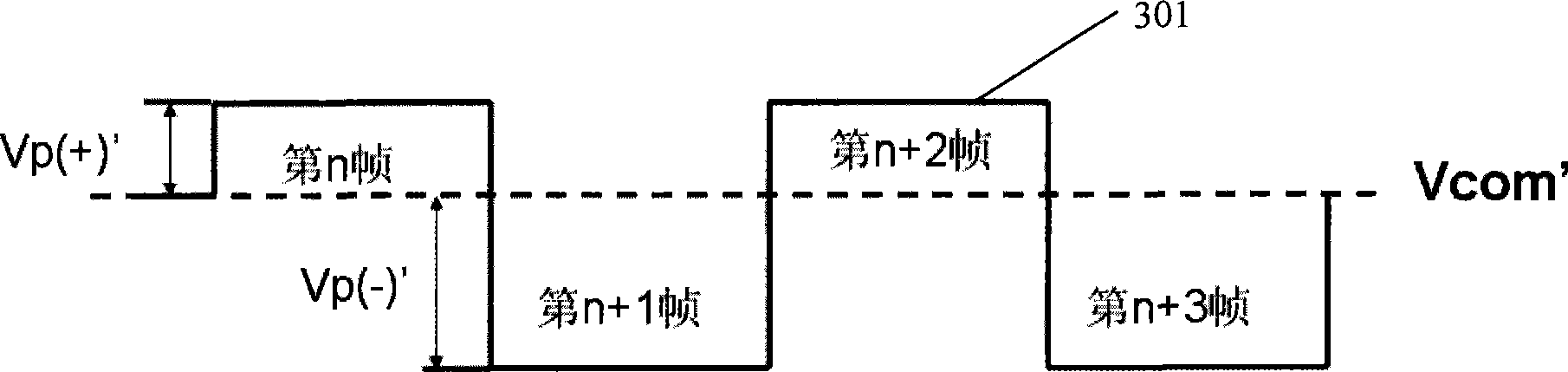

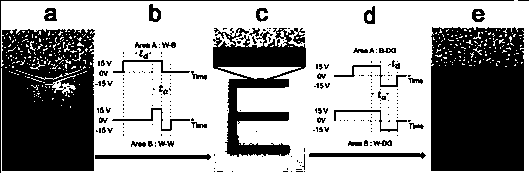

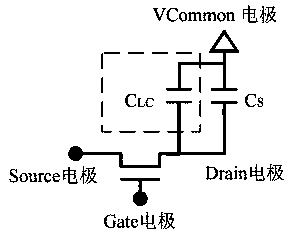

Driving method for removing residual images of LCD display screen, LCD display screen and storage medium

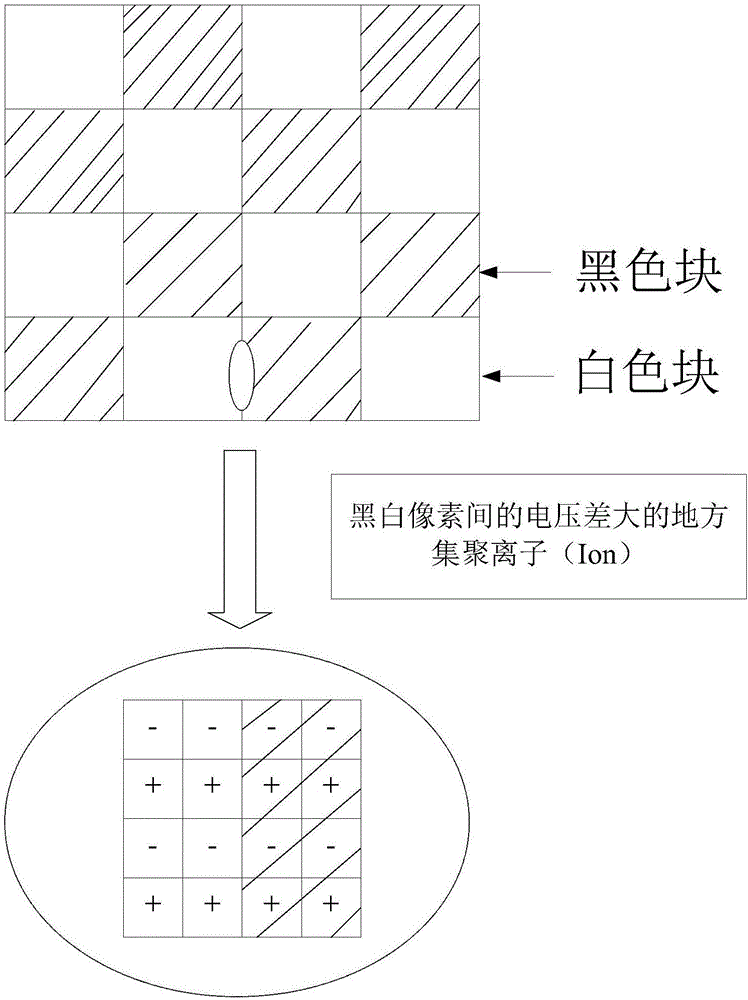

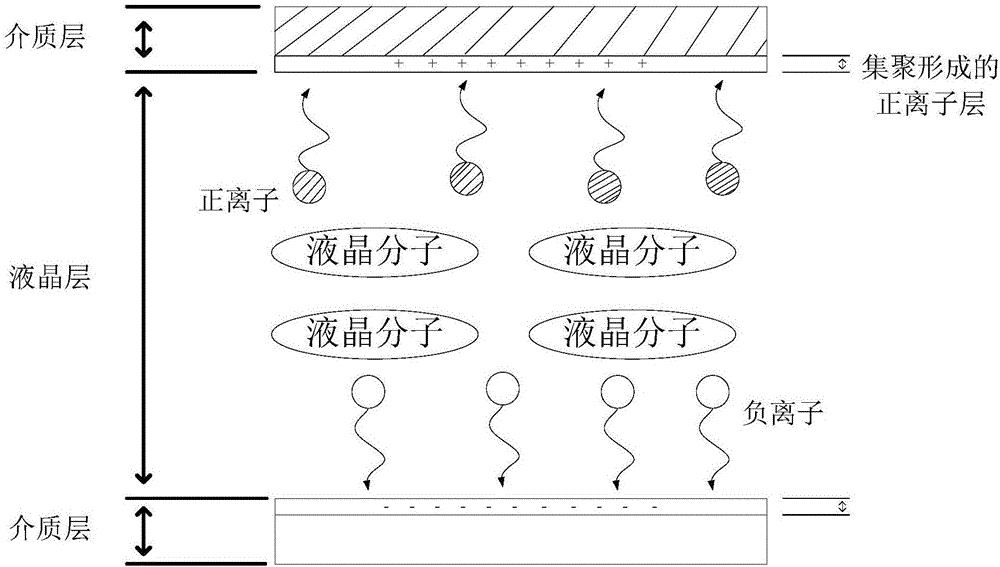

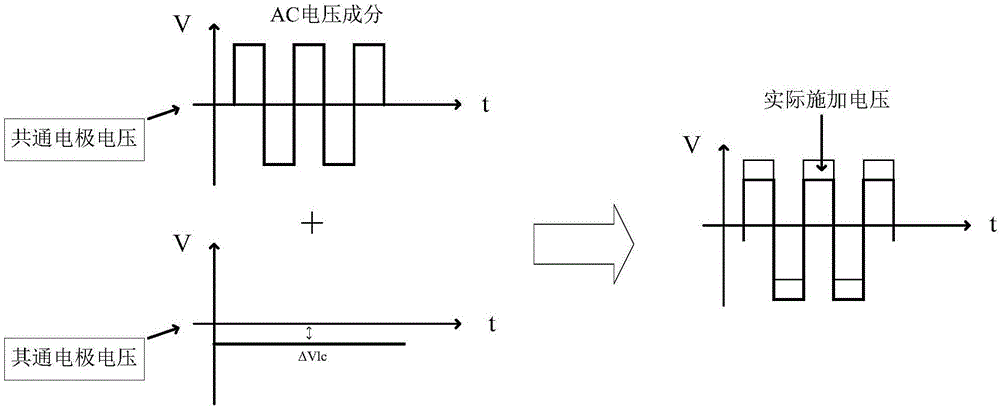

ActiveCN109509458ALow failure rateEliminate afterimageStatic indicating devicesFailure rateLiquid crystal

The invention discloses a driving method for removing residual images of an LCD display screen, the LCD display screen and a storage medium. The method comprises the steps of obtaining theoretical optimal driving voltage of liquid crystal pixels of the LCD display screen and corrected optimal driving voltage which actually drives the liquid crystal pixels of the LCD display screen; according to the theoretical optimal driving voltage and the corrected optimal driving voltage, obtaining debugging voltage for adjusting standard optimal driving voltage (Vcom) to the theoretical optimal driving voltage (V); according to the corrected optimal driving voltage and the debugging voltage, determining the highest amplitude and lowest amplitude of actual driving voltage; according to the highest amplitude and lowest amplitude of the actual driving voltage, determining the waveform of the actual driving voltage and driving the LCD display screen under the actual driving voltage. By dynamically adjusting the Vcom value before and after a thin film transistor is turned on / off, positive and negative residual image influences generated on liquid crystals can counteract each other, so that generation of polarization is avoided, the residual images are removed, the failure rate of the residual images on the LCD display screen is decreased, and the service life is prolonged.

Owner:SHENZHEN SPROCOMM TECH CO LTD

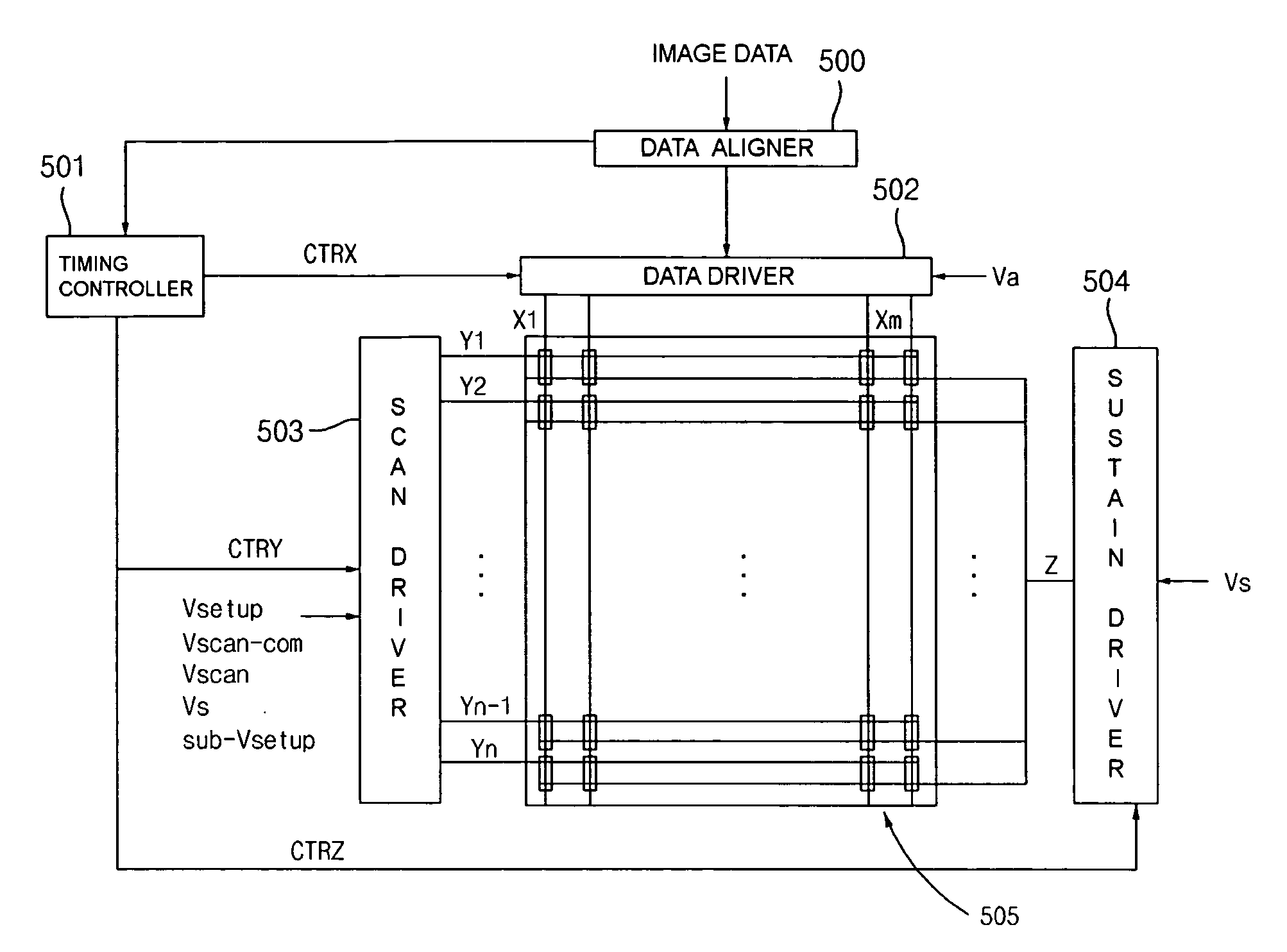

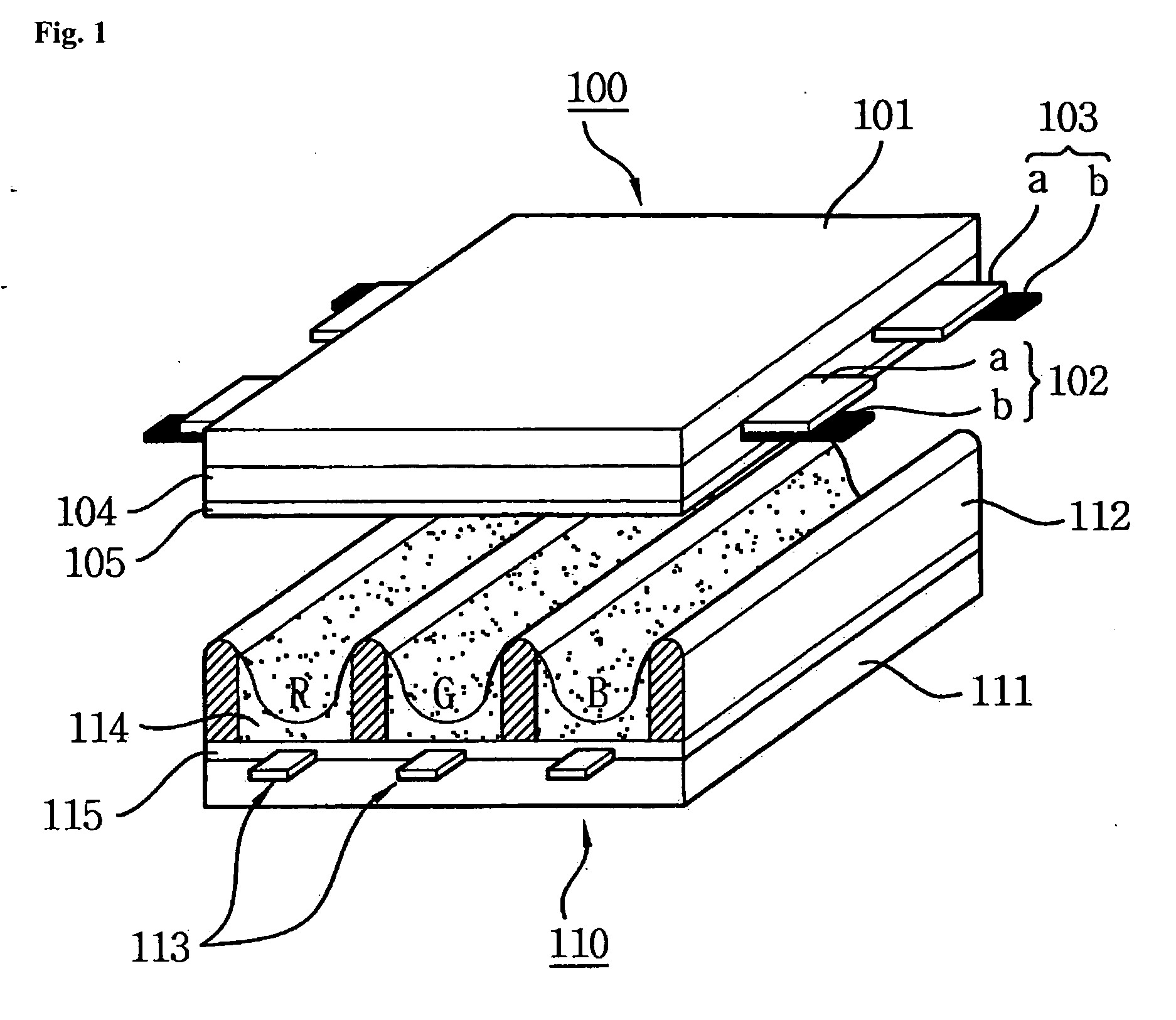

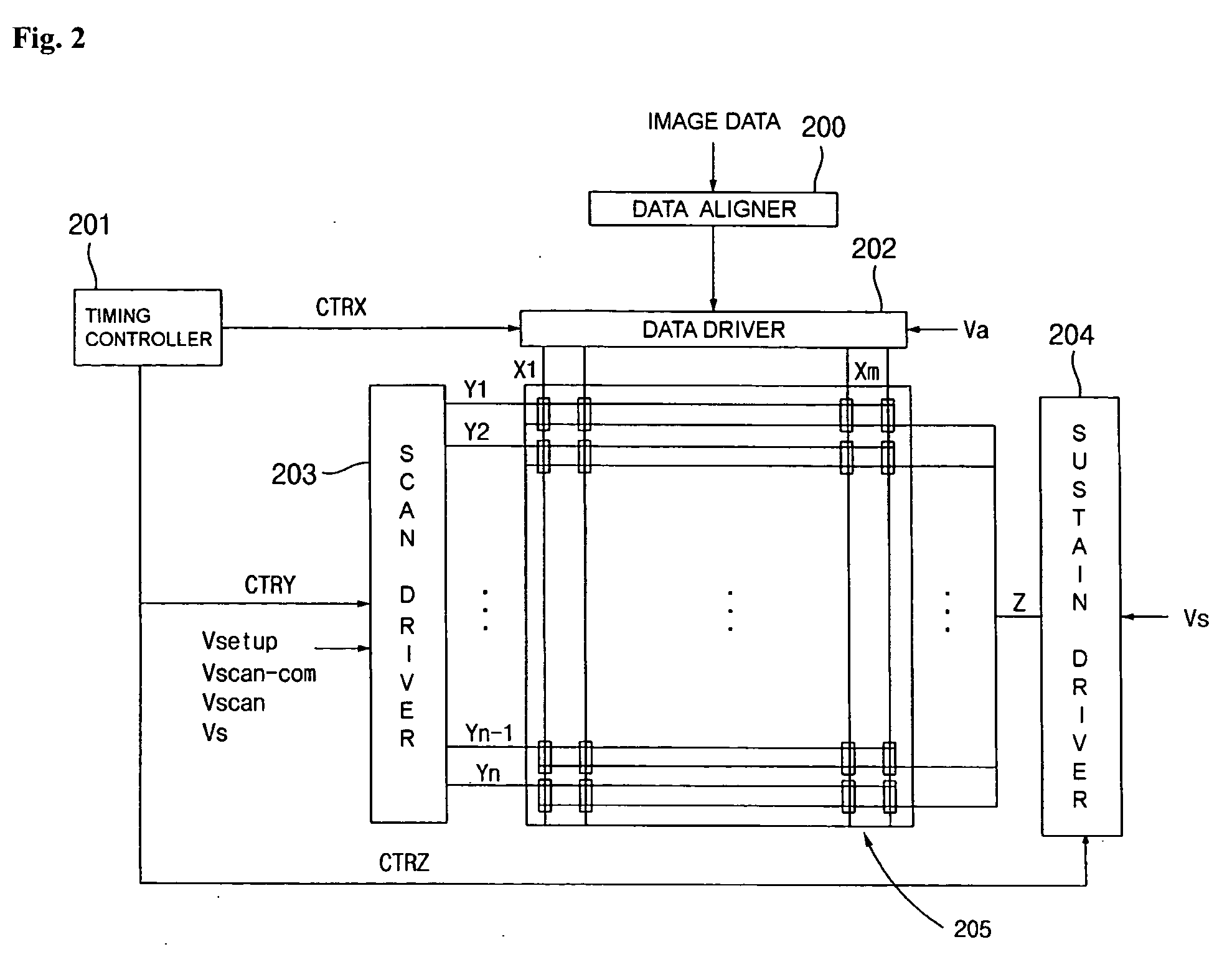

Plasma display apparatus and driving method thereof

InactiveUS20060139247A1Display of display panel is improvedEliminate afterimageStatic indicating devicesEngineeringAfterimage

The present invention relates to a plasma display apparatus and driving method thereof, in which an afterimage occurring when the plasma display panel is turned on can be obviated and an erroneous discharge phenomenon and damage to elements can be prevented. A plasma display apparatus according to an aspect of the present invention comprises a plasma display panel including a scan electrode and a sustain electrode, and a controller for applying a sustain pulse, which is the first applied pulse, to the scan electrode and the sustain electrode for a predetermined time after the plasma display panel is turned on. The present invention is advantageous in that it can obviate an afterimage occurring when a plasma display panel is turned on and can prevent an erroneous discharge phenomenon and damage to elements by improving a driving apparatus of the plasma display panel.

Owner:LG ELECTRONICS INC +1

Device and method for afterimage elimination and self-maintenance of medical display

InactiveCN106297705AEliminate afterimage phenomenonSelf-careStatic indicating devicesSelf maintenanceDisplay device

The invention aims at the problem of afterimages of the traditional medical display in the aspect of static image display and the insufficiency in lacking of self-maintenance and maintenance measures for the display to provide a device and a method for afterimage elimination and self-maintenance of a medical display so as to eliminate the afterimages of the medical display and carry out self-maintenance for the medical display regularly. The value of the invention is to provide a practical and feasible solution for eliminating and preventing the afterimages of the medical display, and carrying out the self-maintenance for the medical display, thereby improving the picture display quality of the medical display, prolonging the service life of the medical display and helping a doctor to improve the diagnosis efficiency and accuracy on patient lesions.

Owner:NANJING JUSHA DISPLAY TECH

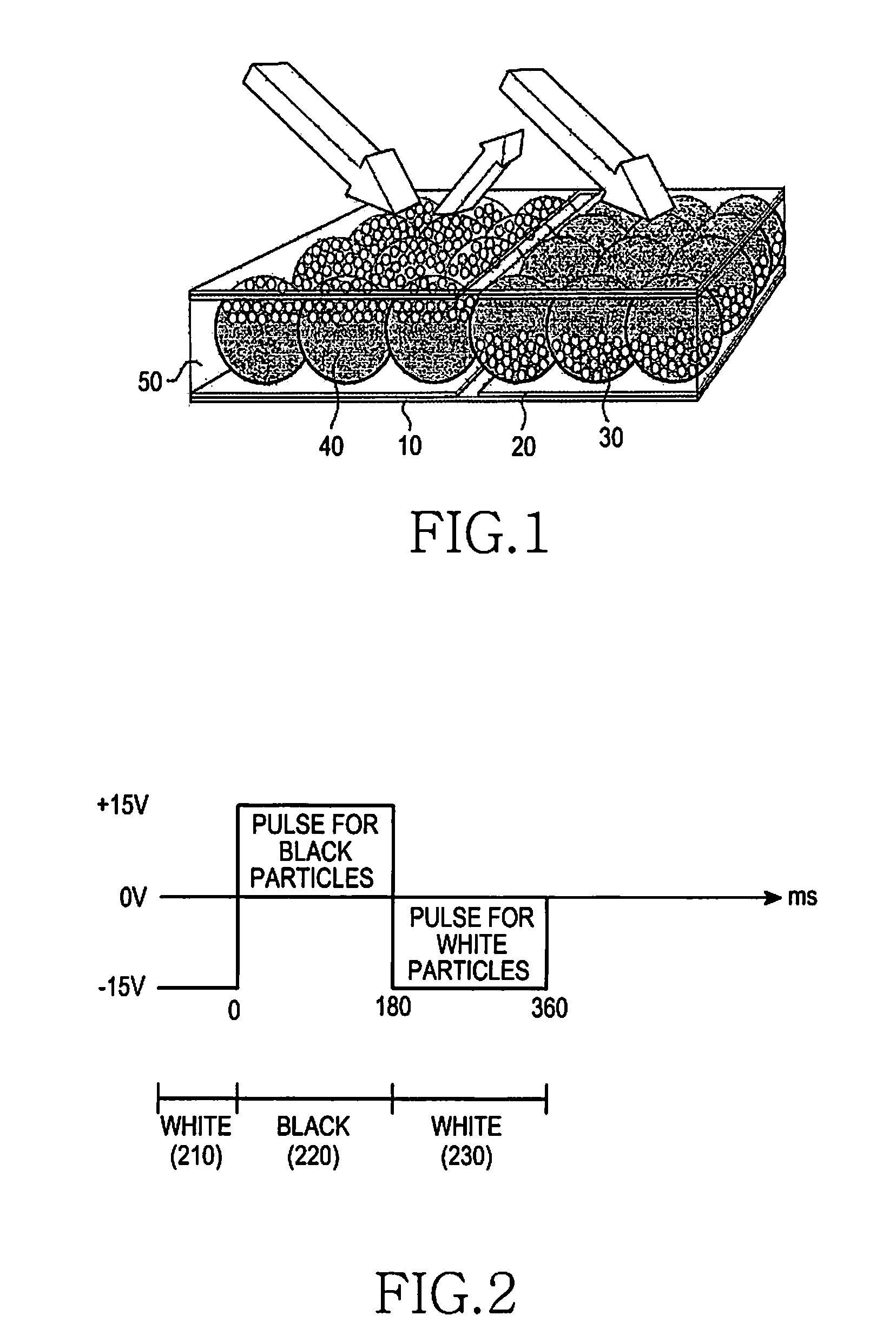

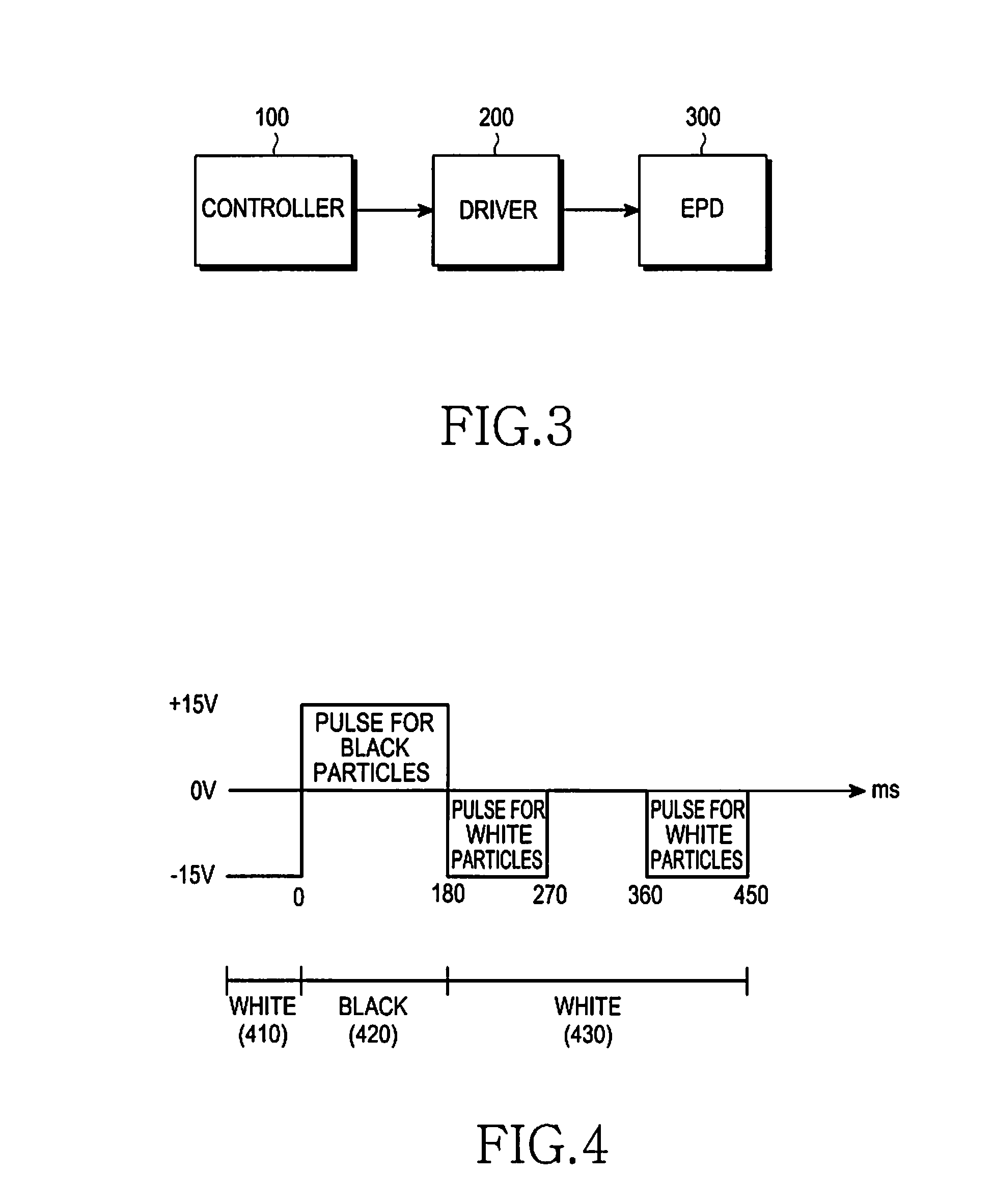

Method and apparatus for driving electrophoretic display

InactiveUS20110157136A1Eliminate afterimageCathode-ray tube indicatorsInput/output processes for data processingVoltage pulseElectrical and Electronics engineering

A method and apparatus for driving an Electrophoretic Display (EPD) where the apparatus includes a controller for controlling an overall operation of the apparatus for driving the EPD, determining data to be displayed on the EPD, and outputting a drive signal; a driver for generating a driving voltage pulse for moving black particles and white particles to display the data on the EPD according to the drive signal output from the controller, thereby controlling the EPD; and the EPD for displaying a representation of the data in white or black according to the driving voltage pulse, wherein the driver generates the driving voltage pulse for moving the black particles or the white particles in such a manner that the driving pulse is divided into a predetermined number of subpulses, and an idle period during which a voltage is not applied intervenes between the respective divided subpulses.

Owner:SAMSUNG ELECTRONICS CO LTD

Liquid crystal display device, method for controlling the same, and portable terminal

InactiveUS20070290968A1Eliminate afterimagePrevent stateCathode-ray tube indicatorsInput/output processes for data processingActive-matrix liquid-crystal displayLiquid-crystal display

An active-matrix liquid crystal display device has pixels arranged in a matrix which each include a thin film transistor (TFT) as an active element. When the device is in a power-off state, TFTs in all the pixels are switched on, and all horizontal switches are turned on so that all data lines are supplied with a potential equal to the potential of common electrodes of the pixels. This forms a discharging path for discharging residual charge in all the pixels, and the discharging path can instantaneously discharge the residual charges.

Owner:JAPAN DISPLAY WEST

Solid picture element manufacturing method

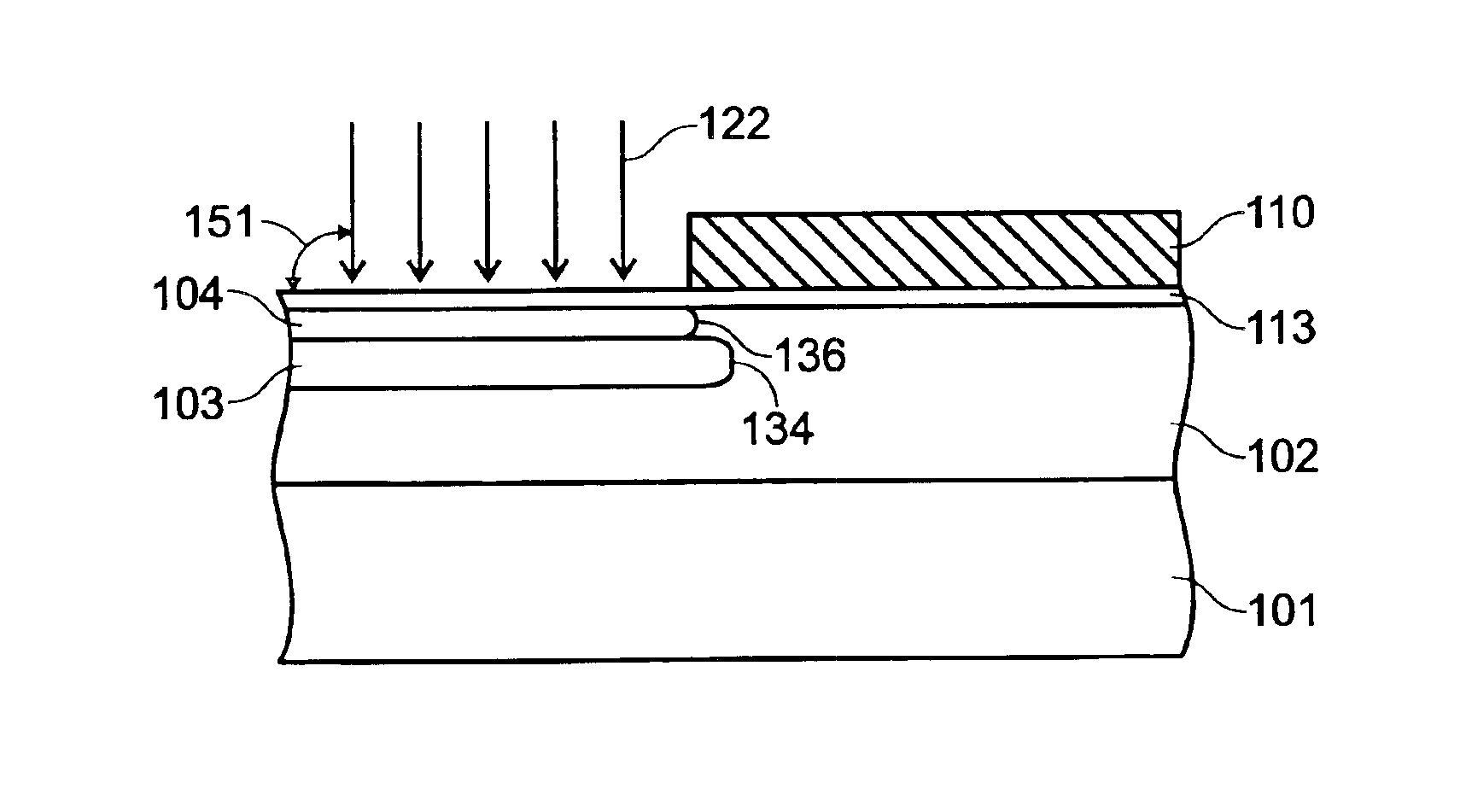

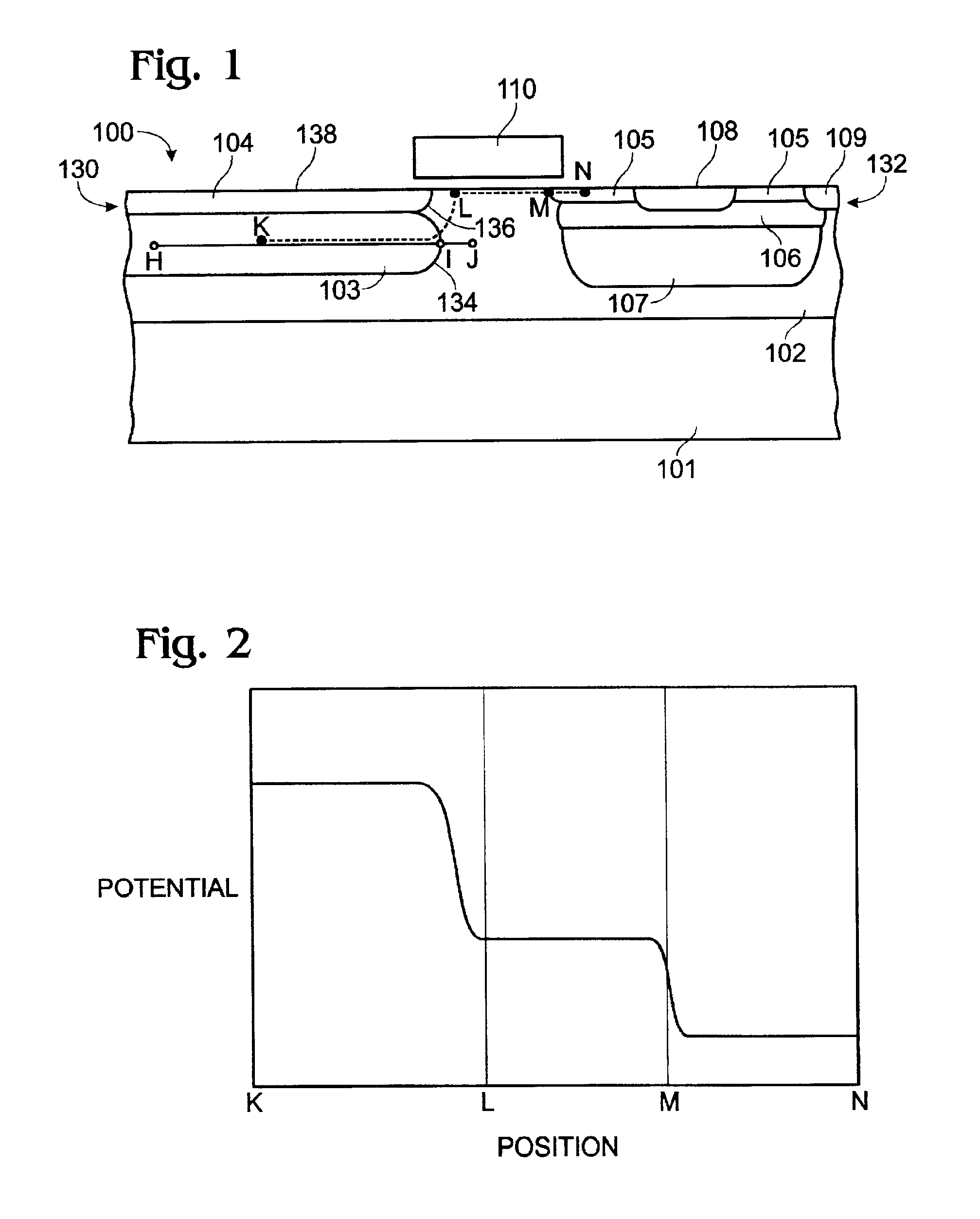

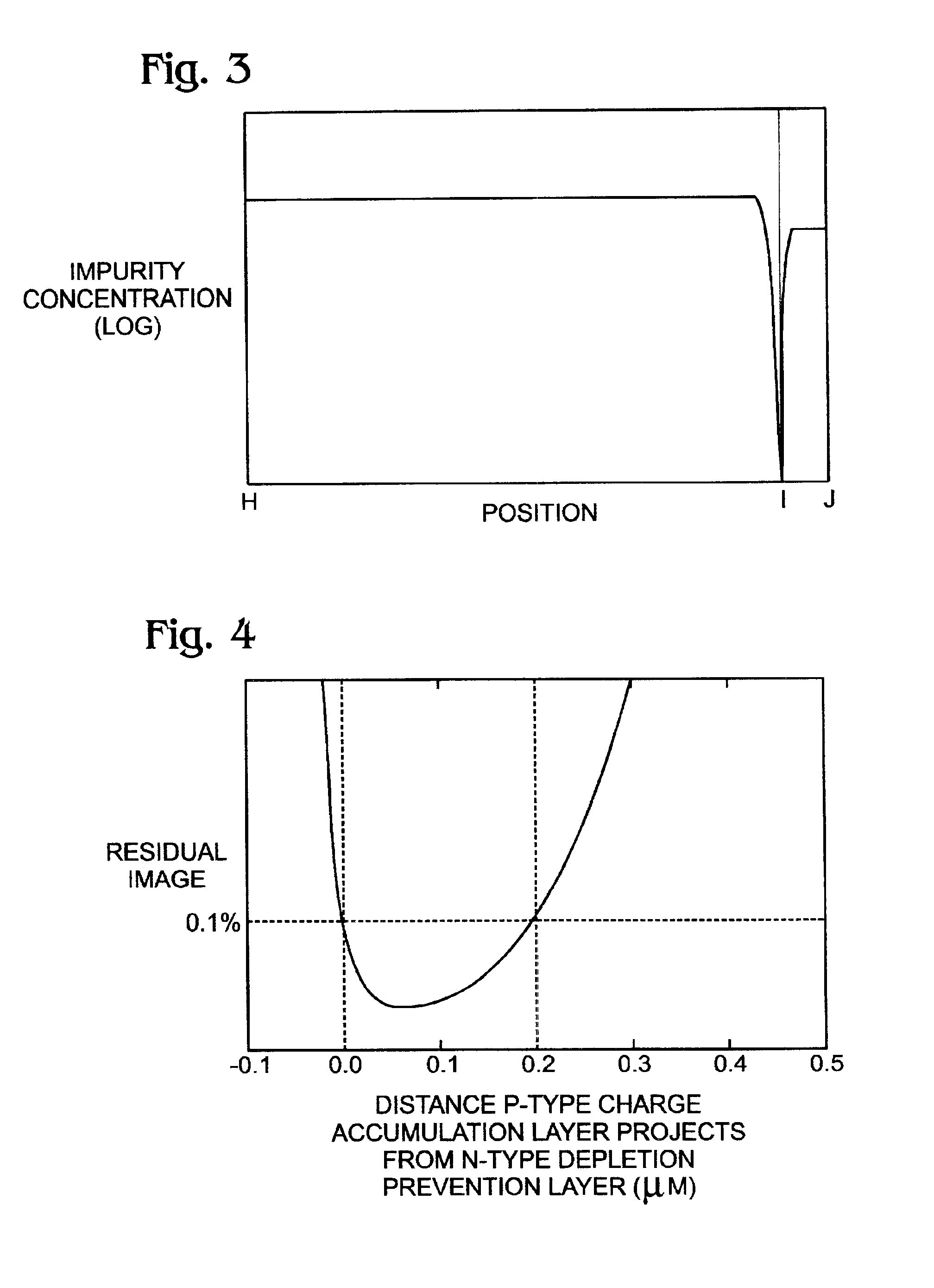

InactiveUS7186595B2Residual image can be substantially eliminatedEasy to controlTelevision system detailsSolid-state devicesEngineeringAlternative methods

A solid picture element that transfers charges completely from a photodiode portion to an amplifying transistor portion to substantially eliminate residual images and methods of its manufacture are disclosed. The solid picture element includes a buried photodiode and a transistor in communication with a transfer gate that is a selective transfer path for charges from the photodiode to the transistor. The charge accumulation region is located so that it is not in contact with the upper surface of the semiconductor substrate and so that a margin of the charge accumulation region is located 0.0 to 0.2 μm closer to the transistor than any portion of the depletion prevention region. Methods of manufacture of the picture element of the present invention include using the transfer gate as a mask and implanting ions into a semiconductor substrate at a first angle to form the charge accumulation region and at a second, steeper, angle to form the depletion prevention region. Alternative methods of manufacture include sifting a portion of a mask to sift end margins of the charge accumulation region and the depletion prevention region to achieve the desired geometry.

Owner:NIKON CORP