Systems and methods for dynamic low latency optimization

A low-latency, user-space technology, applied in multi-program devices, program control design, instruments, etc., can solve problems such as blocking understanding, inability to return, user space low-latency technology is not optimized, etc., to achieve low-latency optimization Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

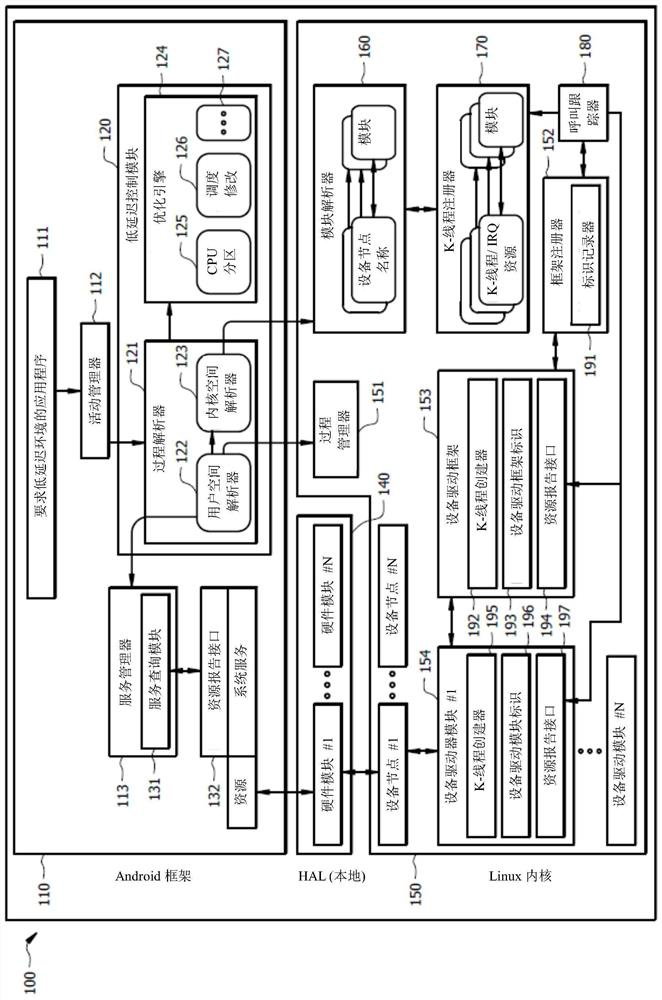

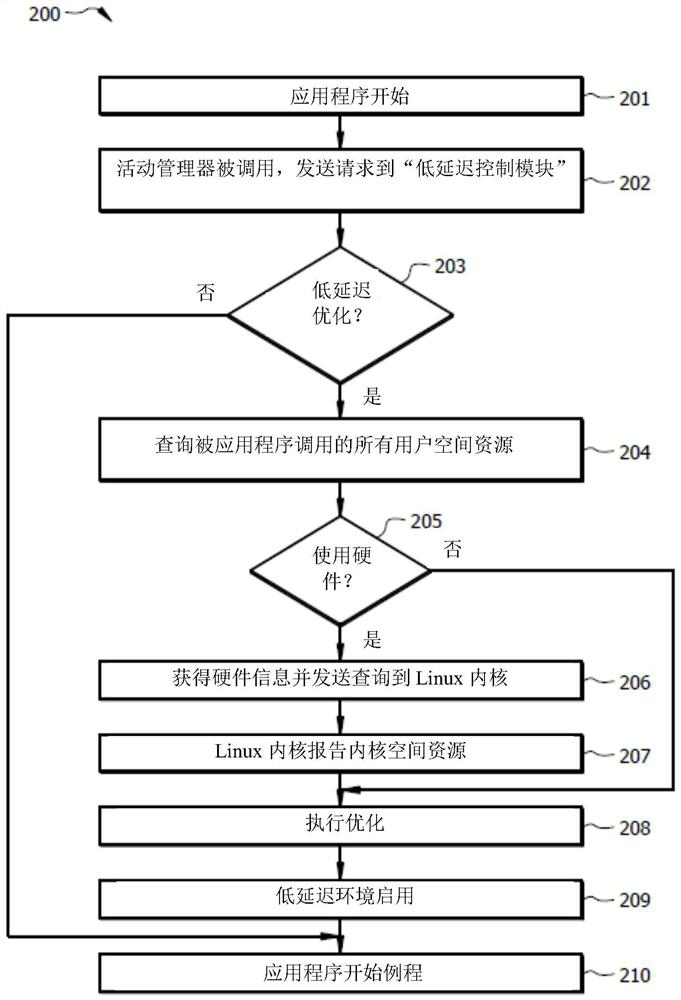

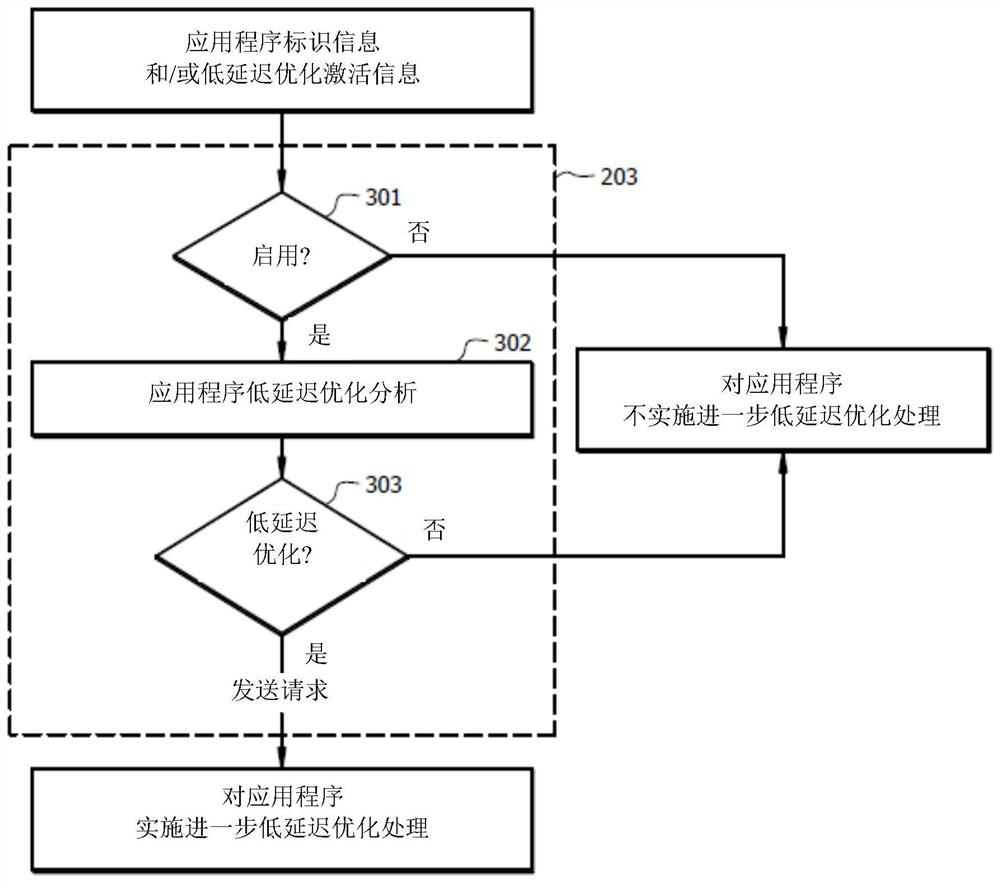

[0023] figure 1 A low-latency optimized implementation of an embodiment is shown that includes a multi-part configuration for obtaining information about services and hardware used by an application and utilizing this information to provide dynamic implementation low-latency operation. specifically, figure 1 One embodiment is shown of a processor-based system 100 (eg, a smartphone or other device with limited processing and / or other capabilities) configured to optimize low-latency execution of certain applications. figure 1 The low-latency optimized implementation configuration of the illustrated embodiment includes modules implemented in user space (eg, the exemplary ANDROID framework of the illustrated embodiment) and kernel space (eg, the Linux kernel of the illustrated embodiment). Individual ones of the modules cooperate together to obtain information about the services and hardware used by the application and provide this information to facilitate low-latency operation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More