A multi-level flash memory unit error correction method, system, device and readable storage medium

A technology of flash memory unit and error correction method, applied in the field of flash memory, can solve the problems of LDPC error correction code error correction performance degradation, logarithm is no longer accurate, etc., to achieve the effect of ensuring reliability and error correction performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039]The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

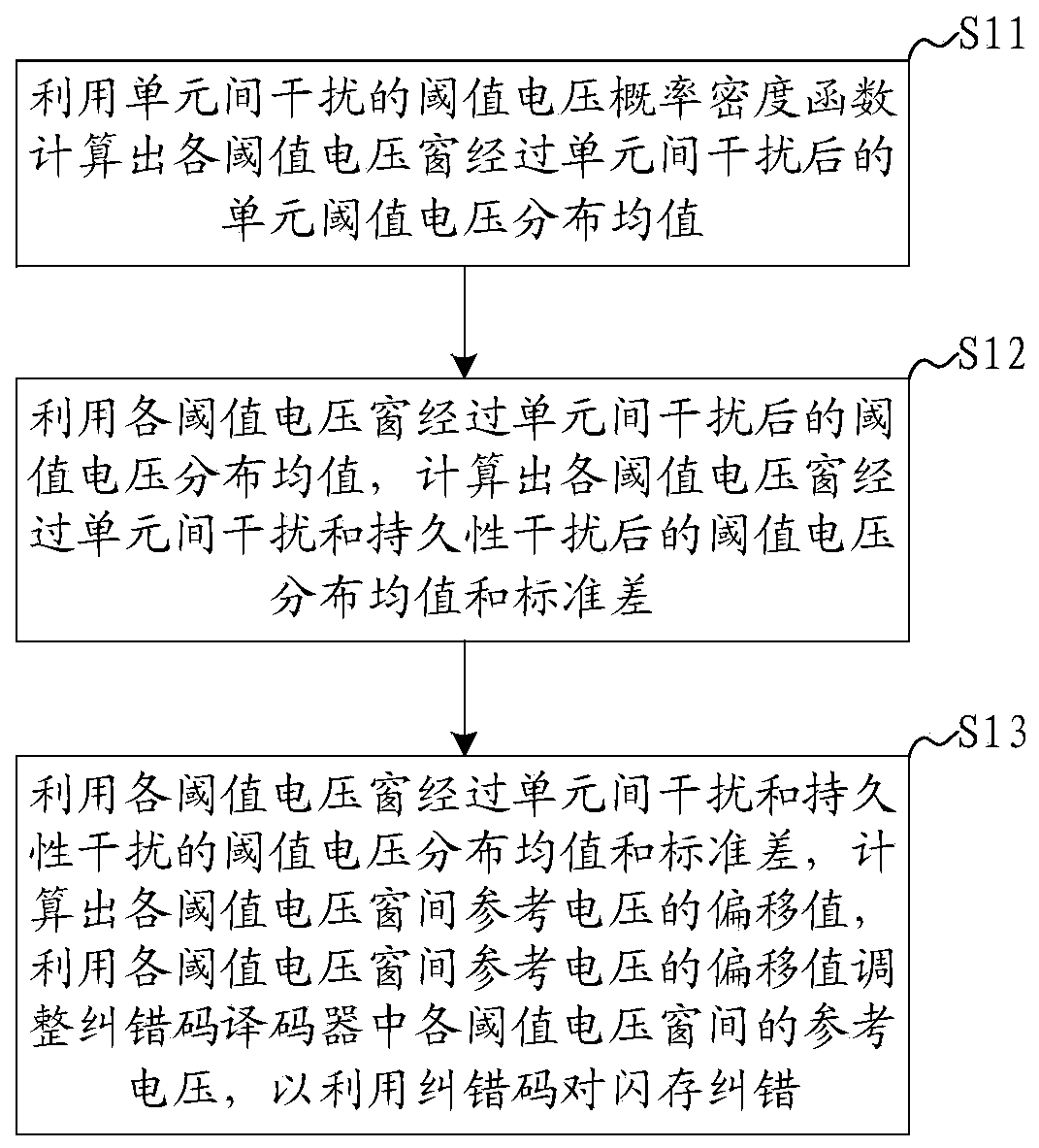

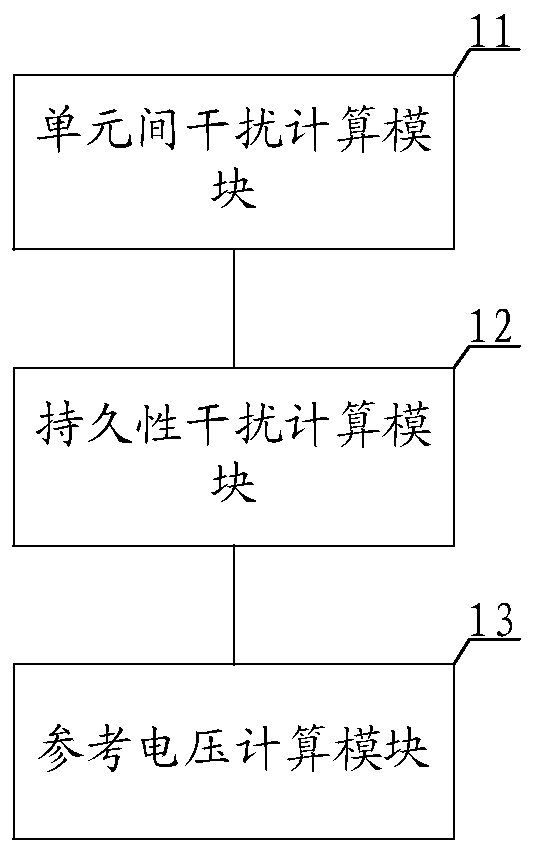

[0040] The embodiment of the present invention discloses a multi-level flash memory unit error correction method, see figure 1 As shown, the method includes:

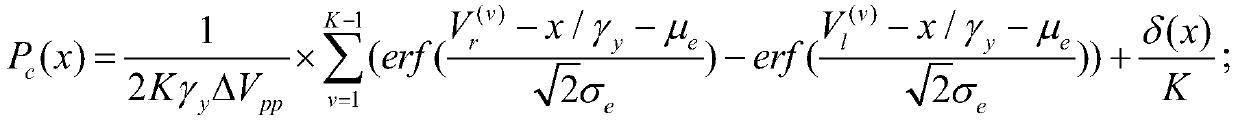

[0041] Step S11: Using the threshold voltage probability density function of inter-unit interference to calculate the average value of the threshold voltage distribution of each threshold voltage window after the inter-unit interference.

[0042] It can be understood that flash memory is composed of mul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More