Multi-chip framework package structure and manufacturing method thereof

A packaging structure and multi-chip technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of limiting feasibility and restricting packaging density, so as to solve the limited number of chips and increase the number , the effect of meeting the diverse needs of packaging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

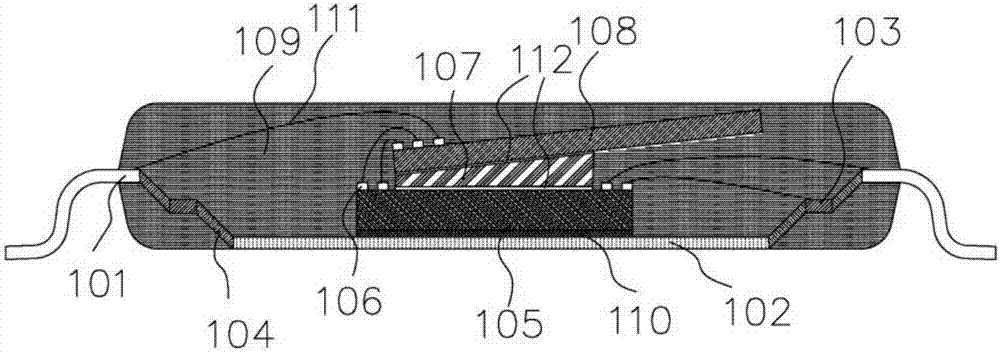

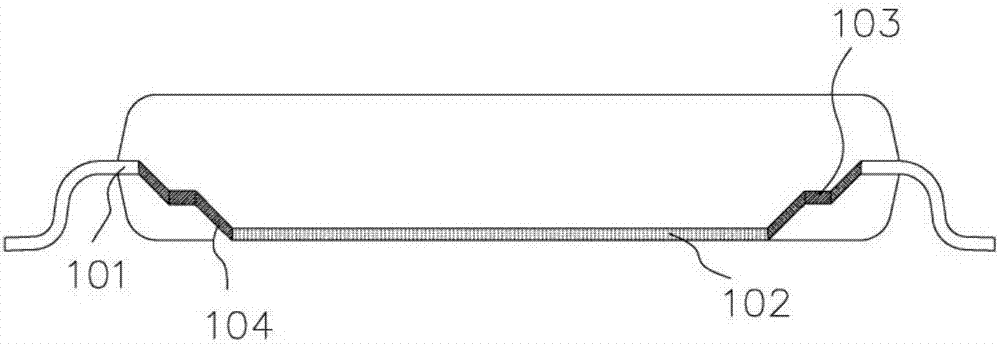

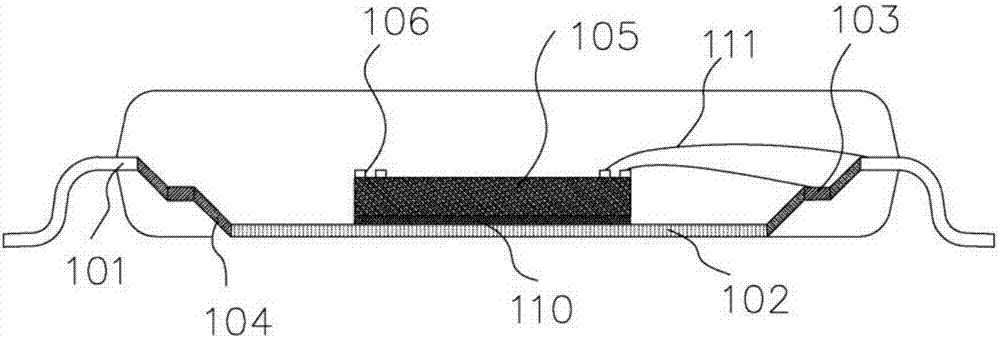

[0038] This embodiment provides a multi-chip frame packaging structure; the multi-chip frame packaging structure described in this embodiment can effectively increase the number of chips packaged in a frame SIP package, which meets the needs of packaging diversification, and effectively solves the existing SiP frame packaging structure for the problem of the limited number of chips in multi-chip packaging; specifically, the multi-chip frame packaging structure includes: at least one chip carrier, at least one bottom chip and at least one upper chip; the at least one carrier The chip platform is used to accommodate the at least one bottom chip and the at least one upper chip; the packaging structure also includes: at least one first dielectric layer; wherein, the first dielectric layer is placed above the bottom chip The upper chip is placed above the first dielectric layer; the positional relationship between the bottom chip and the upper chip can be adjusted by adjusting the i...

Embodiment 2

[0059] This embodiment provides a method for manufacturing the multi-chip frame package structure described in Embodiment 1; specifically, the method includes:

[0060] The bottom chip is set on the at least one loading stage; the first dielectric layer is set on the bottom chip, and the first dielectric layer is placed above the bottom chip; The upper chip is arranged above the dielectric layer, and the above upper chip is placed above the first dielectric layer; wherein, the bottom chip and the upper chip can be adjusted by adjusting the inclination angle of the first dielectric layer The positional relationship among them, so as to increase the number of chips stacked on the at least one loading stage.

[0061] In a specific embodiment, the packaging structure further includes: at least one second dielectric layer; correspondingly, the method further includes: disposing the second dielectric layer above the first upper layer chip in the at least one upper layer chip A diel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More