FPGA-based method and system for measuring add-carry chain delay

An addition and carry chain and measurement method technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve problems such as lack of accuracy, inability to respond to delay time differences, real-time adjustment of working voltage, etc., and achieve accurate results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

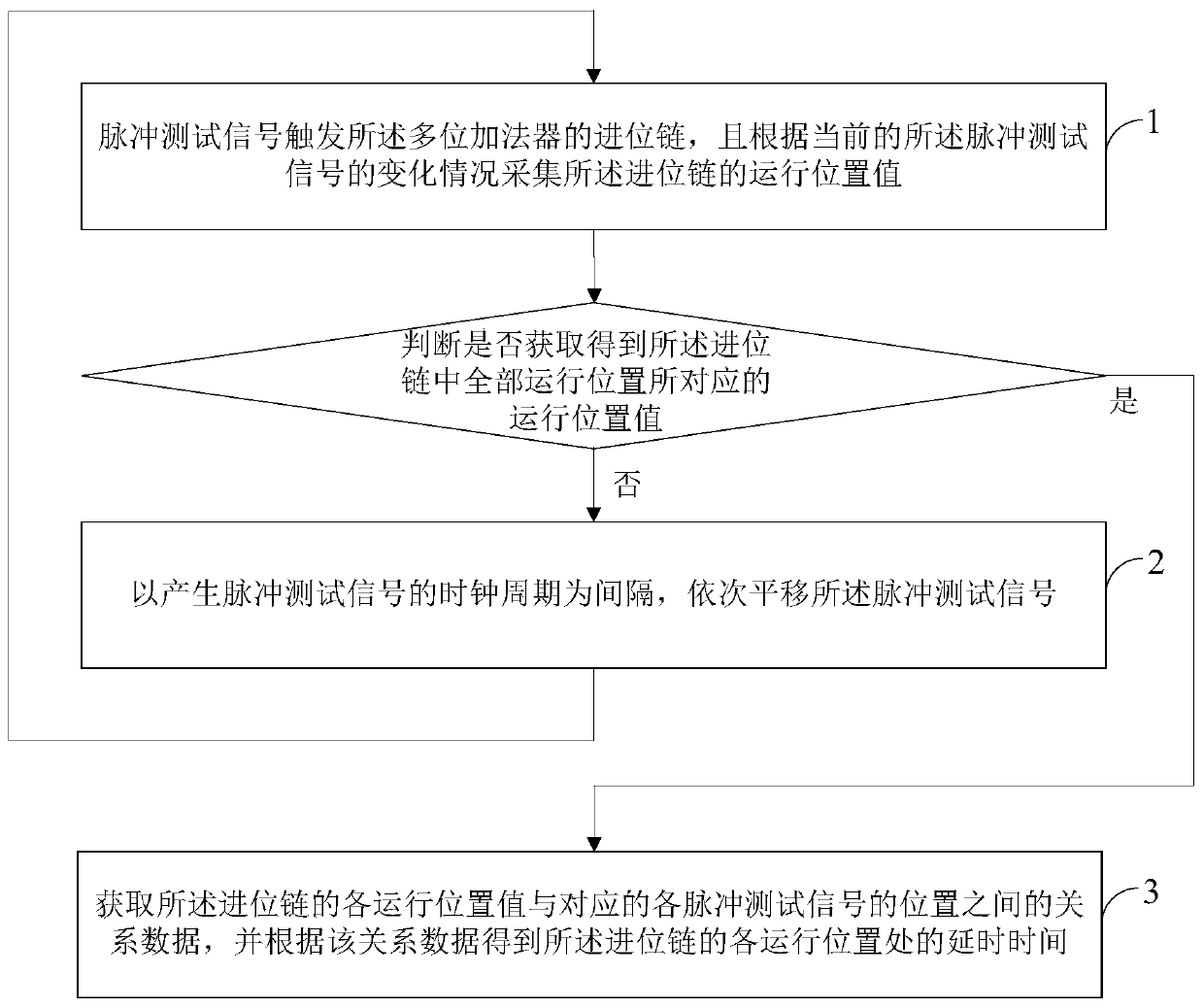

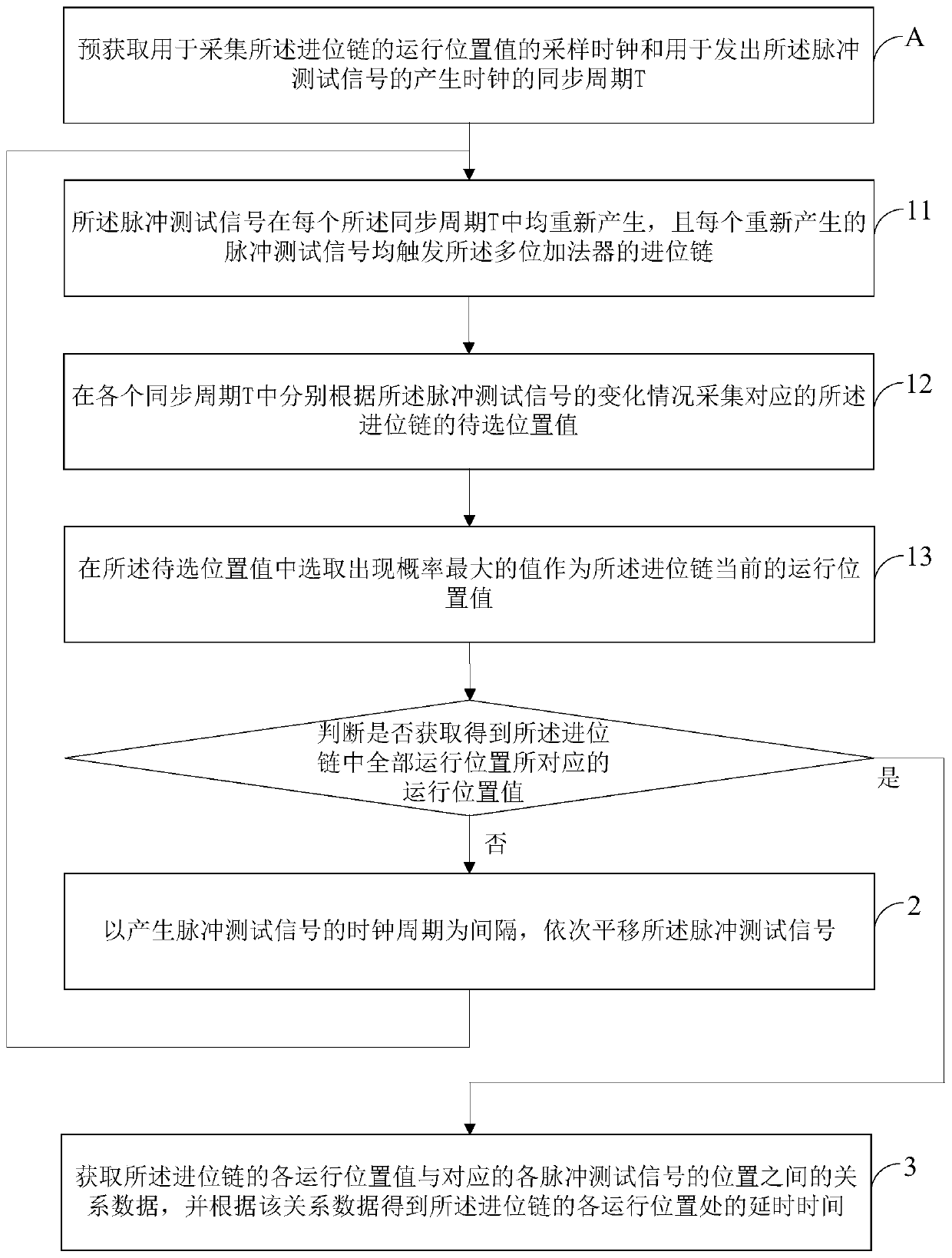

[0058] Embodiment 1 of the present invention provides the first specific implementation of a method for measuring the delay of the addition and carry chain based on FPGA, see figure 1 , the measurement method of the delay of the addition carry chain based on FPGA is used to measure the delay of the addition carry chain in the idle time that the multi-bit adder in the FPGA carries out actual timing measurement, and the measurement method specifically includes as follows content:

[0059] Step 1: The pulse test signal triggers the carry chain of the multi-bit adder, and collects the running position value of the carry chain according to the current change of the pulse test signal.

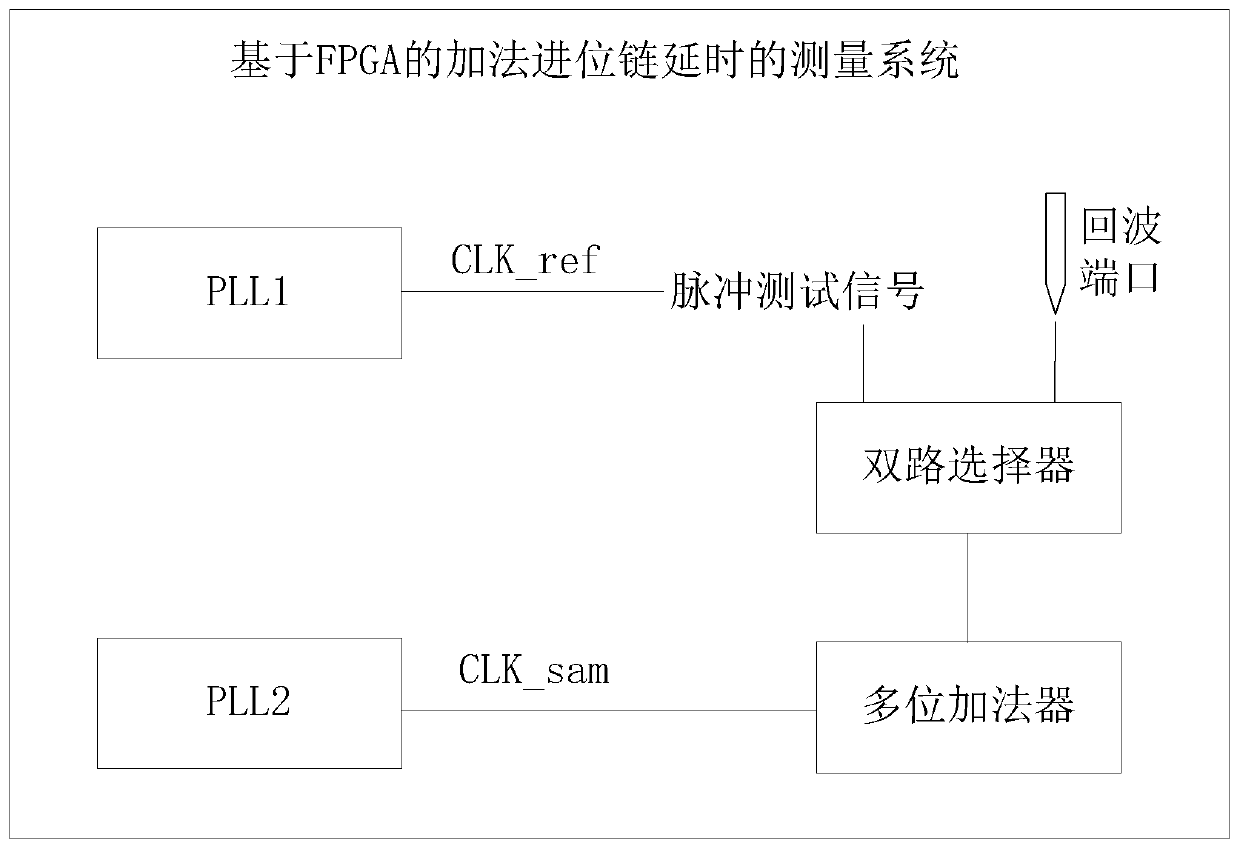

[0060] In step 1, the measurement method of the delay of the addition carry chain based on FPGA can be realized by applying a measurement system of the delay of addition carry chain based on FPGA, and the measurement system specifically includes: the reference clock CLK_ref in the FPGA , sampling cl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More