A three-dimensional on-chip routing device based on recalculation and a method thereof

A recalculation, three-dimensional technology, applied in the field of recalculation-based three-dimensional on-chip routing devices, can solve the problems of occupying data packet header space, resource waste, increasing transmission delay and data packet diversion times, etc., to reduce transmission delay and avoid Effects of wrong turns, reduced number of diverted transfers, and detoured transfers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other.

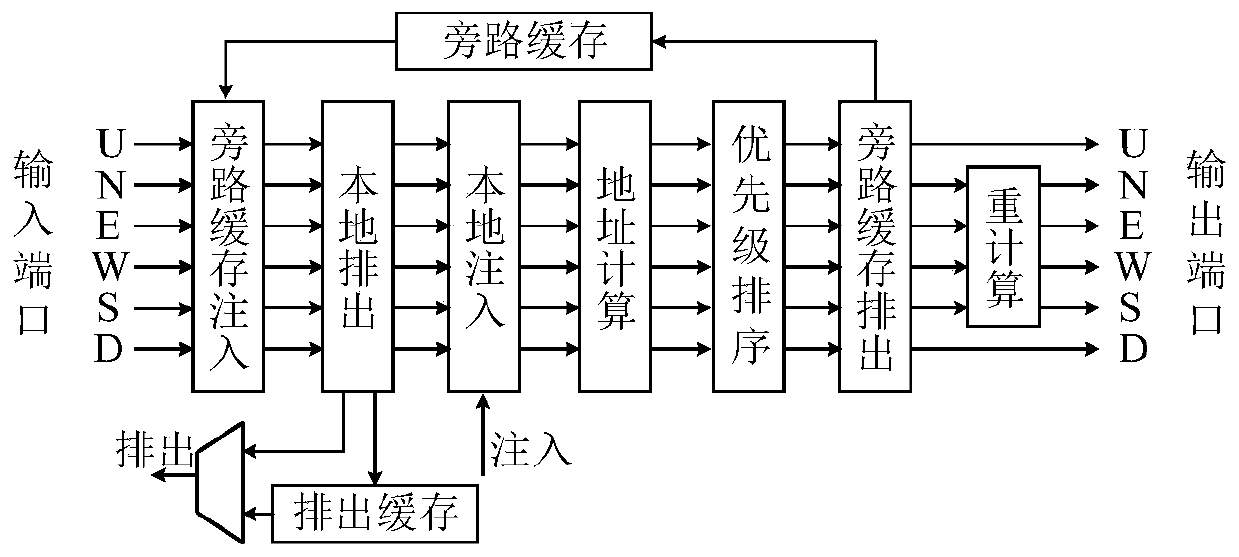

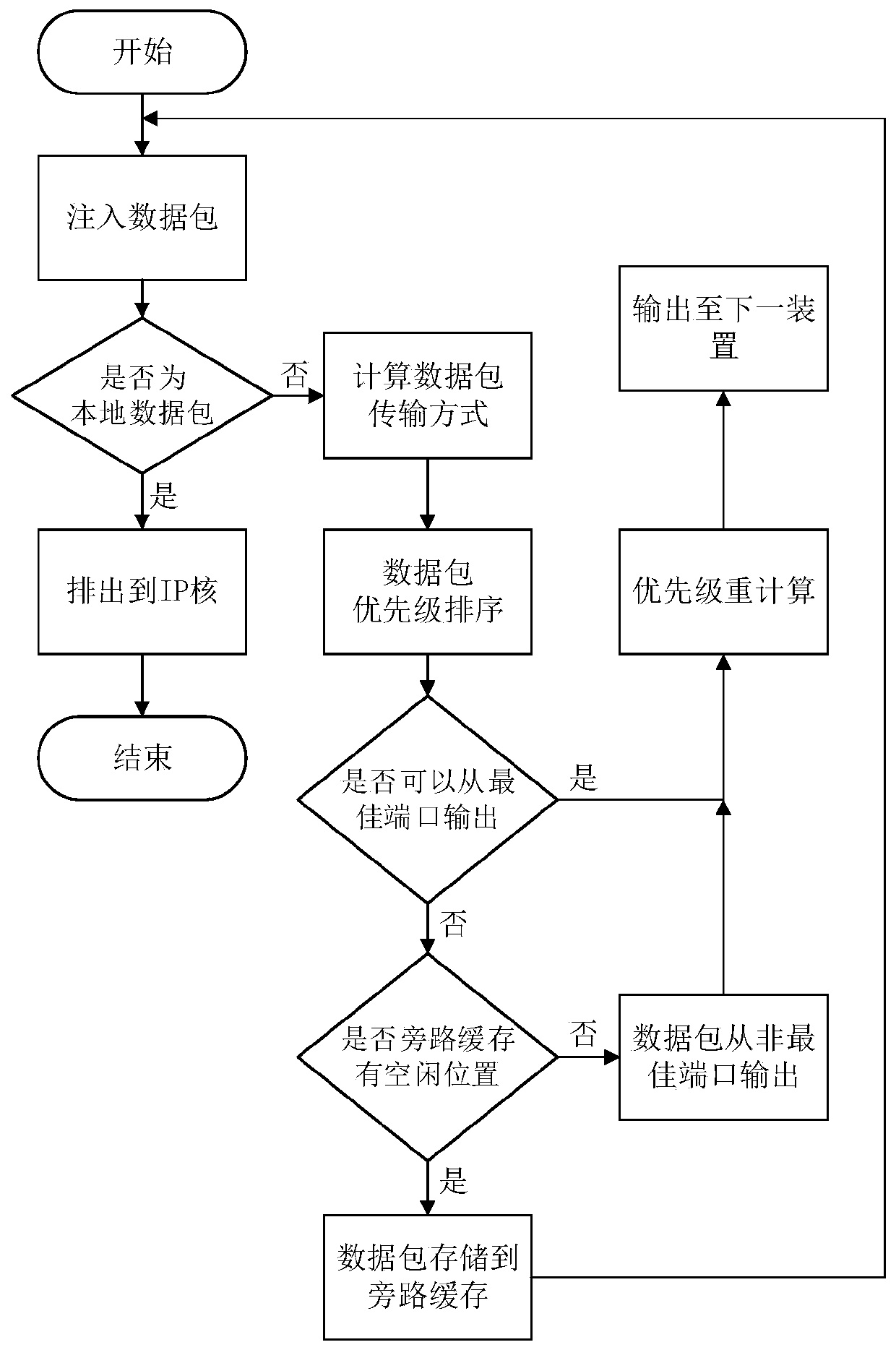

[0039] figure 1 It is a diagram showing a three-dimensional on-chip routing device based on recomputation according to an embodiment. The device mainly includes an injection unit, a discharge unit, a calculation unit, a buffer unit, a priority sorting unit, etc., and is applied in the field of a three-dimensional on-chip network.

[0040]1) The bypass buffer injection unit is used to inject data packets. When a transmission channel is idle, the bypass buffer injection unit re-injects the stored data packets into the channel;

[0041] 2) The local discharge unit is used to discharge data packets. When the local port is idle, the local discharge unit discharges the local data packets from the transmission channel to the IP core. The local discharge unit introduces a discharge cache that can store a data pack...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More